基于DSP28335 的FPGA 软件在线升级方法

王涛,钱昀莹,张铆,田旭

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214062;2.中国矿业大学(北京)机械与电气工程学院,北京 100083)

数字信号处理器(Digital Signal Processor,DSP)内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,采用流水线操作,可以快速实现各种数字信号处理算法;现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)由可编程逻辑块、数字时钟管理、输入输出等模块组成,具有可编程灵活性高、开发周期短以及并行计算效率高的特点。鉴于DSP 和FPGA 的上述优点,DSP+FPGA 架构的实时信号处理系统已广泛应用于网络通信、数据中心、汽车电子、人工智能等领域[1-2]。

在DSP 和FPGA 软件调试过程中,可以通过JTAG 接口将应用程序烧写至相应的FLASH 或PROM中。然而,当产品使用出现问题或者产品功能升级时,需要打开产品外壳,通过电路板上JTAG 接口连接仿真器才能对DSP 和FPGA 软件进行升级。由于一些产品已经交付使用或经过特殊工艺处理,不具备拆卸外壳进行软件升级的条件。目前,DSP 和FPGA 产品软件在线升级得到了广泛的研究[3-16],DSP可以通过固化在内部BOOT ROM 中的引导程序(Bootloader)选择不同的BOOT 模式,实现DSP 软件在线升级[3-4]。针对FPGA 软件在线升级[5-20],文献[5]利用USB2.0 芯片CY7C68013A 设计了一种FPGA 程序在线升级的方法;文献[6]通过1553B 总线实现了对FPGA 的在线升级;文献[7]设计并实现了基于UDP 的FPGA 远程升级系统。

然而,在DSP+FPGA 架构的嵌入式系统中利用DSP 在线升级FPGA 的方法并未见文献论述。基于此,该文提出了一种基于TMS320F28335 的FPGA 软件在线升级方法。该方法通过上位机将FPGA 代码发送给DSP,DSP 通过GPIO 模拟符合IEEE1194.1 标准的JTAG 时序,完成对配置PROM 芯片的擦除、编程和校验操作,实现FPGA 软件的在线升级。实验结果表明:该方法具有较好的可行性、稳定性和可靠性,可以实现DSP+FPGA 架构下不拆产品就可升级FPGA 软件的目的。

1 总体方案

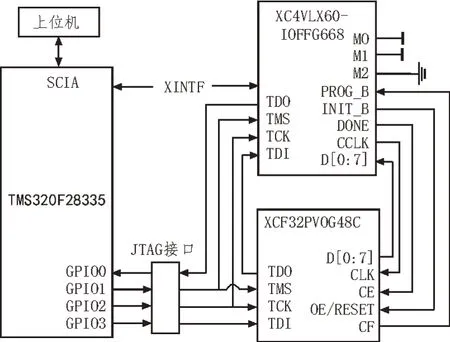

DSP+FPGA 架构下FPGA 软件在线升级原理框图如图1 所示,主要由上位机和目标产品两部分组成。上位机主要负责与DSP 通信,实现命令和数据的发送与接收。目标产品中DSP 芯片型号为TI 公司C2000 系列TMS320F28335,FPGA 芯片型号为Xilinx公司Virtex4 系列XC4VLX60-10FFG668,配置PROM芯片型号为XCF32PVOG48C。

图1 在线升级原理框图

上位机通过RS422 串口发送FPGA 软件给DSP,DSP 接收到数据后将其存放在片内SRAM 中。DSP通过GPIO 模拟标准的JTAG 时序,将SRAM 中存放的数据烧写到32P 芯片中,重复上述操作,直至FPGA 软件烧写完成。

FPGA 软件烧写完成后,上位机通过RS422 串口发送校验命令,DSP 读取32P 芯片中的数据并回传给上位机,上位机进行数据校验。若数据校验全部正确,表明FPGA 软件在线升级成功,否则重新执行在线升级过程。

2 硬件设计

DSP+FPGA 嵌入式系统硬件设计原理图如图2所示,DSP 与FPGA 通过XINTF 总线完成数据交互传输。将FPGA 的M0 和M1 管脚上拉、M2 管脚下拉,配置编程模式为主SelectMAP 模式,通过并行总线进行配置数据传输,数据宽度为8 位。JTAG 接口、FPGA和32P 采用菊花链的方式进行连接,即TMS、TCK 信号分别连在一起,JTAG 接口的TDI 信号与32P 的TDI 信号相连,32P 输出的TDO 信号作为FPGA TDI的输入,FPGA 的TDO 与JTAG 接口的TDO 相连,形成完整的回路。DSP 通过SCIA 串口与上位机进行数据收发,利用GPIO0~3 分别模拟JTAG 接口的TDO、TMS、TCK 和TDI 信号。

图2 硬件原理图

3 软件实现

3.1 升级流程

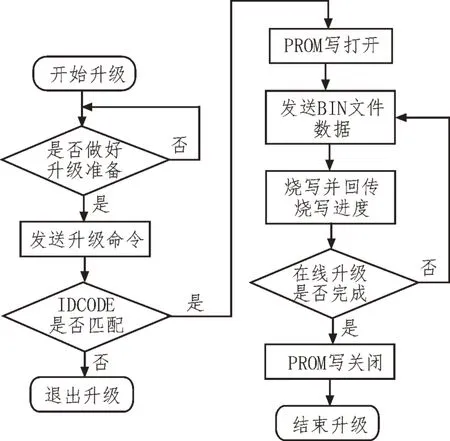

在线升级软件包括上位机软件和DSP 升级软件,在线升级软件总体工作流程如图3 所示。

图3 升级流程图

首先,打开上位机软件,设置串口号和串口波特率并打开串口,加载FPGA 待烧写的BIN 格式软件。上位机通过RS422 串口给DSP 发送升级命令,DSP读取32P 芯片的IDCODE,若IDCODE 不匹配,则退出在线升级;若读取的IDCODE 值为0xF5059093,表示匹配成功,继续执行32P 芯片的编程使能操作,包括使能PROGRAM 操作以及UNLOCK、ERASE 用户寄存器和数据寄存器等。然后,上位机给DSP 发送BIN 文件数据,DSP 接收到数据后将其存放在片内SRAM 中,通过GPIO0~3 模拟标准的JTAG 时序,将SRAM 中存放的数据烧写到32P 芯片中,并回传软件烧写进度给上位机。重复上述操作,直到FPGA 软件全部烧写完成。烧写完成后,执行32P 芯片的编程禁止操作,结束在线升级。

3.2 上位机软件

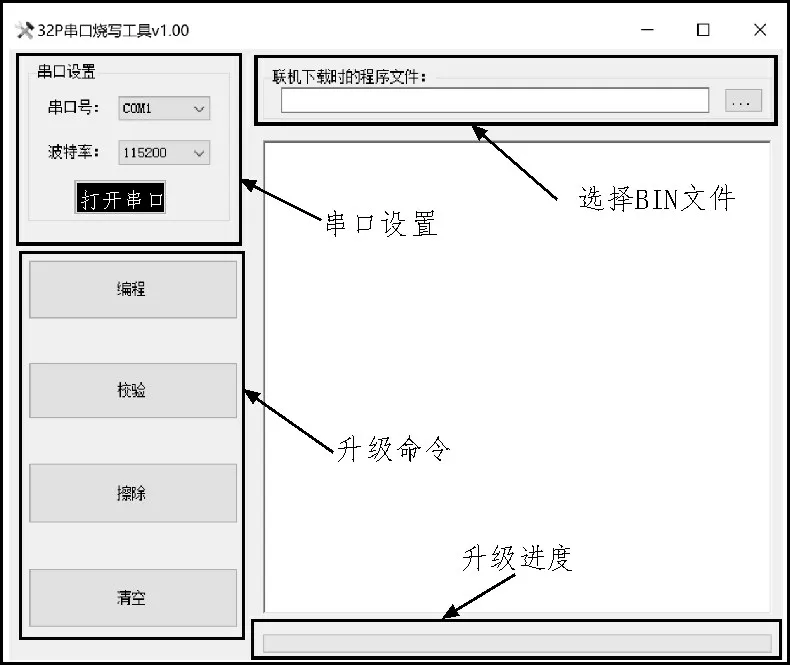

上位机软件使用C#语言完成界面开发,界面如图4 所示,包含串口设置、升级命令、BIN 文件选择以及升级进度等部分。用户通过操作上位机进行FPGA 软件在线升级,上位机对FPGA 软件进行数据预处理,并通过RS422 串口与DSP 建立连接和数据交互,部分握手协议如表1 所示。

表1 部分握手协议

图4 上位机界面

3.3 DSP软件

3.3.1 SVF文件解析

串行矢量格式(Serial Vector Format,SVF)是一种标准文件格式,用来记录JTAG 操作,包括JTAG 指令代码、指令寄存器(Instruction Register,IR)和数据寄存器(Data Register,DR)的长度及内容等,其中IR的长度通常大于2 个比特。SVF 文件可以利用Xilinx iMPACT 软件直接生成,文件内容为ASCII 文本。

所有JTAG 操作都通过32P 的测试访问端口(Test Access Port,TAP)进行控制,其中TAP 控制器是一个16 状态的有限状态机,如图5 所示。TAP 控制器包含了TMS、TDI、TDO 和TCK 四种信号,这些信号通过TAP 控制器与32P 进行数据交互。所有JTAG 操作是将数据移入或者移出IR 和DR 寄存器,通过SHIFT-IR 状态访问IR 寄存器,通过SHIFT-DR状态访问DR 寄存器。在SHIFT-IR 和SHIFT-DR 状态期间,在TCK 的上升沿采样TDI 输入信号,在TCK的下降沿更新TDO 输出值。

图5 有限状态机

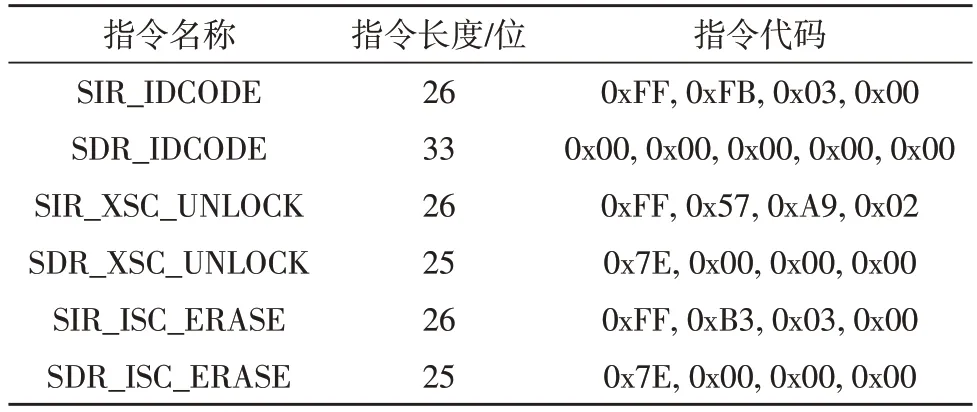

利用Xilinx iMPACT 软件对图2 硬件原理图中的32P 芯片进行编程操作,生成了完整的SVF 文件。当执行SHIFT-IR 命令时,需要将TIR、SIR 和HIR 的数值和长度按照TIR+SIR+HIR 的顺序合并为新的数值和长度;当执行SHIFT-DR 命令时,需要将TDR、SDR和HDR 的数值和长度按照TDR+SDR+HDR 的顺序合并为新的数值和长度,SVF 文件解析后的部分指令代码和长度如表2 所示。

表2 JTAG指令

3.3.2 DSP软件开发

DSP 系统工作频率设置为150 MHz,GPIO0 配置为输入,GPIO1~3 配置为输出,GPIO28 和29 配置为串口SCIA,并进行相应的初始化操作。根据图5 所示TAP 控制器有限状态机的操作顺序,编写了TAP复位、SIR 数据发送、SDR 数据发送等底层驱动接口函数。根据SVF 文件及解析后的指令代码和长度,编写了32P 擦除、编程打开、编程禁止等驱动函数,其中32P 擦除驱动代码如下:

DSP 通过SCIA 串口与上位机进行数据收发,并利 用GPIO0~3 分别模拟JTAG 接口的TDO、TMS、TCK 和TDI 信号,实现对32P 的擦除、编程和校验操作,其中对32P 编程操作的软件流程如图6 所示。

图6 32P编程软件流程

执行32P 编程操作时,上位机首先给DSP 发送0x32 和0xCD 两个字节的数据,若DSP 接收到正确数据,则执行32P 编程使能操作并回复ACK 数据,否则回复NACK 数据。回复ACK 数据后,DSP 等待接收0x31 和0xCE 两个字节的数据,若接收正确,则回复ACK 数据并继续接收4 个字节的起始地址和一个字节的校验值。如果接收到的地址有效且异或校验结果正确,则DSP 回复ACK 数据并重复执行如下操作:

1)获取待接收数据的字节数N;

2)接收N个字节的数据以及校验值;

3)将接收的数据写入32P 中。

上位机发送完FPGA 软件所有数据后,发送0x33 和0xCC 两个字节数据,若DSP 接收正确,则执行32P 编程禁止操作并回复ACK 数据,结束32P 编程操作。

4 实验结果与分析

为了验证基于TMS320F28335 的FPGA 软件在线升级方法的可行性,参照图2 所示硬件原理图搭建了系统实物。将DSP 在线升级程序固化至TMS320F28335 芯片的片内FLASH 中,上电后自动执行升级程序。设计了一个调试成功的FPGA 软件,其功能为LED 指示灯以1 Hz 的频率闪烁。通过在线升级的方式更新配置芯片32P 中的软件,若系统重新上电后FPGA 运行状态与测试程序功能一致,则表明软件在线升级成功。

在图4 所示上位机软件中设置串口号为COM1、串口波特率为115 200 bps 并打开串口,加载LED 测试软件,将所选LED 软件通过TMS320F28335 芯片烧写至配置芯片32P 中,烧写32P 的同时利用逻辑分析仪软件采集TMS、TCK、TDI、TDO 四种信号的数据。

通过对比LED 测试软件BIN 文件和采集结果的数据,可以看出LED 测试软件传输无误。升级结束后,断电重启FPGA,FPGA 自动加载32P 中更新后的程序,可以看到电路板上LED 指示灯以1 Hz 的频率闪烁,说明LED 测试软件已成功烧写至配置芯片32P 中。

为进一步验证所提升级方法的稳定性和可靠性,多次修改LED 测试软件,改变LED 指示灯闪烁的频率,执行上述升级流程。大量实验结果显示,FPGA 重新上电后从32P 加载新程序,每次的运行状态均与测试软件功能一致,表明基于TMS320F28335的FPGA 软件在线升级方法具有较好的可行性、稳定性和可靠性。

5 结论

由于在DSP+FPGA 架构的嵌入式系统中利用DSP 在线升级FPGA 的方法未见文献论述,提出了一种基于TMS320F28335 的FPGA 软件在线升级方法。在理论分析的基础上,给出了所提方法的硬件原理图和软件实现流程。大量的实验结果表明,该方法具有较好的可行性、稳定性和可靠性,可以实现DSP+FPGA 架构下不拆产品就可升级FPGA 软件的目的。