PCB制造基本工艺路线

——减成法与加成法

龚永林

(本刊主编)

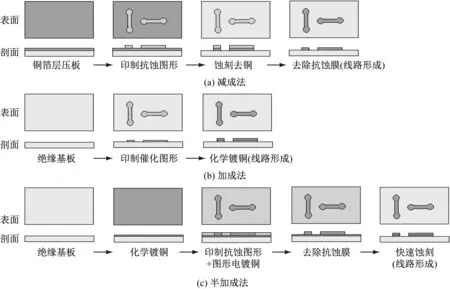

在印制电路板(printed circuit board,PCB)制造技术的发展过程中,开创了多种工艺路线。按照导体图形形成的路径,基本工艺路线可归纳为3 种,分别为减成法、加成法与半加成法。从原材料到成品基本上采取的是减法与加法工艺。

(1)减成法(subtractive process),采用覆铜箔层压板表面形成抗蚀线路图形后,通过选择性蚀刻去除多余铜箔,得到导体图形。减成法又称铜箔蚀刻法,基本流程如图1(a)所示。

图1 减法与加法3种基本工艺路线

(2)加成法(additive process)或称全加成法(fully additive process/all additive process),又称添加法。其采用含光敏催化剂的绝缘基板,在按线路图形曝光后使需要导电线路区域活化、沉铜,通过选择性化学镀铜(厚铜)得到导体图形。基本流程如图1(b)所示,其不存在蚀刻(减法)过程。

(3)半加成法(semi-additive process,SAP),采用绝缘基板进行化学沉铜得到薄铜箔,通过印制抗镀图形(负像)和图形电镀加厚导体,将多余薄铜箔快速蚀刻除去得到导体图形。基本流程如图1(c)所示,其以沉积铜导体(加法)为主,又辅以快速蚀刻(减法)过程。

减成法工艺成熟、稳定,自PCB 商品化70 多年以来,一直以减成法为主要工艺路线。从基材到专用设备具有完整产业链。由减成法制得的PCB 质量稳定可靠,其不足之处是原材料消耗较多,产生较多的污染物,不利于清洁生产。另外,减成法工艺是蚀刻铜层,加工线路程度有限,通常最小线宽/线距在50 μm以上。

加成法的工艺研发早于减成法。例如,在绝缘基板上直接黏贴金属粉末,或者印刷导电膏构成导电线路,只因线路精度不够以及与基板结合力差而未能流行。于是加成法的方向致力于绝缘基板上选择性地化学镀铜,实现铜线路图形。虽然该加成法可以制取线路图形,并且能做到小于10 μm 的高密度细线路,但在与基板结合力和线路导电可靠性方面不足,至今还在实验室阶段。

现在又有新的加成法技术,有的称增材制造,如印制电子(printed electronics)或加成电子(additive electronics)。通常是采用导电油墨直接在绝缘基材上印刷或打印出线路图形,简单的如在聚酯膜上印刷银浆线路形成的薄膜开关板,复杂的如3D打印功能油墨形成多层PCB及立体PCB。

介于减成法与加成法之间的半加成法,虽然采用了无铜箔基板,但有电镀铜与蚀刻过程。半加成法使导体有一定厚度,保证了线路的导电性,而蚀刻的是薄铜层,快速蚀刻(闪蚀)有利于细线路制作,可加工最小线宽/线距小于30 μm。

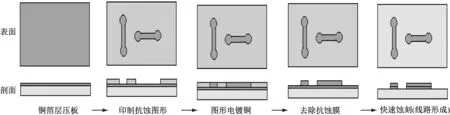

为了确保铜箔与绝缘层之间的结合力,又产生了改进型半加成法(modified semi-additive process,MSAP)并得到应用,流程如图2 所示。为了符合细线路的加工要求,MSAP 采用覆铜板或绝缘板上压合铜箔构成导体层。若铜箔层较厚,先采取化学蚀刻减薄铜层,如减薄铜把35 μm 或18 μm 的厚铜箔层蚀刻至12 μm 或9 μm 以下,然后再制作线路图形。如果采用的是薄铜箔覆铜板,或压合的是薄铜箔,就不需减薄铜过程。MSAP 比SAP 稳定和质量可靠,目前应用得更多。

图2 改进型半加成法流程

另有Averatek 公司开发的半加成法技术,称为A-SAP。采用绝缘基板在表面涂上一层催化油墨,然后进行钯活化和化学镀铜,形成导体层,再进行干膜光致成像、图形电镀铜和去膜、蚀刻(闪蚀),完成线路图形。A-SAP 可以实现25 μm以下,甚至10 μm的细线路。

目前,减成法仍然是PCB 制造的主流技术;半加成法特别是改进型半加成法技术也已成熟,普遍应用在高密度连接(high density interconnector,HDI)板与集成电路(integrated circuit,IC)载板制造中;加成法在印制电子方面前景灿烂,随着功能性油墨新材料的出现和印刷与打印技术的进步,应用将越来越广泛。就可持续发展而言,加成法比减成法更有优势。