人工智能服务器用高多层PCB制作关键技术研究

孙保玉 宋建远 袁为群 郭兴波 麦美环

(深圳崇达多层线路板有限公司,广东 深圳 518117)

0 引言

人工智能(artificial intelligence,AI)是研究如何模拟人的思维能力和智力活动方式,并不断拓展、提高该思维能力,从而延伸人类思维功能的系统。从1956 年夏季达特茅斯会议首次使用人工智能概念开始至今,人工智能的发展已经有60 余年,人工智能的功能体系也发生了翻天覆地的变化。其发展已经突破了单个领域的应用,逐渐形成整个社会生产力生产关系的变革[1]。

AI 服务器为重要的信息产业基础设施。AI 服务器通常搭载图形处理器(graphics processing unit,GPU)、现场可编程门阵列(field programmable gate array,FPGA)、专用集成电路(application specific integrated circuit,ASIC)等加速芯片,利用中央处理器(central processing unit,CPU)与加速芯片的组合可以满足高吞吐量互联的需求,为自然语言处理、计算机视觉、语音交互等人工智能应用场景提供强大的算力支持,已经成为人工智能发展的重要支撑力量[2]。

AI 服务器的特点和需求,促使印制电路板(printed circuit board,PCB)不断向高密度、高精度、高集成度方向发展,这就要求PCB 从常规的多层设计向高速度、高密度、高多层(10层以上)转化。使用高速基材生产制作具有高速、大容量、高可靠性信号传输能力的AI 服务器用高多层PCB成为该细分领域的发展必然。

本文选取一款用于AI 服务器的24 层多层PCB,就其结构特点、设计方案、关键制作技术等做详细介绍。

1 试验部分

1.1 产品参数特点

本款AI 服务器用24 层多层PCB 的产品关键参数见表1。

表1 AI服务器用24层多层PCB关键参数表

1.2 制作工艺流程

本款AI 服务器用24 层多层PCB 产品具有下列工艺设计特点。

(1)高频、高速材料设计:采用M7N 高速板材,支持更高频率的信号传输,具备高速、大容量信息传输基础。

(2)大尺寸、高厚度、高层数:具有良好的承载性,一般来说,AI 服务器主板要比传统服务器主板大许多,这主要是因为在其中要安装更多的组件,如更多的外围组件互连(peripheral component interconnect,PCI)(5 条以上)、外围组件互连扩展(peripheral component interconnect extended,PCI-X)、内存插槽(4 条以上),还可能有多个CPU插槽。

(3)盲孔技术:降低PCB 的尺寸和质量,减少层数,提高电磁兼容性,缩短连线长度,满足高速电路时序要求。

(4)背钻孔:特定层信号传输,信号完整性。

(5)高厚径比:更高的布线密度,更多的信号线路数和节点数。

(6)树脂塞孔:利用树脂将导通孔塞满,并在孔表面进行镀铜,有助于缩小孔与孔的间距,减小板的面积,解决导线与布线的问题,提高布线密度。

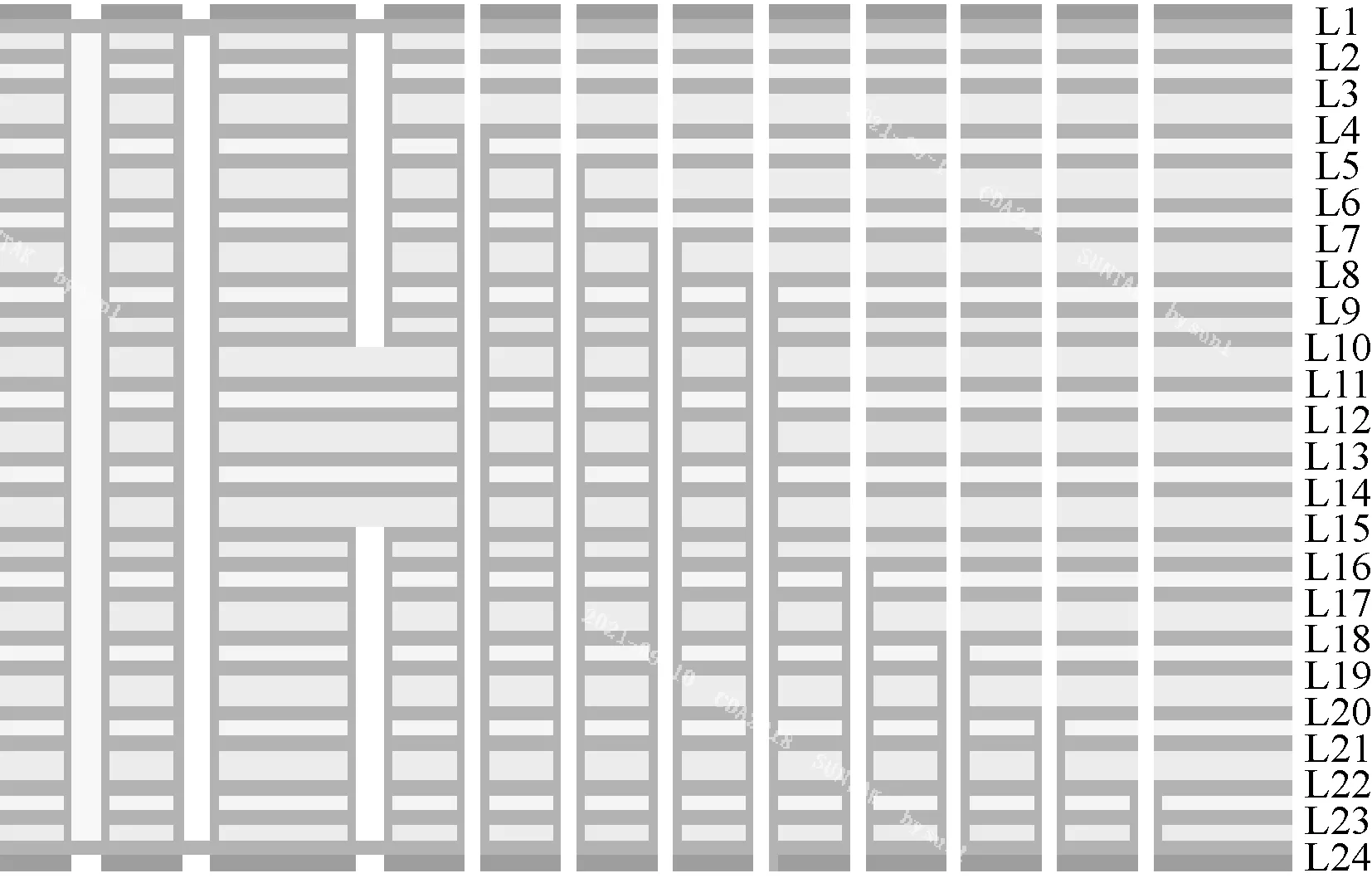

本款AI 服务器用24 层多层PCB 产品的具体工艺制作流程如图1所示。

图1 本款AI服务器用24层多层PCB工艺制作流程

2 结果与讨论

2.1 N+C+N叠构设计技术

2.1.1 技术难点描述

对于非对称叠构设计的PCB 层压结构,芯板厚度上下不对称,压合后,薄的芯板支撑力不足、翘曲,出现PCB 翘曲、弓弯的现象。PCB 翘曲、弓弯会在组装元器件时引起偏移、虚焊等质量问题。

为了改善以上问题,通常采用的处理方式主要包括:①延长层压过程的参数时间,增加层压结构中树脂固化程度,使之不易变形;②优化内层图形非工作区域板边图形设计,全部设计为圆点图形,打破铜皮,在层压前提前释放芯板应力。

这种处理方式存在以下缺陷:①增加层压参数时间,生产效率低,且改善效果较差;②内层芯板图形设计为圆点状,改善翘曲的效果较差。

2.1.2 技术改善方案

本款AI 服务器用高多层PCB,设计总共24 层,压合板厚2.457 mm±0.174 mm。压合叠构设计采用N+C+N(10+4+10)的对称设计方式,其中,10 层采用“1+8+1”的对称设计方式、4 层采用2+2 对称设计方式(其中“1”为单层铜箔层,“8”为4 套芯板,“2”为1 套芯板)。该设计为全流程对称设计,在压合过程中能充分均衡压合过程中的压力,保证表面的平整,保证压合过程中的半固化片(prepreg,PP)充分、均匀地流动,改善了压合过程中产生的翘曲、弓弯等问题,避免组装元器件时de 偏移、虚焊等质量问题。N+C+N层压结构如图2所示。

图2 N+C+N层压结构

2.2 双面树脂塞孔控制技术

2.2.1 技术难点描述

对于PCB 采用大小孔塞孔,塞孔的孔径极差为0.175 mm,且塞孔距非塞孔的最小距离为0.49 mm,为塞孔的制作难点。常出现以下塞孔不良问题:①网版偏位,基板补偿后系数与生产板不匹配,基板多次使用后受刮刀压力作用变长,对位未调正;②油墨气泡,油墨抽真空时间不足或抽真空方式不正确;③铜渣、披锋、杂物堵孔,电镀铜渣、钻孔披锋或生产过程中杂物堵孔未洗穿;④不下油,刮刀角度偏小、塞孔速度快、刮刀不平整导致局部不下油。

2.2.2 技术改善方案

本款AI 服务器用多层PCB,树脂塞孔控制技术依次采用以下方式。

(1)过喷砂线:塞孔前过喷砂前处理且关掉喷砂段洗板,速度为2.5 m/min。

(2)树脂塞孔前处理:磨板速度控制在(3.0±0.5)m/min。

(3)塞孔前烤板:塞孔前180 ℃、1 h+烤板,板面温度保持在28~35 ℃。

(4)选择性真空塞孔:树脂油墨采用帝强SKY2000 HR-4,树脂黏度控制在350~1 000 dPa·s,真空度控制在10~120 Pa。

(5)塞孔参数控制:塞孔前,检查垫板和塞孔机的内部并清理杂物,塞孔前将塞孔油墨平铺在网版上抽真空30 min 以上,采用双面塞孔方式生产,先从背钻孔较多的一面开始,控制塞孔速度10~40 mm/s,塞孔完后不烤板,再从另外一面,控制塞孔速度10~40 mm/s;塞孔后,检查两面无树脂塞孔凹陷、空洞不良,方可批量生产。

(6)烘烤参数控制:115 ℃,30 min+150 ℃,60 min。

(7)陶瓷磨板线打磨:使用陶瓷墨板线打磨2遍。第一遍不织布且速度为2~3 m/min,未磨干净产品手工打磨后过陶瓷磨板线,2 组600#不织布抛光,且速度为(3±0.2)m/min。

(8)树脂自动化光学检测(automated optical inspection,AOI)检查:使用鹰眼AOI 检查,平均灰度值的范围控制为170~190,100%扫描检查塞孔饱满度。

2.3 高精度阻抗控制技术

2.3.1 技术难点描述

由于高频、高速产品应用的大幅提升,对PCB 高速数字信号完整性提出了新的要求。高速电路的传输线在高频、高速的情况下,对信号线的串扰、反射和电磁干扰等信号问题提出了很高的要求。而信号完整性的控制与实现,与传输线的阻抗有着很强的相关性。阻抗除了线阻抗,还包括形成互连的孔阻抗,孔阻抗在很高的传输速度下对信号有很明显的影响,因此,必须考虑孔阻抗的影响效果[3]。

按照常规的制作方法,阻抗条介质厚度整体偏下限,L8~L9层超下限规格:①分析设计资料,发现阻抗条位于板边靠近无铜区域,该区域的流胶量大,与单元内其他位置残铜率有很大区别;②这与切片读取的单元内数据相一致,单元内差分阻抗测试结果显示,阻抗未超差,但整体中值偏上4~7 Ω。

2.3.2 技术改善方案

本款AI服务器用高多层PCB 高精度阻抗控制技术依次采用以下方式。

(1)控制压合介质层厚度:将阻抗条移到靠近单元内的大铜面处,确保压合时该区域的树脂胶不容易流走,避免介质厚度偏薄,减少对阻抗的影响。一般板边的阻抗条处介质厚度与板内的介厚相差10~15 μm,差动阻抗影响2.5~4.0 Ω。

(2)管控棕化的微蚀量:将棕化的速度从3.5 m/min 提升到5 m/min,将微蚀量从1.3~1.8 μm降低到1.0~1.5 μm,同时提高效率42.9%。提升线速,减少微蚀对线路的影响。

(3)阻抗线设计加补:阻抗线设计时,工作稿补偿完之后,阻抗线额外增加5 μm 可改善阻抗偏高问题。如0.10/0.15 mm 的线宽,介质厚度0.1 mm,理论控制阻抗值为100 Ω,但在实际生产过程中介质厚度会存在不均匀的情况,偏厚就会导致阻抗偏高。而压合结构与压合条件一般是固定的,所以只能调整线宽的大小去对冲介质厚度对阻抗的影响,一般是在正常的蚀刻量补偿的基础上多补偿5 μm,就可以确保阻抗线偏上控制。

差分阻抗设计时,生产照相底版的线间距确保内层间距≥89 μm,外层间距≥100 μm;针对部分差分阻抗线,客户设计的间隙较小,按照工厂能力正常补偿后,生产制作能力无法满足,此时需对差分阻抗进行单测补偿,以增加阻抗线之间的间距。

2.4 高多层压合控制技术

2.4.1 技术难点描述

本款AI 服务器用高多层PCB 采用松下M7N材料,在常规压合制作过程中,出现了以下问题:①单元边空旷区无铜皮导致失压;②70 μm 内层铜位置爆板;③材料流动性差,内层铜厚位置填胶不足导致空洞;④该材料升温速率要求≥4 K/min,常规排板方式无法达到,导致树脂流动度差。最终引起爆板、漏电、内短等严重的质量问题,进而严重影响产品的质量和产品交期。

2.4.2 技术改善方案

本款AI 服务器用高多层PCB 压合控制技术,通过熔合预对位、熔+铆的方式排板(铆钉使用阶梯铆钉)、M7N 压合参数等操作,实现压合后无爆板分层及漏电问题,具体如:

(1)棕化烘烤:烘烤参数控制为120 ℃,60 min,分开静置冷却芯板,每叠芯板高度小于竖着的A4 纸高度,管控芯板表面温度降至室温(<30 ℃)后再生产。

(2)熔合预对位:采用吸尘器吸开窗位残胶(目视有残胶清洁),放板和PP 后检查4 角铣槽,确认无PP/芯板错位后再熔合;熔合参数采用温度设定(200±20)℃,恒温时间(30±10)s,冷却时间(20±10)s。

(3)MASS-LAM 排板:采用熔+铆的方式排板且铆钉使用阶梯铆钉,层间加白色缓冲纸;排板前检查寸套是否变形、缺口;芯板顺滑套进,不可拍打套进,保证上下层水平紧贴;每张钢板使用无尘布前清洁一次板面;两组子板必须一起安排生产,安排同一炉压合;上下底盘加10 张牛皮纸,铜箔外加铝片,层间加5 张牛皮纸;排板层数为2片/层,2层/叠。

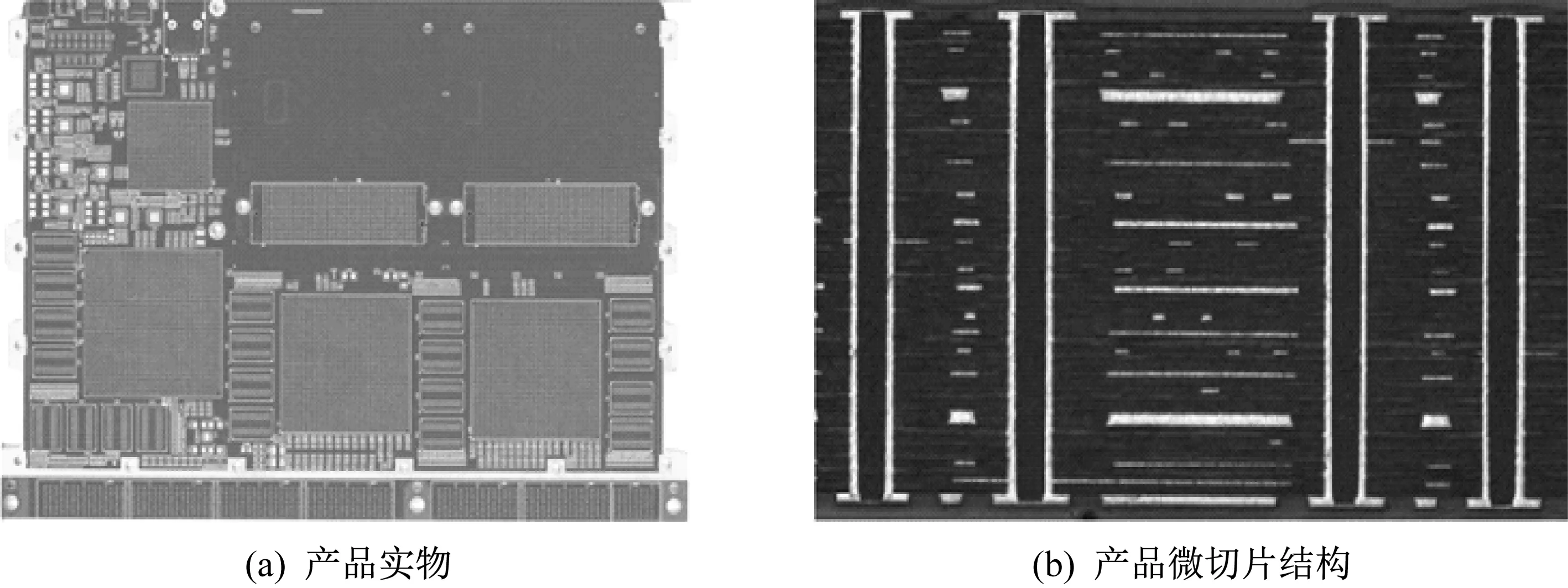

(4)层压参数:棕化后到层压进炉时间≤24 h;压板使用博可压机,层压按照M7N 专用压合参数控制(见表3)。压合后切片如图3 所示。由表3及图3可见,结果合格,无爆板分层及漏电问题。

图3 压合后切片分析

表3 M7N专用压合参数

2.5 高均匀性除胶控制技术

2.5.1 技术难点描述

一些特殊板料的PCB 在制板钻孔后,需要过等离子除胶及活化。在等离子生产过程中,为保持真空腔体内的真空度,需要真空泵不间断地对腔体进行抽真空,而现行的等离子机抽真空入口均集中于真空腔侧壁某一位置,导致靠近抽真空入口周围的板子由于等离子气体在抽真空过程中被抽走部分,除胶量远小于其他区域板子的除胶量,除胶均匀性极差[4]。

2.5.2 技术改善方案

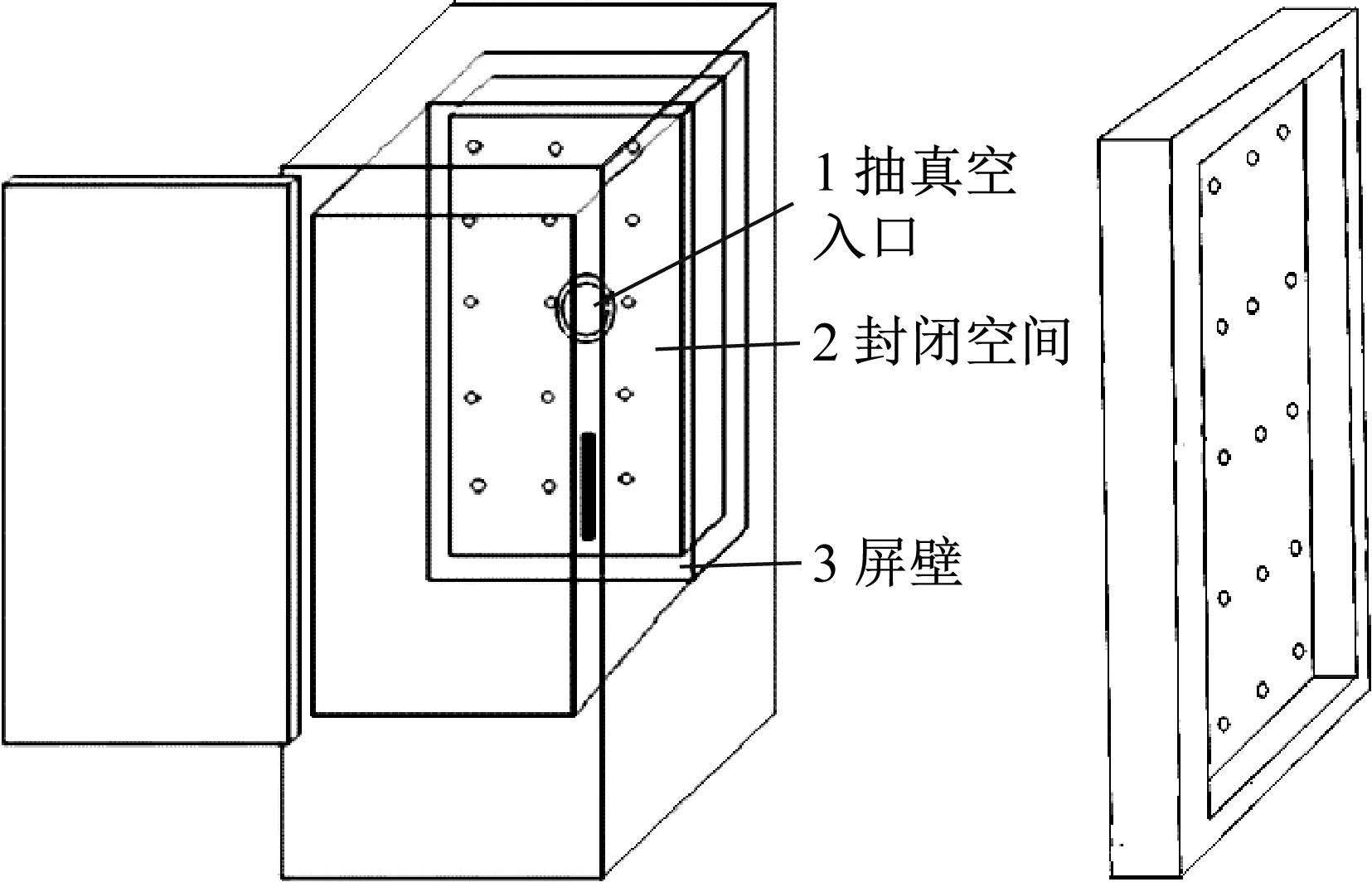

本款AI 服务器用高多层PCB 采用松下M7N材料,对除胶精度、除胶均匀性有较高要求,特创新开发高均匀性除胶控制技术如下。

(1)在抽真空入口的真空腔侧壁上安装一面长方体的屏壁,长方体屏壁与真空腔入口处的真空腔侧壁等大(具体大小视等离子机真空腔大小而定),将屏壁中间掏空,形成一个深50 mm的长方体容器,四周及屏壁另一侧保留厚度10 mm(实际深度和余厚视抽真空气压及机台本身具体情况而定,可改动),并在屏壁另一侧均匀地钻出5 排小孔,小孔面积总和与抽真空入口面积等大(实际孔径大小及孔数视具体情况可改动)[4]。

(2)屏壁与抽真空腔入口侧壁形成一个与抽真空入口连通的封闭空间,抽真空时,先将夹壁空间的气体抽出,与真空腔形成气压差,气体由夹壁上的小孔均匀地从真空腔各处流入夹壁再由真空泵抽出,从而达到均匀抽真空的目的,防止由于局部抽真空等离子气体分布不均导致等离子除胶不均匀[4]。匹配开发的高精度、高均匀性除胶装置如图4所示。

图4 高精度、高均匀性除胶装置图

(3)除胶三段式参数控制。段1:N2200 mL/min,O21 800 mL/min,温度控制50 ℃,电源功率7 000 W,处理时间20 min。段2:N2160 mL/min,O21 200 mL/min,CF4240 mL/min,温度控制50 ℃,电源功率7 000 W,处理时间27 min。段3:N22 000 mL/min,温度控制50 ℃,电源功率7 000 W,处理时间2 min。

3 产品制作效果

整合各关键技术点并串联整个制作流程,成功地制作出了预期产品,产品实物如图5 所示。各项可靠性测试均合格,结果见表4。

图5 产品实物与微切片

表4 产品可靠性检测结果

4 结语

本文以一款整体24 层用于AI 服务器的多层PCB 为例,对其常见的制作难点和解决方案做了详细介绍以供参考。更深层次的技术和品质探索需要各位PCB同仁们的共同努力。