基于手机USB3.1应用的FPC信号传输研究

胡珂珂 郑泽红

(深圳市景旺电子股份有限公司,广东 深圳 518100)

0 前言

计算机技术的快速发展离不开通用串行总线(USB)的技术的推广与支持,IT产业的接口重大革命正是USB出现的原因。如今在USB2.0的基础之上,USB3.1增加了许多物理总线,由4线增加到9线,用来实现并行模式,这也使USB3.1有了超速的性能,以满足当前5G智能手机的通讯朝向高频高速化发展,同时也对基于手机USB3.1应用的挠性印制电路板(FPC)的材料和设计提出了更高规格要求。本文基于以往USB3.1应用的FPC的制作经验,从叠构设计、材料搭配、过程控制。损耗测试等展开一系列研究。

1 试验方法及材料

1.1 试验方法

根据在加工过程中对损耗影响因子的经验以及最终产品功能指标对材料的指向选择要求,本次试验将首先对不同厂商高频覆盖膜(CVL)材料的性能进行测试,然后再从不同网格设计、线宽设计,不同厂商高频覆盖膜对阻抗与损耗的影响变化进行研究(见表1)。

1.2 试验材料及测试设备

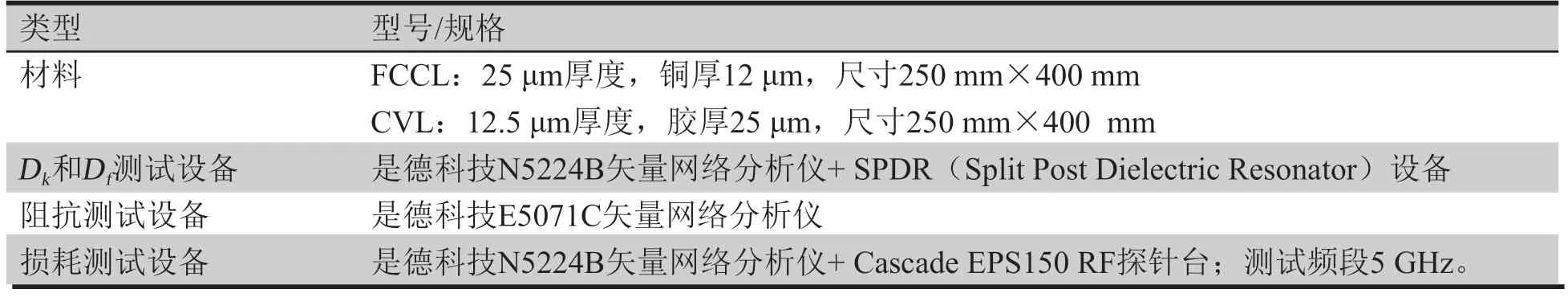

主要试验材料及测试设备见表2。

表1 测试方法及具体项目

表2 主要试验材料及测试设备

1.3 产品叠构

FPC产品叠够图见图1所示。

图1 FPCB产品叠构图

1.4 工艺流程

开料→减铜→钻孔→线路→AOI→覆盖膜→阻焊→表面处理→电磁膜→激光刻→FQA

2 测试结果分析

3.1 不同高频覆盖膜Dk和Df测试

将厂商A和B的高频覆盖膜的样品裁切成7 cm×7 cm的标准测试样件,测试常规条件(21±2)℃,(65±5)%RH)在2.5 GHz、5 GHz、10 GHz频率下的Dk与Df。具体测试结果见表3 。

从表3数据可以看出:厂商A的高频覆盖膜比厂商B的Dk大0.2,不利于后续阻抗与损耗的管控;不同频率下,材料的Dk与Df值基本无变化,后续可以采用一个频率来评估材料。

2.2 不同线宽设计阻抗对比

采用同一叠构测试,传输线长设计115 mm,使用厂商B高频覆盖膜材料制作产品,线宽设计75 μm、85 μm、95 μm,网格设计0.15 mm×0.30 mm,阻抗管控在(90±10)Ω条件下,阻抗数据进行对比,具体如图2。

从图2数据可以分析得出:随着线宽增大,阻逐渐降低;85 μm和95 μm设计线宽的阻抗相差3Ω,说明线宽增大到95 μm后,阻抗开始趋于稳定。

2.3 不同线宽设计损耗对比

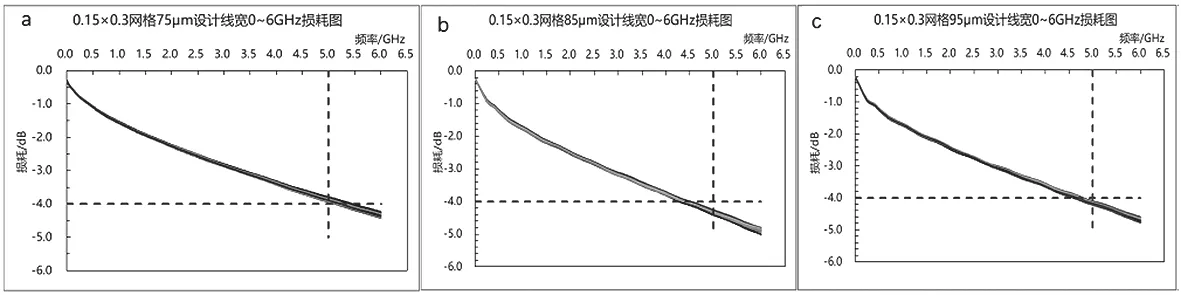

采用同一叠构测试,传输线长设计115 mm,使用厂商B高频覆盖膜材料制作产品,线宽设计75 μm、85 μm、95 μm,网格设计0.15 mm×0.30 mm,阻抗管控在(90±10)Ω条件下,损耗数据进行对比,具体如图3。

表3 不同频率下不同厂商高频覆盖膜的Dk与Df

图2 不同线宽设计阻抗对比

图3 不同线宽设计损耗对比

从图3数据可以分析得出:(1)75 μm设计线宽下,5 GHz损耗最大值为-3.95 dB,最小值为-3.79 dB,平均值为-3.87 dB,极差0.16 dB;(2)85 μm设计线宽下,5 GHz损耗最大值为-4.4 1 d B,最小值为-4.2 6 d B,平均值为-4.33 dB,极差0.15 dB;(3)95 μm设计线宽下,5 GHz损耗最大值为-4.22 dB,最小值为-4.10 dB,平均值为-4.16 dB,极差0.12 dB;(4)同频率时,75 μm线宽设计损耗最小,85 μm设计线宽损耗最大,随着线宽逐渐增加,损耗先增加后降低;(5)在同时满足阻抗与损耗的条件下,设计线宽选择75 μm。

2.4 不同网格设计阻抗对比

采用同一叠构测试,传输线长设计115 mm,使用厂商B高频覆盖膜材料制作产品,设计线宽为75 μm、85 μm、95 μm,设计网格为0.15 mm×0.30 mm和0.15 mm×0.25 mm,阻抗管控在90±10 Ω条件下,具体数据见图4所示。从图4中的损耗数据可以看出,0.15 mm×0.25 mm网格的阻抗略小于0.15 mm×0.30 mm网格;0.15 mm×0.30 mm网格设计阻抗数据稳定性优于0.15 mm×0.25 mm网格。

2.5 不同网格设计损耗对比

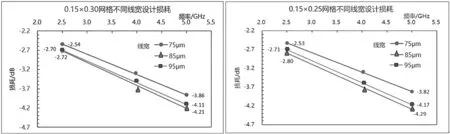

采用同一叠构测试,传输线长设计115 mm,使用厂商B高频覆盖膜材料制作产品,线宽设计75 μm、85 μm、95 μm,网格设计0.15 mm×0.30 mm和0.15 mm×0.25 mm条件,损耗数据具体见图5。

图4 不同网格设计阻抗对比

图5 不同网格设计损耗对比

从图5的损耗数据可以看出,在三种设计线宽下,两种不同网格设计对损耗影响不大,结合前面网格对阻抗的影响,可以选择0.15 mm×0.30 mm的网格设计。

2.6 不同高频覆盖膜阻抗对比

采用同一叠构测试,传输线长设计115 mm,使用厂商A和厂商B高频覆盖膜材料制作产品,线宽设计75 μm,网格设计0.15 mm×0.30 mm的条件,阻抗数据具体见图6所示。

从图6数据分析得出:75 μm设计线宽下,厂商A阻抗最大值为104 Ω,最小值为93 Ω,平均值为98 Ω,极差11 Ω;厂商B阻抗最大值为103 Ω,最小值为93Ω,平均值为98 Ω,极差10 Ω;从阻抗波动范围来看,厂商B的阻抗相对稳定。

2.7 不同高频覆盖膜损耗对比

采用同一叠构测试,传输线长设计115 mm,使用厂商A和厂商B高频覆盖膜材料制作产品,线宽设计75 μm,网格设计0.15 mm×0.30 mm条件,损耗数据具体如图7。从图7的损耗数据可以看出,厂商B的高频覆盖膜的损耗低于厂商A的,结合前面阻抗的影响,选材厂商B有利于阻抗稳定与降低损耗。

图6 不同覆盖膜阻抗数据对比

图7 不同高频覆盖膜损耗对比

3 总结

从线宽设计、网格设计、覆盖膜这三个角度探讨了其与产品阻抗、损耗的因果关系,为USB3.1的设计和选材提供了充分的数据支撑,得到具体结论如下:

(1)随着线宽设计的增加,阻抗逐渐减低,损耗先增加后降低,线宽设计增加到95 μm后,阻抗趋于稳定,75 μm设计线宽损耗最低;

(2)随着网格含铜率降低,阻抗有所增加,损耗差别不大,0.15 mm×0.30 mm网格的阻抗略大于0.15 mm×0.25 mm,两者损耗相近;

(3)覆盖膜Dk、Df越小,越有利于阻抗稳定与降低损耗。