基于时间模式信号处理的三阶FIR 滤波器实现

赵倩,陈杨军

(西安交通工程学院,陕西西安 710300)

许多现代集成电路应用对速度和功耗的要求越来越严格。由于集成电路应用的器件尺寸越来越小[1],且使用了低电压电源,因此利用先进的互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)技术可以满足这些标准的要求[2]。但是许多以前的模拟电路架构,例如模数转换器,难以克服电压余量低和动态范围小的问题。时域技术是一种相对较新的时间处理方法,其利用时间延迟、时差或脉冲宽度技术,因此,在时域电路中,时间是最重要的物理量。

信号滤波是生物医学传感器接口、图像处理、无线接收机等最先进应用中最重要的功能之一。基于有限脉冲响应/无限脉冲响应(Finite Impulse Response/Infinite Impulse Response,FIR/IIR)滤波器实现的信号滤波属于传统离散时间数字信号处理(Traditional Discrete-time Digital Signal Processing,TD-DSP)中的基本信号处理操作[3-4]。FIR/IIR 的实现需要一些基本运算符,如z-1运算符和信号加法器以及信号乘法器,以获得滤波器系数[5-6]。传统的FIR/IIR 实现主要基于纯数字设计方法,时间模式下的FIR/IIR 实现要求基本运算符在时域中工作,这意味着z-1加法器和乘法器必须能够处理时间模式量,这些系统被归类为离散时间信号处理系统。

文中提出了一种基于新型时间模式乘法器和时间模式加法器的三阶FIR 滤波器实现方法。时间模式乘法器和时间模式加法器两种电路都基于对简单时间寄存器拓扑的修改。通过三阶低通拓扑,可以在高频抑制、芯片面积和电流消耗之间得到有效权衡。提出的时间模态FIR 方法可以很容易地在电压模态的拓扑图上实现,并可以用时间模式对应的模态算子逐个替换电压模态算子。

1 时间模式信号处理

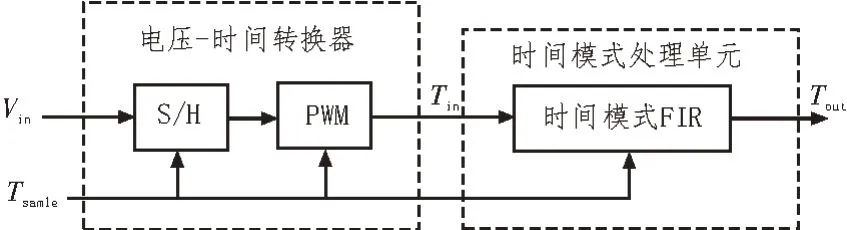

时间模式电路用于处理两个连续脉冲之间的时间差或恒定频率脉冲的时间宽度,文中侧重于处理恒定频率脉冲宽度的时间处理方法[7]。图1 所示为时间模式处理后的电压-时间转换框图。

图1 电压-时间转换框图

使用采样/保持电路(S/H)和脉宽调制器(PWM),将输入信号电压Vin转换为时间模式。采样/保持电路对于高频输入带宽是必需的,对于低频输入信号(例如来自传感器接口电路的信号)可以忽略[8-10]。基于PWM 技术,输入电压Vin对应于恒定频率脉冲的输入脉冲宽度Tin,如下式所示:

式中,kVT为电压-时间转换系数,n为采样数,而恒定频率假定为采样频率fsampling。Tin可以根据式(1)取连续值,但从采样时间可知,时间是离散的,相应的系统被视为是一个离散时间-连续信号处理系统[11-14]。信号由主时间模式系统处理,该系统能够处理脉冲序列的脉冲宽度。

在连续或离散信号处理中嵌入的一个主要构件是滤波器,该滤波器可以是模拟滤波器或FIR/IIR 滤波器,滤波器必须能够过滤掉所有不需要的信号或组件[14-16]。从时间模式的角度来看,任何滤波器的实现都类似于FIR/IIR 离散滤波器,这主要是因为使用了离散的采样时间。

文中是基于时域FIR 滤波器的实现,FIR 滤波器是一种信号处理滤波器,其脉冲响应(或对任何有限长度输入的响应)具有有限的持续时间。N阶离散时间模式FIR 滤波器输出序列中的每个值是最近输入值的加权和,如下式所示:

其中,Tin[n] 是输入脉冲宽度;Tout[n] 是输出脉冲宽度;N是过滤器阶数;bi是N阶FIR 滤波器在第i个时刻的滤波器系数,其中0 ≤i≤N。因此,在相应的时间模式FIR 滤波器中,最重要的运算符主要包括时间模式z-1运算符、时间模式乘法器和时间模式加法器。

2 时间寄存器的乘法和加法运算

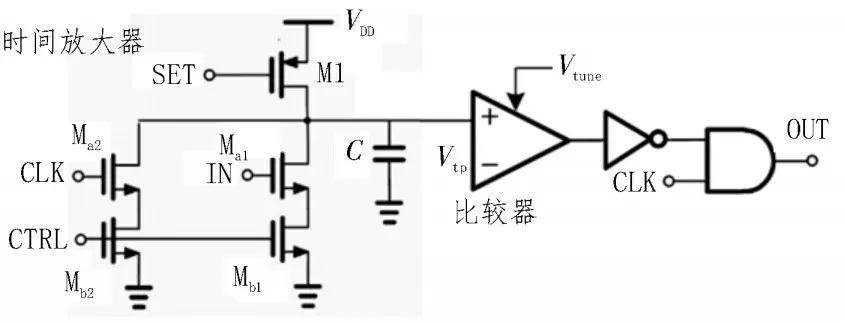

图2 所示为时间寄存器(TR)电路。当SET=0时,晶体管M1接通,电容器电压设置为VDD(电源电压)。当晶体管M2接通时,电容器放电,这由OR 门(或门)控制。通过数字校准回路,可以利用栅极电压CTRL 来校准放电斜率的变化[17-18]。

图2 时间寄存器电路

为了使输出与CLK 同步,同步电路包括一个与门、一个快速比较器和一个逆变器。设计该比较器的目的是提供快速瞬态响应,其三相点电压Vtp设置为与VDD/2 匹配。

设定信号的时间间隔TCLK是一个具有固定脉冲宽度和25%占空比的脉冲。当输入脉冲和CLK 均为0 时,电容器电压保持不变。考虑到CLK 引起的放电时间不发生变化,输入脉冲信号的脉冲宽度Tin越大,Tin引起的放电时间越长。输出是一个宽度等于TCLK-Tin的脉冲,允许存储Tin的值,同时输出脉冲与CLK 信号同步。

上述时间寄存器电路可以存储输入脉冲的时间间隔,并通过增益因子放大脉冲宽度。时间放大器电路如图3 所示。在此配置中,OR 门的操作由两个晶体管分支Ma1、Mb1或Ma2、Mb2执行。晶体管Ma1和Ma2具有与开关相同的纵横比。Mb1和Mb2的纵横比不同,放电斜率也不同。假设Mb2和Mb1的通道宽度分别为Wb2和Wb1,而两个晶体管的通道长度相同。输入脉冲信号的脉冲宽度Tin的放电斜率由下式给出:

图3 时间放大器电路

其中,a为时间增益,计算如下:

slopeCLK是由TCLK引起的放电参考斜率。

基于时间寄存器的时间加法器电路如图4 所示。时间加法器只是简单地将n个输入脉冲宽度Tin1,Tin2,…,Tinn相加,晶体管Mb1,Mb2,…,Mbn,Mbn+1具有相同的纵横比。输出脉冲宽度为:

图4 基于时间寄存器的时间加法器

时间寄存器的主要问题是工艺过程变化和芯片温度变化的强烈影响。由于MOS 器件的放电漏极电流和片上电容值的依赖关系,电容器电压放电斜率随工艺过程和芯片温度的变化而变化,可以使用数字校准回路来校准放电斜率,以实现更好的性能。

3 时域模块

1)时间模式z-1电路

时间模式z-1电路的作用是产生脉冲宽度等于Tin的输出脉冲,该脉冲与采样同步。如前一节所述,时间寄存器电路(TR)可以以脉冲宽度等于Tclk-Tin的输出脉冲形式存储输入信号的脉冲宽度Tin,这与CLK同步。四个串联时间寄存器电路的组合实现了z-1电路。假设采样信号是时间寄存器电路(TR1)的SET1信号,输入信号等于TR1 的输入,而最终输出信号是时间寄存器电路(TR4)的OUT4 的输出。

为了与SET2 脉冲同步,需在CLK1 的上升沿产生OUT1 脉冲。之后,OUT1 脉冲被用作时间寄存器电路的输入。OUT2 与CLK2 同步,其输出脉冲宽度计算为:Tout2=TCLK-Tout1=TCLK-(TCLK+Tin)=Tin。因此,相对于采样信号,OUT2 延迟了Tsampling/2。基于上述特性,OUT4 脉冲经过Tsampling延迟,其宽度值为Tin。考虑到这一点,z-1算子是通过在级联布局中利用四个时间寄存器电路产生的。

2)时间模式z-1乘法器电路

时间模式z-1乘法器的工作原理是产生脉冲宽度等于aTin的输出脉冲,其中Tin为输入脉冲宽度,a为乘法系数,输出脉冲与采样信号同步,并延迟一个时钟周期。

两个放大器-时间寄存器电路(AMP-TR)和两个时间寄存器电路(TR)串联的组合实现了时间模式z-1乘法器。假设采样信号是时间放大器电路TR1的SET1 信号,输入信号为时间放大器电路TR2 的输入IN1,而最终输出信号OUT 是TR2 的OUT4 的输出。时间放大器电路TR1 和时间放大器电路TR2 产生的时间放大系数分别等于a1和a2。

OUT1 脉冲在CLK1 的上升沿产生,以便与SET2脉冲同步。之后,OUT1 被用作TR1 的输入,即有Tout2=TCLK-Tout1=TCLK-(TCLK-a1Tin)=a1Tin,OUT2 与CLK2 同步。因此,相对于采样信号,OUT2 延迟了Tsampling/2。扩展上一个特性,OUT4 被延迟Tsampling,同步输出脉冲的脉宽为:

其中,乘法系数b=a1a2。

3)时间模式z-1加法器电路

时间模式z-1加法器可以将多个输入信号的脉冲宽度相加,并产生所有输入时间间隔之和的输出。

OUT1 脉冲在CLK1 的上升沿产生,以便与SET2脉冲同步,其值为Tout1=TCLK-(Tin1+Tin2)。之后,OUT1 被用作下一个TR 的输入,即有Tout2=TCLK-Tout2=TCLK-(TCLK-(Tin1+Tin2)=Tin1+Tin2,OUT2 与CLK2 同步。因此,相对于采样信号,OUT2 延迟了Tsampling/2,信号仅通过两个TR 获得一个周期的延迟。输出脉冲的脉冲宽度将由以下公式给出:

由上式可知,该电路实现了加法功能。

4 时域三阶FIR滤波器

文中设计了一个三阶FIR 滤波器,用所提出的时间模式z-1乘法器和加法器来证明时间模式滤波的概念。用时间模式处理单元实现三阶FIR 滤波器拓扑结构,如图5 所示。它使用三个z-1运算符、四个z-1乘法器和一个四输入z-1加法器。如前所述,使用两个放大操作有助于更好地逼近滤波器系数。为了近似b0、b1、b2和b3的精确系数值,只需要三个放大器系数,即0.3、0.4 和0.7。

图5 三阶FIR滤波器拓扑结构

5 结果

所有电路均采用三星28 nm FD-SOI CMOS 技术设计并通过仿真验证,电源电压VDD=1 V。使用适当的三相点补偿电路将比较器的电压三相点调整为0.5 V。考虑到输入脉冲宽度Tin是一个正弦信号,最大允许峰峰值幅度理论上可以等于TCLK,在研究中令其为40 ns。

5.1 时间模式z-1乘法器

z-1乘法器的操作如图6 所示。z-1乘法器时序波形的乘法系数为0.28,图6(a)所示为同步时钟。图6(b)、(c)分别为Tin=20 ns 的输入脉冲宽度和Tout=5.55 ns 的输出脉冲宽度。输入脉冲宽度Tin为20 ns 时,乘法系数为0.28。因此,该电路产生脉冲宽度为Tout=5.55 ns 的输出脉冲。

图6 乘法系数等于0.28的z-1乘法器定时波形

5.2 时间模式z-1加法器

z-1加法器的操作如图7 所示,输入脉冲宽度分别为20 ns 和5 ns。加法器产生脉冲宽度Tout的输出脉冲,这是前两个脉冲的总和,等于25 ns。在一个输入处使用5 ns 的稳定输入脉冲Tin1,而在第二个输入处,Tin2在0 ns 和40 ns 之间。很明显,所提出的加法器可以线性相加40 ns 动态范围内的所有值。

图7 两输入z-1加法器的定时波形

5.3 时间模式FIR滤波器

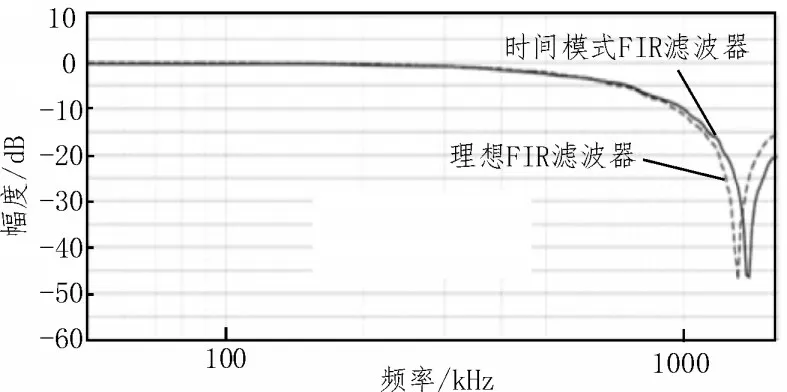

理想和实现的时间模式三阶FIR 滤波器的模拟幅度响应如图8 所示。采样频率为5 MHz,平均功耗为200 μA,包括实际滤波电路和数字校准的功耗。理想滤波器的陷波频率选择为1.31 MHz,接近所实现的FIR 滤波器的1.38 MHz 陷波频率,频率偏移为70 kHz,这些频率响应的差异性主要归因于滤波器系数的近似误差。

图8 理想和实现的时间模式FIR频率响应

6 结论

提出的时域三阶FIR 滤波器基于z-1延迟、z-1乘法器和z-1加法器等时间模式信号处理电路。对于频率为50 kHz 的信号,滤波器的峰值SNRR 为38.6 dB,5 MHz 采样频率下的平均电流消耗为200 μA,这种滤波器设计在时间模式信号处理中具有许多固有的优势。首先,其输出与采样频率同步;其次,由于拓扑结构是模块化的,因此只需在相同的复杂度上增加延迟和乘法器的数量就可以创建高阶滤波器;最后,与数字电路的兼容性使其成为在最先进拓扑中广泛使用的所有数字拓扑的完美候选。该技术可用于未来生产其他类型的滤波器,例如高阶FIR 或IIR滤波器,时间模式控制器也可以使用这种技术,该拓扑的制作和实验验证将是未来工作的一部分。