垂直电压增益自动比例控制电路设计

余 甜,王志斌,景 宁

(1.中北大学 仪器与电子学院,山西太原 030051;2.中北大学微系统集成研究中心,山西太原 030051;3.中北大学信息与通信工程学院,山西太原 030051)

该文提出的垂直放大系统采用运算放大器、数模转换器和高精度电阻设计了数字程控垂直增益放大电路[1],由FPGA接收上位机指令或者分析ADC采集数据的大小控制LTC2600 输出不同的电压来实现对垂直系统0.5、1、2、5、10、20、50倍放大倍数的调节[2],对应于上位机垂直系统调节范围1~100 mV/div 中的七个档位[3],相邻的放大倍数调节按照1、2、5倍放大倍数互相变换[4],具有更全面的覆盖范围,以保证ADC位数尽量多的被使用,使得上位机恢复的波形更加精确[5]。

1 垂直增益放大电路工作原理

1.1 顺序等效取样原理

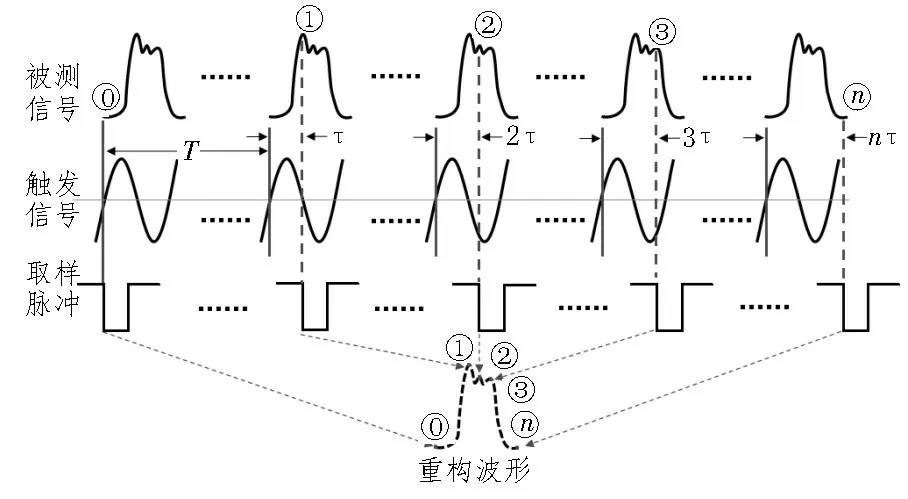

垂直增益放大电路作为取样示波器波形重构的重要组成部分,其工作原理如图1 所示。在被测信号与触发信号同步的基础上,精密时基模块在触发信号的驱动下每次触发都会延时相同的时间产生取样脉冲对被测信号进行取样处理[6],同时产生同步采样时钟驱动垂直增益放大电路的模数转换模块进行取样采集[7],每个取样点分别取自被测信号波形的不同位置上,若干取样点组成一个周期,就可以在上位机直接重构出被测信号,重构信号的频率计算如式(1)所示:

图1 顺序等效取样原理

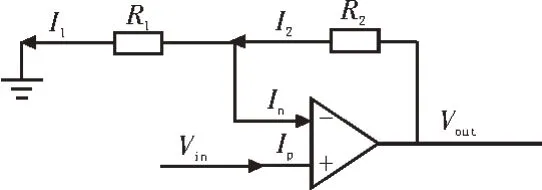

1.2 同相比例运算电路

该设计的垂直增益放大电路基于同相比例运算电路的原理进行设计[8],电路如图2 所示,输入信号Vin加在运算放大器的同相输入端,输出信号Vout经过一个电阻R2加在运算放大器的反向输入端,形成负反馈。由于理想的运算放大器的净输入电流为0,所以Ip=In=0,I1=I2。同时由于运算放大器的同相和反相输入端虚短路,同相输入端的电压与反相输入端的电压相同,即可以计算出输出电压Vout与输入电压Vin的运算关系:

图2 同相比例运算电路

由式(2)可知,同相比例运算电路的电压增益放大倍数取决于R1+R2和R2之比,通过选择不同大小的高精度的电阻搭建同相比例运算电路,就可以实现信号的放大、缩小或者保持不变[9]。

2 垂直增益放大电路设计

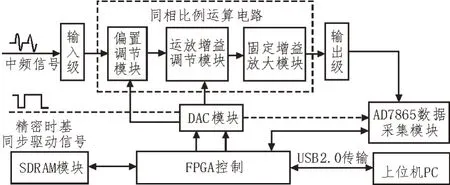

文中硬件系统包括五部分:数字控制垂直增益放大电路、数模转换电路、数据采集电路、数据存储电路和USB2.0 数据传输电路。硬件系统设计框图如图3 所示。

图3 硬件系统设计

2.1 数字控制垂直增益放大电路

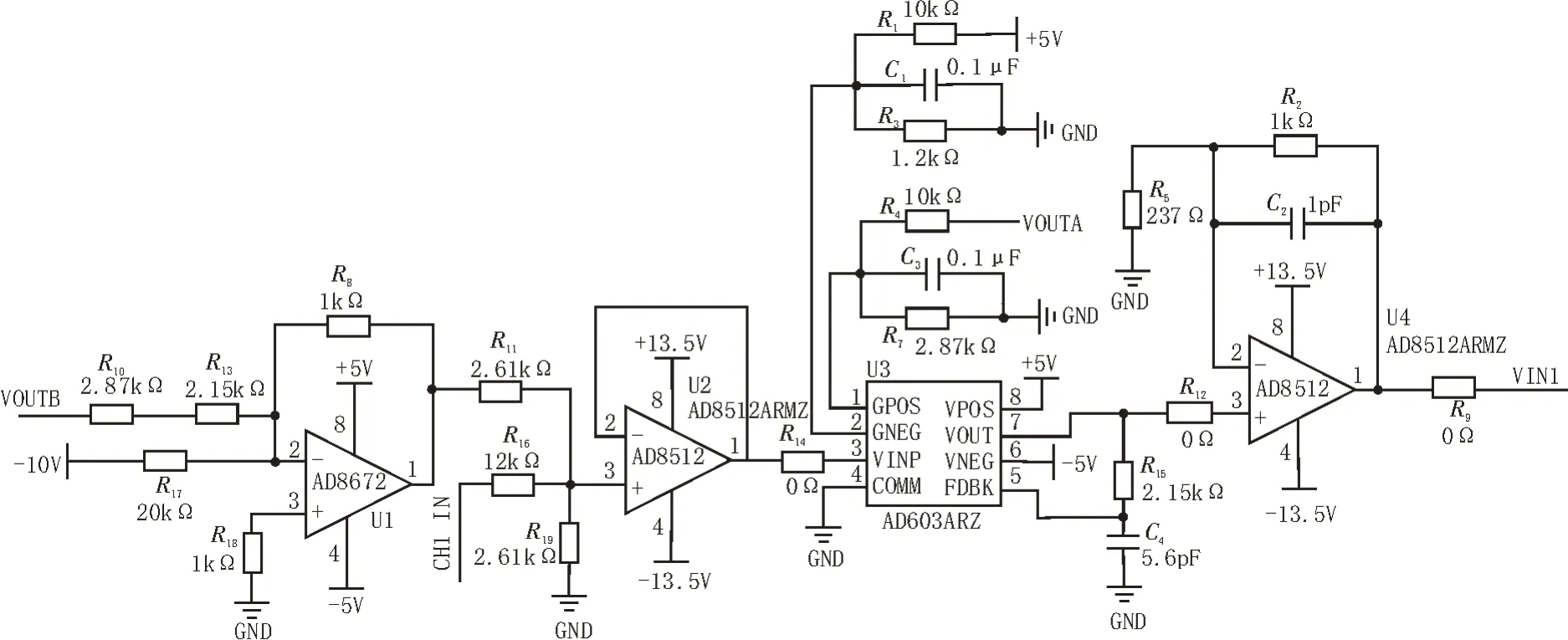

数字控制垂直增益放大电路设计由集成运放AD8512、AD8672、可变增益放大器AD603 和精度为0.1%的贴片电阻搭建而成。FPGA 采用Alter 公司的EP4CE22FC8N 芯片,用于通过控制数模转换LTC2600 输出电压来改变垂直增益放大电路的放大倍数,同时控制数据的采集和存储并使用USB2.0 将处理后的数据传给上位机[10]。

图4 所示为数字控制垂直增益放大电路原理,U1、U2 与R8、R10、R11、R13、R14、R16、R17、R18构成输入级同相比例运算电路,取样器输出中频信号为CH1_IN,VOUTB 与数模转换芯片LTC2600 输出相连,由FPGA 控制LTC2600 对中频信号的偏置进行调节,并将输入信号的幅度衰减10 倍以满足AD603 的输入范围[11]。U3 与R1、R3、R4、R7、R15、C1、C3、C4构成第二级同相运放增益调节电路,VOUTA 与数模转换芯片LTC2600 输出相连,通过改变VOUTA 的电压来改变GPOS 和GNEG 的引脚电压差,即可改变可变增益放大器AD603 的增益。输出级由U4 与R2、R5、R9、R12、C2构成同相固定增益放大电路,负责将AD603输出的信号放大5 倍,并输出给AD7367 数据采集模块[12]。

图4 数字控制垂直增益放大电路

可变增益放大器AD603 的增益为0~40 dB,通过FPGA 控制LTC2600 调节AD603 的增益,鉴于该设计垂直增益放大电路采用125 比例放大,故采用其中的七种增益放大倍数。前级中频电路取样器每20 μs 取样一次,取样后的信号经高阻积分电路、加法器和三级滤波电路的固定增益放大后输出幅值范围为-10~10 V,频率为50 kHz 的中频信号输入垂直增益放大电路[13],该设计电路增益带宽为8 MHz,输入幅值范围为-12~12 V,满足应用要求。

2.2 数模转换电路模块

该设计中数模转换电路使用LTC2600 调节垂直增益放大电路的增益倍数,LTC2600 的基准电压使用ADR02 输出+5 V 参考电压。上位机通过USB 发送16 位十六进制数作为控制指令,由FPGA 读取USB 中接收到的指令并识别上位机控制的通道以及所控制的通道的放大倍数从而控制LTC2600 所对应通道的电压,以实现双通道放大倍数和偏置的控制。该文垂直系统幅值刻度调节范围为1~100 mV/div,共有七个档位,上位机垂直系统幅值刻度初始为100 mV/div,刻度值越大,放大倍数越小,具体对应关系如表1所示。垂直系统偏置调节范围为-500~500 mV,当LTC2600 的B 或D 通道输出电压为0 V 时,偏置为-500 mV,当B或D通道输出电压为2.5 V时,偏置为0 mV,当B或D通道输出电压为5 V时,偏置为+500 mV。

表1 DAC数据字与放大倍数对应关系

2.3 AD7367数据采集模块

由FPGA 驱动AD7367 数据采集模块对垂直增益放大电路调理后的中频信号进行同步采集,精密时基模块每隔20 μs 产生取样脉冲对被测信号进行取样[14],同时产生50 kHz 同步采样脉冲驱动AD7367的CNVST 信号开启模数转换,采集取样后的中频信号[15]。当BUSY 信号拉低产生下降沿,表示模数转换完成,FPGA 检测到BUSY 信号下降沿后拉低CS 使能信号,此时DOUT 数据线输出第14 位数字信号,SCLK 信号下降沿更新DOUT 数据线上的数据,FPGA 产生14 个SCLK 信号并在SCLK 信号上升沿时读取DOUT 数据线上的数字信号,直到读取完最后一位数字信号后拉高CS 信号,DOUT 数据线回到高阻态并等待下一次数据转换。

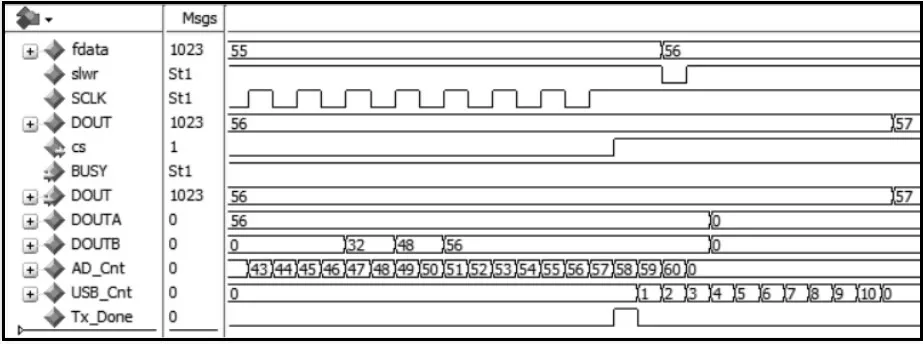

依据AD7367 的工作时序图对其进行仿真,仿真结果如图5 所示。当检测到BUSY 信号的下降沿后,AD_cnt 开始计数,线性序列机根据AD_cnt 的数值拉低CS 使能信号,并依次产生SCLK 信号读取AD7367转换完成的数字信号。最后,Tx_Done 拉高一个时钟周期,代表传输结束,CS 使能信号拉高。FPGA 将模数转换完成的数字信号分组存到SDRAM 中并通过USB2.0 发给上位机进行波形重构和分析。

图5 AD7367工作仿真图

3 实验验证与数据分析

3.1 上位机控制垂直增益放大电路阶梯放大

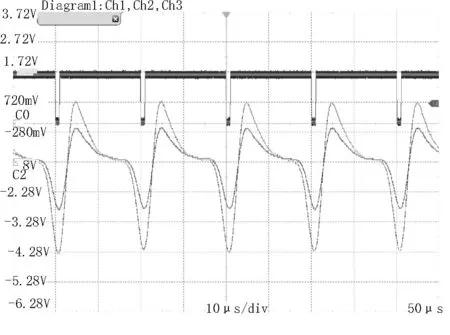

上位机启动USB Control Center(USB 控制中心),使用Control Center 将CY7C68013A 芯片配置为从设备FIFO 模式之后发送控制垂直增益放大电路阶梯放大的逻辑电平指令,指令用8 位十六进制数表示,逻辑指令更新到FPGA 后,由FPGA 识别指令然后配置LTC2600 从而实现对垂直增益放大电路进行控制,实现阶梯放大倍数。对其进行板级验证,将输入80 mV 的中频取样信号放大50 倍,信号经垂直增益放大电路输出幅值为4 V,如图6 所示。其中,被测信号经取样、滤波、放大后其幅值信息存在于正弦包络状信号的峰值位置[16],3 通道脉冲信号为同步取样信号,频率为50 kHz,脉冲信号的下降沿驱动AD7367 对正弦包络状信号的峰值位置进行采样,上位机根据采集到的数据、时基刻度和采样点数就可以重构出被测信号的频率和幅值。

图6 80 mV中频取样信号放大50倍

3.2 上位机接收采集数据

为了验证垂直电压增益自动比例控制电路性能,将设计的硬件电路和精密时基电路、脉冲压缩模块、中频滤波放大模块进行联调测试,实验采用的射频源为KEYSIGHT 的E8257D,示波器为ROHDE&SCHWARZ 的RTO2044 等仪器。

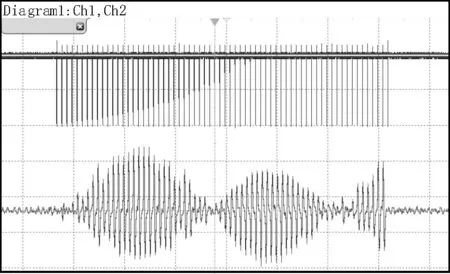

将整套硬件系统搭建好后,上位机设置精密时基模块步进延时为10 ps,取样点数为64,总延时范围为640 ps,每20 μs 产生一次取样脉冲,总取样周期为1 280 μs。被测信号输入2 GHz、200 mV 正弦信号,示波器测试波形如图7 所示,示波器时基刻度为每格200 μs,其中正弦包络状信号为垂直增益放大后的取样中频信号,正弦包络状信号的峰值位置包含着被测信号取样时的幅值信息,64 个正弦包络状信号依次组成2 GHz 被测信号。脉冲信号为同步取样信号,频率为50 kHz,脉冲信号的下降沿对应着正弦包络状信号的峰值位置并对其进行采样,并由上位机根据每次产生取样脉冲后的延时时间和采样点数将被测信号重构出来。

图7 被测信号为2 GHz时重构波形

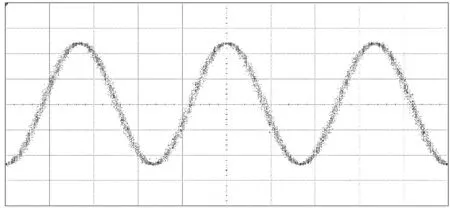

同理,上位机设置精密时基模块取样点数为8 192。被测信号输入5 GHz、200 mV 正弦信号,使用14 bit 两通道高精度同步采样ADC 芯片AD7367 对垂直增益放大电路的输出的正弦包络状信号进行采集,AD7367输入范围为-10~10 V,采集频率为50 kHz,FPGA 读取AD7367 转化完成的数字信号并分组存入到相应通道的FIFO 内,当FIFO 内存储的数据大于SDRAM 的突发长度时,FPGA 读取FIFO 内的数据以突发写的方式将数据存入SDRAM 中,然后进行相应的处理之后通过USB2.0 将数据传输到上位机。上位机对于上行数据进行转码处理和波形重构,其恢复波形如图8 所示。

图8 被测信号为5 GHz时重构波形

4 结论

该文针对垂直电压增益放大电路,使用FPGA控制垂直增益放大倍数、数据的采集与存储和USB2.0 与上位机进行双向通信,通过上述实验验证和数据分析得知,垂直电压增益放大电路的放大倍数误差小于2%,且放大倍数采用1、2、5 比例放大,具有更全面的覆盖范围,以保证ADC 位数尽量多的被使用,使得上位机恢复的波形更加准确。与此同时,FPGA 通过分析上位机指令灵活控制双通道数据存储长度,每个通道的采样点数为16~65 536 个,灵活的采样率能够根据不同情况捕获不同长度的波形,上位机能够分析信号中微弱的抖动或者毛刺信号,使得波形测试结果更加精确。