多主从模式高速仪器内部总线设计与实现

周建琼,李谦

(中海油田服务股份有限公司油田技术研究院,北京 101149)

随着测井行业的不断发展,成像类仪器信号采集数据量大,且信号节点数量多,节点之间数据交互和协同工作频繁且复杂,对仪器内部总线提出了更高的要求。根据485 总线电气标准特点,能够实现40 m 范围内10 Mbps 的数据传输速率,然而485 总线均为单主从结构[1],不能满足成像仪器内部各个节点实时发送采集数据以及节点之间快速协同工作和连贯反应的要求[2]。该文通过对485 接口硬件的优化,总线数据收发逻辑的改进以及定义全新的总线数据帧格式,设计一种多主从模式的高速仪器内部总线,满足成像类仪器内部总线的特殊需求[3-4]。

1 设计方案

多主从模式的高速仪器内部总线,要满足仪器设计中各个节点协同工作且快速反应的要求,需要允许每个节点都可以主动发送数据,且各个节点发送时机不受限制,则必须通过总线进行协调[5],以保证数据不错乱。该文引入地址信息、总线侦听和总线仲裁的设计思路[6-7],每个节点都定义唯一的地址信息,多个节点发送时,通过发送地址信息自动进行仲裁,这样就可以实现总线数据不错乱,而且一个节点发完,别的节点可以侦听到总线空闲,省去了主机的询问,提高了总线利用率,增强了总线节点响应的快速性和连贯性[8]。多主从模式总线设计主要包含四部分内容:接口硬件、总线数据帧格式、总线数据收发逻辑和地址信息分配。

1.1 接口硬件

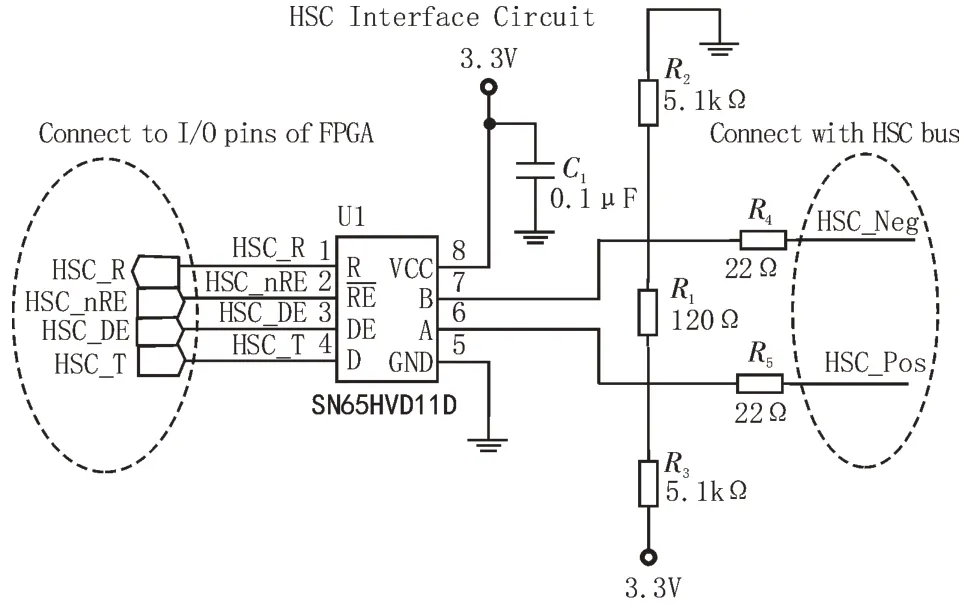

该文设计的总线以双绞线为介质,遵从ANSI TIA/EIA-485-A 和ISO-8482:1993 标准,实现标准的485 总线电气特性,数据发送逻辑方面完全参照数据帧格式以bit 为单位连续发送[9]。接口硬件主要包含485 接口驱动芯片和接口逻辑控制芯片,在器件选型上着重考虑芯片的功耗和耐温等性能指标,选择TI 的SN65HVD11D 芯片。总线接口采用平衡驱动器和差分接收器的组合,抗共模干能力增强,抗噪声干扰性好[10-11],接口控制逻辑芯片采用FPGA来实现,选择ACTEL 公司的A3P250VQG100 芯片作为接口逻辑控制芯片。其电路的参考设计如图1所示。

图1 总线驱动电路参考设计

电阻R1为通道匹配120 Ω电阻,该电阻只存在于总线两端的节点上;电阻R4和R5用于保护仪器内部总线通道,当该节点的硬件出现故障时不会使整个总线的通信受到影响,电阻R2和电阻R3保证总线在默认情况下保持一个确定的电平。

1.2 总线数据帧格式

数据通信中,在10 Mbps 的传输速率下,数据传输逻辑按照帧结构以bit 为单位连续发送,为了保证数据传输的可靠性,降低数据出错率,在总线控制逻辑中加入了8b/10b 编解码功能[12-13]。总线上的数据传输均以帧为单位,所有的类型的数据均需要严格按照帧结构组帧[14]。该文设计的数据帧格式,可以协助完成总线仲裁和竞争,其具体组成结构如图2所示。

图2 数据帧结构

总线数据帧长度不固定,但是为了确保单个节点不长时间占据总线,一帧最大可传输的数据长度最多为255 Bytes 数据,可传输的数据长度不足255 Bytes 数据时,只需要传输有效数据,每一帧的有效数据长度由该帧的数据长度字段指示。帧格式包含两层,数据层和编码层。数据层主要包含帧目标段、帧标识段、帧长度段、帧数据段和帧校验段,编码层对数据层以8 bit 为单位进行8b/10b 编码,然后添加帧头、帧地址段和帧尾组成完整的数据帧格式。帧格式中各个字段的功能如下:

1)帧头——低电平信号,默认高电平,高低跳变沿标识数据帧开始;

2)帧地址段——仪器信号采集节点自身地址信息,作为总线竞争优先级判断条件,借助地址段实现总线仲裁的功能;

3)帧目标段——总线数据发送目标节点地址信息,作为节点是否接收数据判断条件;

4)帧标识段——帧内数据类型和数据帧状态信息,包含单包、多包数据标识,首包、中间包、末包数据标识,重传帧标识,重传次数统计标识等;

5)帧长度段——帧内数据层有效数据长度,以字节为单位;

6)帧数据段——信号采集单元的数据体;

7)帧校验段——帧数据层有效数据体的CRC 校验,辅助判断数据是否正常接收;

8)帧尾——采用8b/10b 编码中的K28.1 字符即“1001111100”,该字符在编码规则中具有唯一性,可有效避免假帧结束[15-16]。

总线一次完整的数据帧传输格式图3 所示。

图3 总线一次完整的数据帧传输格式

在发送节点发完当前帧的数据后,必须收到接收节点一个确认信号后,才确定该帧数据已经发送正确,接收节点每接收到一帧数据后产生一个确认信号。确认信号需要迅速响应,该文设计总线确认信号产生时间在接收完当前帧的帧尾后10 个bit 传输时间内产生,确认信号同样为K28.1 字符。

对于发送节点,每当发送端发送完一帧数据据后立即关闭发送端,释放总线,在接下来的20 个bit传输时间内,当成功接收到K28.1 字符表示该帧数据已经成功发送,未接收到则表示发送失败,该帧数据需要重发。接收到确认信号帧之后,完整的一簇数据帧传输格式才结束。

每个节点接收到确认信号后要至少延迟20 个bit 传输时间再发送下一帧数据。总线空闲的判断条件也是连续20 个bit 传输时间的高电平信号。从而保证各个节点公平的占用总线,且能够按照预先设定的优先级进行连贯工作。

1.3 总线数据收发逻辑

总线数据收发逻辑在接口硬件逻辑芯片FPGA中实现,通过总线收发逻辑的设计和总线节点地址信息的固化,完成总线侦听和总线仲裁功能,实现多主从模式。总线数接收流程起始于监测到总线帧头,即高低跳变沿。开始接收10 位帧地址段和10 位帧目标段。接收节点可以与帧目标段直接对比,判断是否为发往该节点数据,如果不一致,则重新返回到空闲监测;如果一致,则接收所有数据,将接收到的帧进行8b/10b 解码,CRC 校验通过后发送确认帧,并存储处理数据,CRC 校验失败则返回到空闲监测;空闲检测环节需要监测到总线空闲才返回数据接收起始位置,数据接收逻辑流程如图4 所示。

总线数据发送起始于信号采集单元,受控于总线状态,数据发送逻辑流程如图5 所示。

多主从总线不可避免存在节点竞争现象,硬件接口和逻辑设计中增加了FIFO 缓存区域,作为总线发送的缓冲,可以保证节点数据的连续性。发送时首先判断FIFO 缓存是否满,如果缓存已满,则等待,如果未满,则取出数据完成组帧,交给数据控制逻辑。数据控制逻辑负责数据流控制,根据该节点数据发送状态和总线空闲状态,判断是否发送数据,如果总线空闲,则开始帧目标段8b/10b 编码,发送帧头和固化于接口硬件的10 位帧地址段开始竞争总线。根据总线特点,所有节点均可以接收到总线数据,该节点也可以接收到帧地址段,与该节点固化地址段对比,如果一致,则竞争总线成功,如果不一致,则总线被其他节点竞争到。总线竞争成功后开始发送数据帧,然后等待返回确认,如果返回确认帧,则延时后准备下一帧数据发送;如果没有收到确认帧,则重复发送本帧数据,连续发送3 次不成功,则放弃此帧数据。如果总线竞争失败,继续监测总线,当总线空闲时再次竞争总线使用权。

图4 总线数据接收逻辑图

1.4 总线地址信息分配

总线节点地址信息将8 位地址以8b/10b 编码后规则进行地址填充,固化到接口硬件FPGA 中,每个地址均具有唯一性,其在接收逻辑中作为节点是否接收总线数据的判断依据,在发送逻辑中作为总线竞争的工具。通过硬件接口设计电平特性,可以实现10 位地址信息数值越小优先级越高。

2 调试与验证

为了验证总线多主从工作模式,设计制作了5 块接口电路板,5 个电路均连接在总线上,每个节点分配了不同地址,为方便测试每块电路板通过串口连接一个上位机,同时上位机4 连接2 个接口电路,用于测试总线数据发送逻辑的竞争机制,如图6 所示。测试过程中,在上位机中输入目标节点地址和任意字长的数据,即可将数据发送到目标节点,且在目标上位机中显示。实验证明,该设计总线可以实现每个节点都作为主节点发起数据传输,且按照地址设置优先级竞争发送数据的多主从模式,数据传输效率高,总线节点响应快速、连贯。

图6 测试示意图

3 结论

该文设计的多主从工作模式其特点在于多个节点可以自主发送数据给任意一个节点,这种总线可以实现仪器内部各个节点之间按照预先设计的流程协同合作,让各个信号采集单元的采集工作更加灵活,相互之间的配合更加自由,并且可以通过主控节点的调度随时改变工作模式,且能够达到10 Mbps 的传输速率,完全满足成像类仪器内部信号采集单元之间总线通信和协同工作的要求。