心电信号监测轻量化残差神经网络硬件IP 设计

谢文鑫,史纪广,李宙童,黄启俊

(1.武汉大学物理科学与技术学院,湖北武汉 430072;2.上海交通大学医学院附属第九人民医院黄浦分院,上海 200011)

心血管疾病(CardioVascular Disease,CVD)是人类身体健康的首要威胁,具有发病率和死亡率高的特点,已成为重大的公共卫生问题[1],对其预防和诊断也越来越受到人们的重视。心电图[2](Electrocardiogram,ECG)包含有各种心血管疾病的细微信息,是CVD 诊断的重要依据。随着机器学习的发展,神经网络算法逐渐应用于心电信号的自动识别[3]。因此,采用人工智能算法对ECG 信号进行自动分析,并将智能算法移植到便携式心电检测设备,实现大众心脏健康的日常监护,成为一个亟待解决的问题。文中设计了一种适合硬件实现的轻量化残差神经网络结构,将其硬件化部署于FPGA 平台上,并验证该模块的效果。该硬件IP 模块具有准确率高、计算速度快的特点,易于硬件实现,可满足便携式心电检测系统的需求。

1 数据来源及处理

1.1 数据来源

数据库样本来源于上海某医院心内科实际采集的心电图,包含有七万多名被检测者的心电图,为12导联的完整心电数据,采样率为1 000 Hz。通过对被检测人的信息进行脱敏保密处理,心电图数据只保留了信号波形和对应的疾病标签。每个样本都由专业医生进行疾病诊断并做出标注,标注的诊断结果包含46 种心电信号类型,如正常心电图、右心房扩大、左心室肥大、房性早搏、心动过速、心动过缓等。考虑到实际需求,文中主要对其中的心律失常疾病进行分类,因此选取了其中的正常心电图(N)、房性早搏(A)、心动过速(T)、心动过缓(B)四种CVD进行分类[4]。由于一个样本可能同时包含两种以上的CVD类型,例如一条样本含有房性早搏和心动过缓两种疾病,所以文中选择只包含四类独立CVD 疾病类型的心电数据。为满足分类算法硬件的轻量化要求,文中只使用了Ⅱ导联数据进行心律失常的检测。

1.2 数据预处理

心电信号是一种微弱的生物信号,易受各种环境因素的影响,所以原始心电信号会包含基线漂移、工频干扰、肌电干扰等噪声[5]。根据美国心脏协会的建议,文中采用0.5~150 Hz 的带通滤波器对原始信号进行去噪[6]。

由于每个心电图样本的长度不固定,时间长度从11 s到92 s(即包含的采样点数量为11 000~92 000个),因此要对心电数据进行片段分割处理。为了保证每个片段具有足够的心电信号特征,将心电信号分割成固定长度为9 000 个采样点的数据:

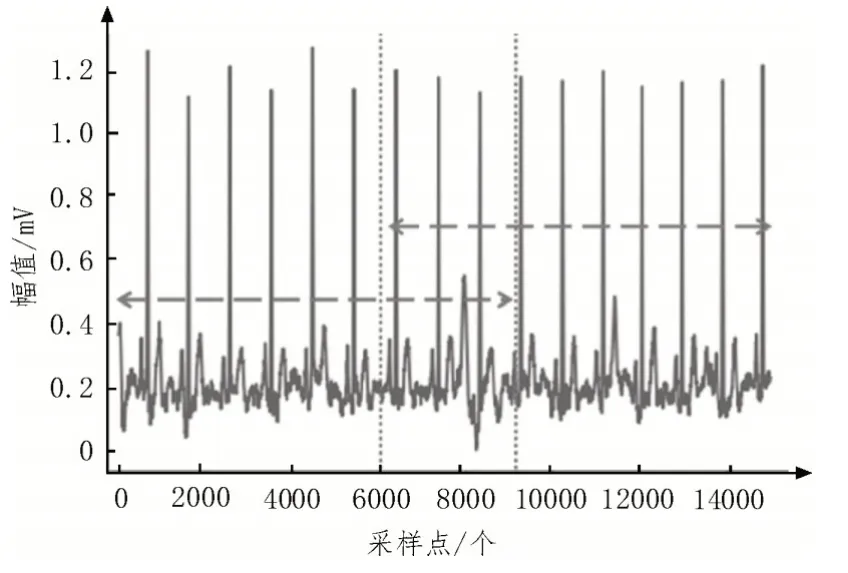

其中,num_sigment 为样本切割后得到的片段数量,L0为原始样本的长度。一条包含15 000 个采样点的样本数据可以被切割为两段9 000 个采样点的心拍片段,如图1 所示,切割后的每个片段包含9 s 的信息,标签与原始样本的标签相同。

由于数据库的数据采样率为1 000 Hz,因此在保证足够信息和分类精度的前提下,对切割后的心拍片段进行了降采样处理,将每段包含9 000 个采样点的片段重采样成1 000 个采样点,即将9 s 的心电信号表示为1 000 个采样点的数据。

图1 心电信号片段分割

将原始心电信号经过上述预处理,得到尺寸为1 000×1 的输入数据。其中,各类心电信号处理后的样本量如表1所示,共计11 358个心拍片段,按照8∶1的比例划分训练集和测试集。

表1 各类片段样本量及训练集、测试集样本量

2 残差神经网络模型设计

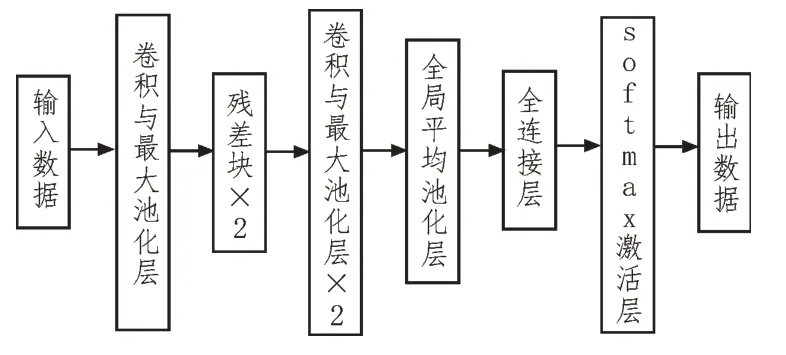

原始的Ⅱ导联数据经过去噪、片段分割、重采样处理后,输入神经网络对心律失常进行疾病分类检测。神经网络结构如图2 所示,输入的心电信号经过神经网络后得到4×1 的输出数据,使用Softmax 作为输出层的激活函数,输出四个类别分别对应的概率,将概率最大的类别视作分类的结果。

图2 神经网络结构

残差神经网络(Resnet)[7]由何恺明等于2015 年提出,其中残差模块如图3(a)所示,将Resnet 信息绕道传输到输出端并将二者叠加,使输出信息更加完全,在一定程度上解决了深层网络的梯度消失或梯度爆炸问题[8]。文中在此基础上提出了一种改进的残差模块,该模块由卷积层、最大池化层和激活层组成,信号经过该残差模块可以缩小最大池化层对应的尺寸,有利于模块硬件化时降低资源的使用,如图3(b)所示。

图3 残差模块与改进

图2 所示的Resnet 输入数据尺寸为1 000×1,使用卷积层、最大池化层、残差模块、全局平均池化层提取特征,并用全连接层和Softmax 激活函数进行CVD 的检测分类。

基于Python 语言(v3.7)和TensorFlow(v2.4.1)深度学习框架完成网络模块设计,使用Nvidia RTX 3060进行训练和神经网络测试。测试结果的混淆矩阵如表2 所示,横向为真实值,竖向为预测值。可由混淆矩阵计算得出分类准确率及F1-Score。F1-Score 为分类任务的一个重要衡量指标,是精确率和召回率的调和平均数,最大值为1,最小值为0,F1-Score 数值越大,则分类效果越好。

表2 混淆矩阵

经过计算,分类准确率为91.22%,N、A、T、B 四类心电信号的F1-Score 分别为91.70%、88.38%、93.97%、91.34%,均达到了90%左右,该网络模型对于心律失常的误诊率较低,可满足人们日常心电监护的需要。

3 残差神经网络硬件IP模块设计

使用Xilinx 公司的HLS 设计工具——高层次综合(High-level Synthesis,HLS)对残差神经网络模块进行硬件IP 设计[9]。将基于C/C++语言编写的源代码和仿真测试代码导入HLS 设计工具中,可进行代码层面的C 仿真,验证算法功能的正确性。利用约束指令、优化指令进行综合约束和优化[10],C 综合器可以将C/C++软件代码综合成寄存器传输级(Register-Transfer Level,RTL 级)的硬件,综合完成之后进行硬件层面的RTL/C 联合仿真,进一步验证硬件IP 设计的正确性,仿真正确之后就可以将设计封装为硬件IP,用于Vivado 设计工具中搭建硬件系统。

3.1 数据量化

在keras 中,训练的参数被保存为浮点类型,单精度浮点数在硬件中需要用32 位二进制数表示,数据位宽越高将会耗费巨大的硬件资源[11]。在满足精度要求的前提下,选择合适的位宽进行数据量化,将会减少硬件资源消耗并显著提高硬件计算速度[12]。所以选取16 位有符号定点数对数据进行量化,小数位宽越大,精度越高,但小数部分的位宽过大会导致整数位数据溢出。最后文中定点化设计方案为:一位符号位,七位整数位,八位小数位。

3.2 硬件模块设计

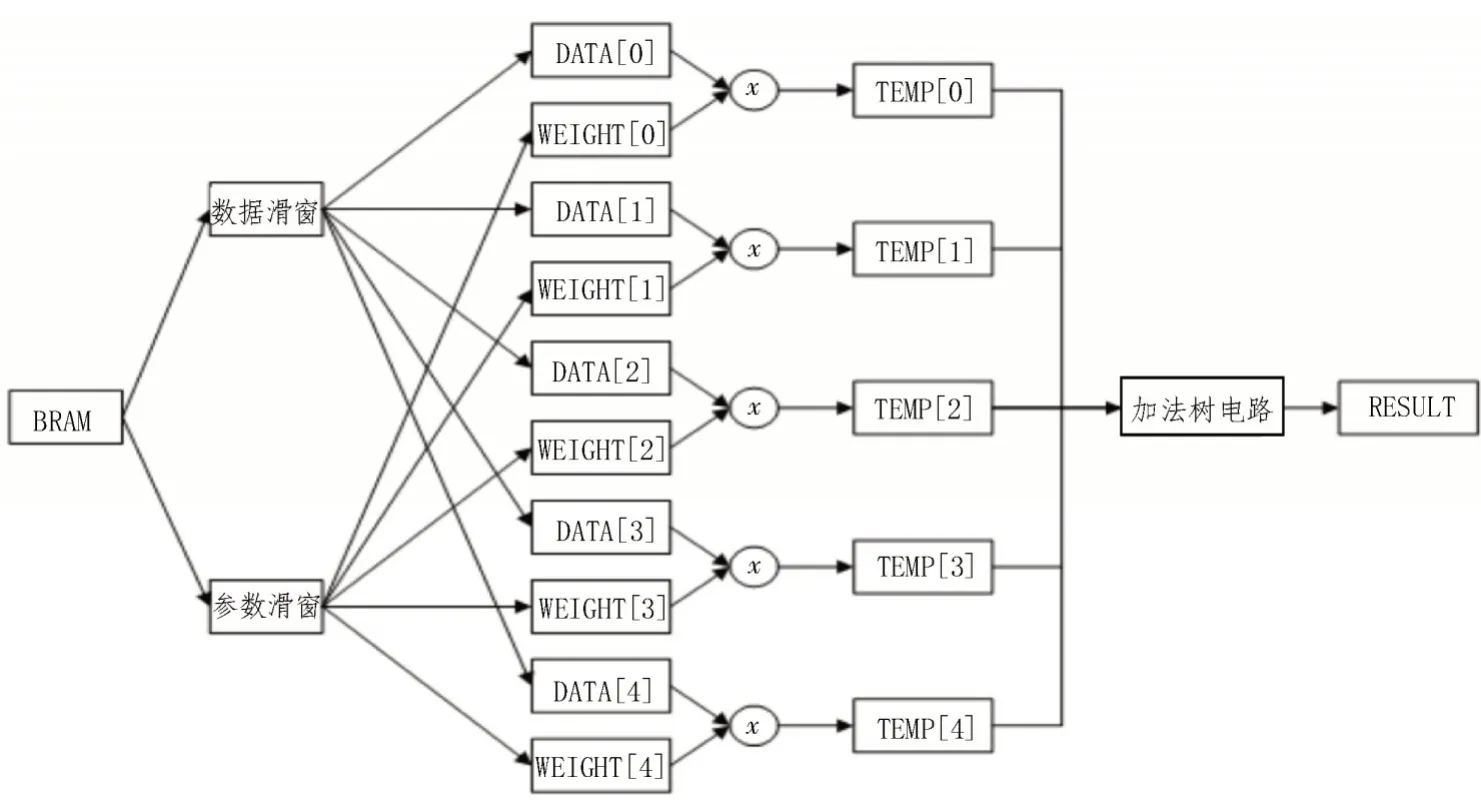

神经网络算法的计算过程复杂,卷积层是网络结构的核心,也是设计的重点。心电信号是一维时间序列信号,与常用于图像处理的二维卷积相比,一维的卷积模块会显著降低硬件模块设计的复杂度[13]。图4 所示为文中一维卷积运算的过程。首先将储存在BRAM(Block Random Access Memory)中的数据和权重参数读取到数据滑窗和参数滑窗,通过乘法器使两个窗口对应位置数据相乘,将乘法运算的结果输入到加法树电路中,便可得到一次卷积运算的结果。整个卷积层的计算包含了四层循环,用来控制数据和权重参数的读取及计算过程。在输出通道和输入通道的循环操作上,添加Unroll 优化指令作并行展开,可提高模块计算速度[14]。对于第一层卷积层,输入通道数为1,所以只在输出通道上展开,设置并行度为8;对其余卷积层,输出通道和输入通道并行度均设置为4。

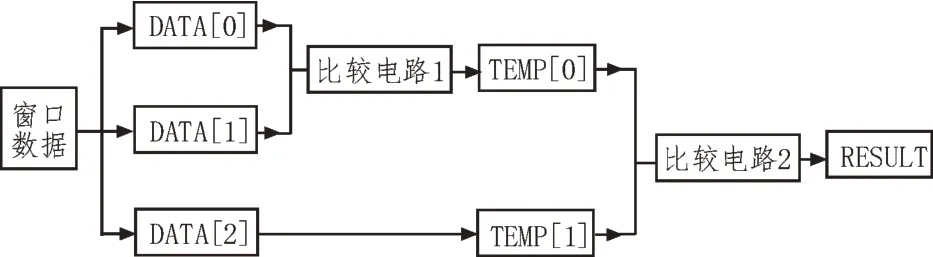

池化层的结构比较简单,只需要池化窗口在输入数据上滑动一遍,便能得到输出数据。文中使用的池化函数均为最大池化,池化窗口的宽度应和池化的步长保持一致,用到的池化步长为2 和3。对于步长为2 的池化层,只需要一个比较器便可以实现最大池化,步长为3 的池化则需要两级比较器来实现。图5 所示为步长为3 的最大池化窗口结构。

图4 卷积计算过程

图5 最大池化窗口

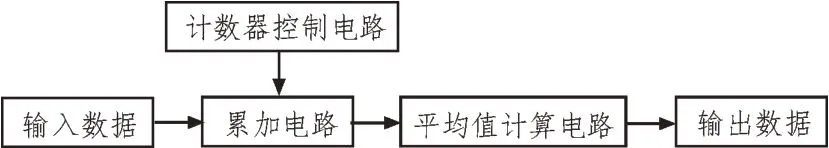

全局平均池化层设计方法和最大池化层类似,计算过程如图6 所示。将输入数据输入到累加器电路中进行累加,累加的次数通过计数器电路控制,最后将累加的运算结果输入到平均值计算电路中进行运算,得到全局平均池化的结果。

图6 全局平均池化计算过程

全连接层计算量较大,计算过程与卷积层类似,但是循环层数较少。全连接层的输入数据经过Flatten 操作,可看成每个输入通道只有一个数据,每个输出通道也只会得到一个数据结果,因此只需要两层循环即可完成。

残差神经网络各层设计好后,根据网络结构完成硬件模块连接,使用Dataflow 优化指令对网络进行优化[15],使数据以数据流的形式在各层之间流动,实现各层的流水线操作,有效地提高了网络的吞吐率。模块使用AXI_M 数据接口,实现与ARM CPU 的数据交互。经过C 仿真、RTL/C 联合仿真,模块均能得到正确的计算结果,最后将模块封装成IP。

4 硬件系统搭建

4.1 硬件平台选择

文中使用米联客MZ7XA-7020 FPGA 开发板对算法进行硬件部署验证,该板卡体积小、资源相对丰富且灵活度高,适合开发便携式设备。

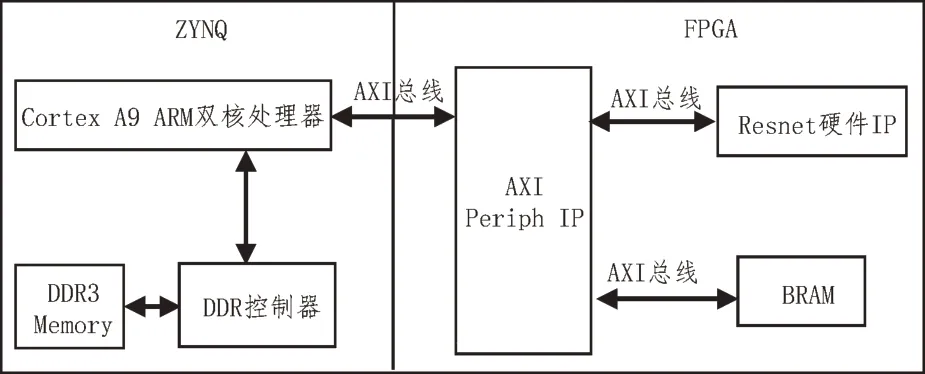

4.2 硬件部署

将设计完成的硬件模块导入到Vivado 设计工具中,搭建图7 所示的硬件系统,用于该模块的验证。整个系统可分为ZYNQ 和FPGA 两个部分[16],FPGA的核心是Resnet 硬件模块,用硬件实现心电信号的自动识别;ZYNQ 的核心是ARM 处理器,负责运行整个系统的控制程序。Resnet 模块和ARM 之间的数据交互则通过AXI 总线完成[17]。系统中的BRAM 模块用于数据的存储,Resnet 硬件模块和ARM 处理器可以通过AXI 总线对BRAM 进行数据的读写操作。整个系统的时钟在ZYNQ 中设置产生,并提供给其他模块使用。

图7 硬件系统框图

4.3 结果分析

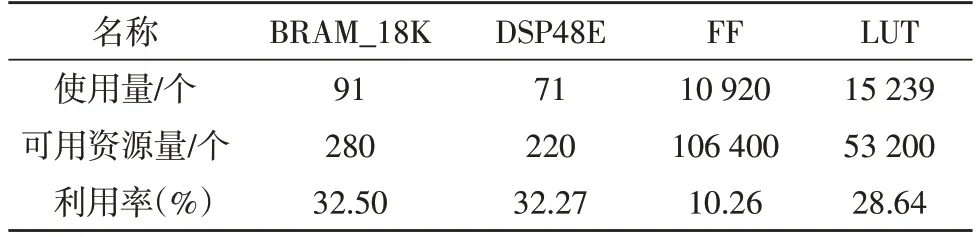

模块硬件资源的使用情况如表3 所示,BRAM、DSP48E、FF(Flip-Flop)和LUT(Lookup Table)使用率分别为32.50%、32.27%、10.26%和28.64%。可看出IP 模块对四种硬件资源的使用均未超过可用资源量的三分之一,剩余的硬件资源供ECG 系统的其他模块使用,可以满足便携式心电检测系统小型化的要求。

表3 资源占用情况

性能分析如表4 所示,表中记录了硬件IP 模块处理完1 264 条数据的总时间和每条数据的平均时间,并与在ARM Cortex-A9 CPU 中用纯软件模式实现运行的计算时间进行对比。从表4 可以看出,在100 MHz 的时钟频率下,处理同样一条心电数据,硬件IP 模块的速度是ARM CPU 纯软件实现速度的2.07 倍。

表4 FPGA与ARM CPU计算时间比较

在FPGA 嵌入式平台对文中Resnet 网络模型进行测试,输入测试集1 264 条心电数据,将测试结果与keras 框架下的网络测试结果相比较,其中,5 条数据输出结果与软件结果不一致,硬件计算的准确率达到了99.60%。

表5 FPGA计算准确率

5 结束语

文中针对实时心电数据的自动分类识别,设计了一种适用于便携式心电检测的残差神经网络硬件IP,可实现正常心电图、房性早搏、心动过速、心动过缓四种心电信号的分类,分类准确率分别达到87.31%、89.40%、97.39%、95.24%。在FPGA 上搭建硬件系统,完成了硬件IP 模块的验证,与软件计算结果相比,速度提升2 倍以上;且硬件资源消耗较少、准确率高,能够满足便携式心电检测系统的要求,具有实际应用价值。未来将用更大的数据集进行验证,进一步提升算法的普适性。