提升精细线路蚀刻良率的方法探讨

李君红

(上海美维科技有限公司,上海 201613)

0 引言

随着电子产品越来越向着轻、薄、短、小的方向发展,封装基板图形密度越来越高,线路的线宽间距越来越细,互连孔的直径也越来越小,对封装基板的制程能力提出了更高的挑战。在精细线路的制作过程中,传统的减成法因成本低、设备投资小而被广泛使用[1-5]。

在减成法的蚀刻工艺中,侧蚀是无法避免的问题[6-11]。其成因是蚀刻药水在进行深度方向蚀刻时,不可避免地与水平方向的金属层发生反应,抗蚀层下面的导线侧壁被蚀刻,使线路的形状发生改变,影响线路精度。由于侧蚀造成线路的线宽、线间距与设计图形的要求不完全一致,针对侧蚀现象,目前通用的解决措施即在图形设计时,采用均匀曝光补偿的方法设计线宽和间距。但由于电镀铜厚、干膜曝光显影、蚀刻线的均匀性问题,采用该方法已不能使整板每个单元的线宽间距均匀一致。

本文主要研究电镀铜厚、干膜显影、蚀刻线的均匀性对良率的影响,找出线宽的分布与测试板的电镀铜厚度、显影后干膜宽度及蚀刻均匀性之间的关系,并根据实测结果,修订优化非均匀的线宽曝光补偿值。最终在20 μm 铜厚下使25/25 μm 线路的局部良率和整板良率得到大幅提升,整板所有单元的线宽间距均匀性得到较大改善,均接近设计目标值25/25 μm。

1 实验部分

选用叠构为4 层的测试板,主要流程为:芯板棕化处理→层压介质层和铜箔→电镀→贴膜→曝光→显影→蚀刻→检测。

图形设计为每块在制板上有6 个单元,如图1所示。每个单元里均设计有25/25 μm、30/30 μm、35/35 μm 的线路,铜厚为20 μm。图形制作完成后,测试线路开路/短路良率和检查缺陷。

图1 测试板图形示意

2 结果与讨论

2.1 蚀刻后线路良率的收集

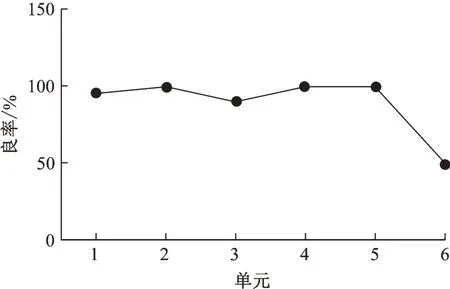

收集整板的开路/短路良率数据如图2所示,25/25 μm 良率仅88.26%,与其他线宽相比良率较差。良率缺陷原因主要为开路和短路。

图2 整板开路/短路良率

继续分析25/25 μm 在整板不同位置的良率,如图3所示。由图可知,单元6 位置的良率仅50%,其他位置的良率均在90%及以上。因此良率损失主要来自单元6位置。

图3 不同位置25/25 μm良率

分别对单元1、单元3、单元6 的3 个位置抽样检查线宽间距后发现,线宽整板分布不均匀,所有线宽设计均在单元6 位置偏细。线宽间距设计越小,不同位置间差异越大,25/25 μm 差异性最大,最宽位置单元3与最细位置单元6的线宽平均相差8.5 μm,如图4所示。

图4 线宽分布

2.2 良率影响因素的分析

通过对蚀刻后整板不同单元位置的线宽平均值进行分析,超过3 μm 会影响线路宽度的过程性能指数(performance of process index,Ppk)以及在局部区域出现线路过细;对于25/25 μm 此类精细线路就会影响良率。出现此问题的原因一般有以下3 个方面:① 电镀时,由于电力线的分布及药水能力等问题,电镀的均匀性有一定差异,使得铜厚度不一致。经过蚀刻后,镀层厚度大的地方会出现线间距小而线路宽的现象,镀层厚度小的地方会出现线间距大和线路窄的现象;② 干膜曝光显影中由于曝光和显影的不均匀性,使得干膜宽度在整板不均匀,导致蚀刻后线路宽度间距不均匀; ③ 蚀刻线的均匀性会因喷嘴的压力、上下面的药水交换速度的差异等,使不同位置蚀刻能力不同,导致线路宽度间距不均匀。针对以上3个方面对本次实验进一步分析。

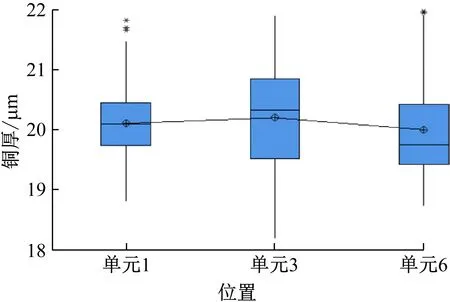

(1)电镀铜厚度对良率的影响。分别抽样收集单元1、单元3、单元6 的3 个位置铜厚度数据,结果如图5 和表1所示。通过minitab 分析,P值>0.05,3个位置的铜厚度无明显差异。

表1 方差分析

图5 电镀后铜厚均匀性

结论:在本实验中,采用目前的电镀参数,对于蚀刻本身没有明显差异。

(2)干膜显影的均匀性对良率的影响。抽样收集曝光显影后单元1、单元3、单元6干膜宽度的数据,结果如图6 和表2所示,通过minitab 分析,P值>0.05,6个位置的干膜宽度无明显差异。

图6 显影后25/25 μm干膜宽度均匀性

表2 方差分析

(3)蚀刻线均匀性对良率的影响。采用70 μm 厚铜板对蚀刻线的蚀刻能力进行分析,结果如图7所示。由图7 可知,在蚀刻线的不同位置,蚀刻能力有一定差异。其中单元6 位置的蚀刻能力最强,导致6 位置的线宽较细,算出蚀刻均匀性为91.24%。用单元1 和单元3 的数据统计,得到均匀性为96.58%。如25/25 μm 线宽要得到较好的良率,则需蚀刻均匀性数据大于96%。尝试调整蚀刻线的蚀刻均匀性,但因蚀刻线固有的一些问题,仅可提高至92.89%。如需提高至96%以上,还需大量经费对设备进行改造,因此短期内,蚀刻均匀性不能明显提升。

图7 蚀刻均匀性

对图5~图7 中电镀铜厚、干膜显影、蚀刻均匀性的分布进行分析,得出本次实验中,蚀刻均匀性是影响良率的主要因素,且主要为单元6 位置的蚀刻能力和其他位置差异较大造成。

2.3 良率提升的方法

在蚀刻工艺中,目前通用的方法是在图形设计时,采用均匀曝光补偿的方法设计线宽和间距。该方法对于较宽的线路良率影响不大,但如要做25/25 μm 这种精细线路,电镀铜厚、干膜显影、蚀刻线的均匀性就会对良率和整板线宽间距的一致性产生影响。特别是蚀刻线的均匀性,很难在短时间内改善到精细线路制作的目标96%以上。

因此,在制程稳定情况下,可采用非均匀补偿法来提高减成法的良率及线宽过程能力指数(complex process capabilityindex,Cpk)。具体方法为:① 选用固定的电镀线,测量被电镀基板上的镀层厚度,获得基板上不同区域镀层厚度分布图;② 搭配固定的曝光、显影和蚀刻线,规定放板规则,采用均匀补偿的方法进行初步蚀刻,直到获得初始的最优线宽间距及线宽分布图;③ 将电镀后建立的铜厚分布图、显影后干膜宽度分布图及厚铜板蚀刻均匀性分布图进行匹配,与蚀刻的线宽分布图进行对比;④ 找出线宽的分布与测试板的电镀铜厚度、显影后干膜宽度及蚀刻均匀性之间的关系,并根据实测结果进行线宽补偿值的修订。这种修改补偿是特定位置单元的补偿值,并非每个单元的补偿都做同样的图形设计资料修改。如图1图形设计中,总共有6个单元,可将单元6 左侧的单元1 到单元5 所有单元补偿值不变,仍为补偿1,针对单元6 位置单独进行补偿值的修改,记为补偿2。也可根据需要针对6 个单元做6个单独的补偿值。

本次实验结果发现,良率及线宽偏细的问题主要在单元6 位置存在。通过对电镀铜厚、干膜显影、蚀刻均匀性的分布图分析得出蚀刻均匀性是主要影响因素,且主要是单元6 位置的蚀刻能力和其他位置差异较大造成的。因此可着重优化单元6 位置的曝光补偿,提高25/25 μm 精细线路的良率及线宽一致性(补偿值的设定需要考虑曝光机的解析能力,补偿后不能超出曝光机的解析能力)。

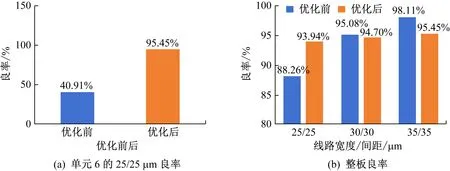

通过实验,得出结果如图8所示。25/25 μm单元6 位置的开路/短路良率从40.91% 提升到95.45%,整板的开路/短路良率从88.26%提升到93.94%。线宽优化前后比较结果见表1。由表1 线路可知,优化前单元6 位置线路宽度偏细,优化后3 个位置的线宽间距都接近于设计目标值25 μm,线宽一致性得到较大提升。

图8 曝光补偿优化前后良率比较

表1 线宽优化前后比较

续表1

3 结语

本文针对减成法制作精细线路中存在的生产板在部分区域良率表现较差的情况,研究了电镀铜厚、干膜显影、蚀刻线的均匀性对精细线路良率的影响。实验结果表明:线路宽度整板面不均匀是由于蚀刻不均匀引起的。根据实测结果进行非均匀的线宽曝光补偿值的修订优化,最终在20 μm 铜厚下使25/25 μm 线路的局部开路/短路良率从40.91%提升到95.45%,整板的开路/短路良率从88.26%提升到93.94%。优化后整板抽样3 个位置的线宽都接近于设计目标值25 μm,线宽一致性得到较大提升。