硅转接层高带宽存储互连通道信号完整性设计及仿真*

李 川,郑 浩,王彦辉

(江南计算技术研究所,江苏 无锡 214083)

1 引言

随着大数据、云计算、智能计算和高性能计算领域的飞速发展,芯片存储带宽需求急剧增加,尤其是T Byte/s(1E12 Byte/s)带宽需求。为了缩小存储带宽与芯片计算性能之间的差距,动态随机存储架构(DRAM)的I/O速率逐年增加,DDR5规范中I/O最高速率达到6.4 Gbps,GDDR6产品最高速率达18 Gbps。但是,对于T Byte/s带宽需求,DDR5所需 I/O数量大,封装以及存储颗粒布局难以解决,GDDR6实现T级存储带宽,其匹配带宽的颗粒数量与可靠的高速并行互连难以兼得。由此,基于3D堆叠且具有超高位宽的HBM(High-Bandwidth Memory)存储技术发展迅速。

为了实现HBM存储颗粒与CPU/GPU芯片之间的高位宽信号互连,需要引入超细线宽和间距的转接板,常规的封装基板和印制板互连密度难以满足需求[1,2]。目前,硅基转接板工艺相对于有机和玻璃转接板更为成熟,并且布线更灵活,硅基转接板是HBM颗粒和CPU/GPU芯片之间互连的主流介质[3]。

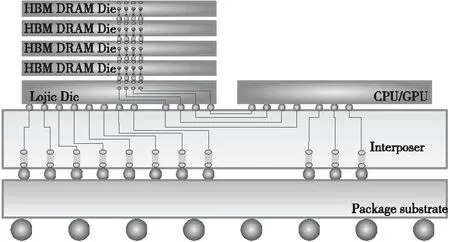

硅转接板中,HBM相关的物理传输路径如图1所示分为2类。一类是HBM与芯片之间的信号互连,包括8个通道的数据组信号和地址组信号,以单端信号为主,分布在硅转接板的RDL(ReDistribution Layer)。另一类是HBM相关的电源和地信号以及少量的外测试信号,贯穿整个转接板,通过微焊球与封装基板和印制板连接。本文主要分析HBM与芯片之间互连信号的电传输特性,属于第一类。

Figure 1 HBM structures and its signal interconnection图1 HBM结构及其信号互连示意图

硅转接板不同于常规的封装基板和印制板,其硅基损耗特性明显,微小尺寸的阻抗特性特殊,经典的印制线阻抗近似理论不再适用。韩国科学院的Heegon Kim团队基于早期HBM产品的信号互连作了大量的仿真分析[4 - 7],国内专家学者也在持续关注转接板上的多种信号传输特性[8,9]。但是,随着HBM颗粒升级到HBM2E的3.2 Gbps,接口电平降至1.2 V,这对于微Bump细节距条件下的串扰、损耗控制是极大的考验,有必要针对新的应用环境对互连传输通道的信号完整性进行深入研究。

2 结构分析

根据固态技术协会关于HBM的最新规范[10],单HBM存储颗粒与芯片互连信号共8组,约1 800个。每组代表一个信号传输通道,有独立的数据组信号和地址组信号。8组信号用后缀a,b,c,d,e,f,g,h区分,a~d组信号管脚从上至下沿颗粒长边一字排开,e~h组管脚与a~d组管脚并列。

无论是2颗粒HBM还是4颗粒HBM与芯片互连,沿颗粒长边平行方向放置颗粒和芯片可以最大程度增加同信号层布线数量。如果信号盘引出空间允许,2个信号层即可实现8组信号互连,a~d组通道信号同层,e~f组信号布设在另一层。

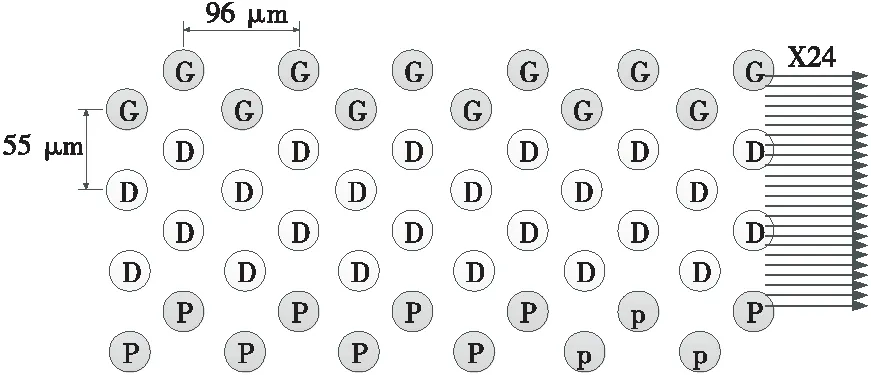

每通道包括16字节数据信号和一组约20 Pin的地址信号。2字节共24 Pin数据信号为一个管脚阵列单元,通过上、下2排电/地信号与其它单元进行分隔。地址信号阵列与2字节数据信号阵列类似。

通道内部2字节信号管脚排布如图2所示,24 Pin信号在图中用字母D标识。最上一排管脚是地管脚,最下一排管脚是接口电源管脚。假设芯片位于右侧,HBM颗粒位于左侧,24个信号同时向右侧引出,瓶颈位置在最右列的电、地管脚之间,粗略估算,每个信号可以利用的空间为55*3/24 μm,即6.875 μm。也就是说单根信号线宽度及信号间距之和小于6.8 μm时,2个信号层可以满足布线的引出需求。

Figure 2 HBM signal ball-map and line distribution图2 信号管脚及布线引出空间示意图

根据上述分析,总共的1 800 Pin信号分2个信号层布设,单层信号个数为900,沿颗粒长边方向布线宽度约为900*6.8 μm,即6.1 mm。互连线长度可以用存储颗粒最内层信号管脚距封装壳边沿距离加上芯片外管脚距芯片封装壳边沿距离估算,约为4.6 mm+1.5 mm,即6.1 mm。单HBM存储颗粒与芯片互连布线区域面积估计为6.1*6.1 mm2。

3 模型设计

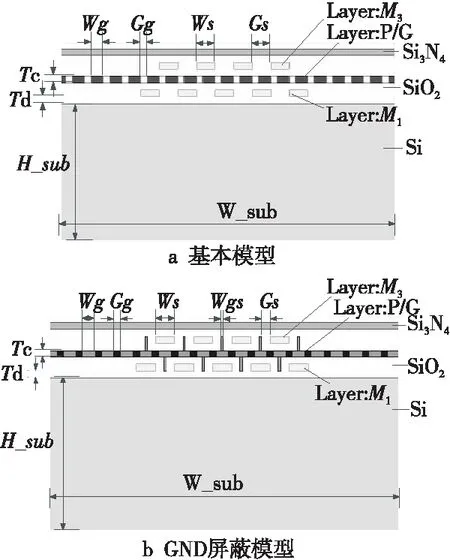

2个信号层的互连通道仿真模型如图3所示。图3a中,从下至上依次是硅基板、二氧化硅层、信号层M1、二氧化硅层、电地层、二氧化硅层、信号层M3、二氧化硅层和氮化硅层。图3b与3a叠层结构相同,不同的是,M1层和M3层的信号线之间加入了地屏蔽线。由此,用基本模型和GND屏蔽模型将二者进行区分。

Figure 3 Simulation model图3 仿真模型

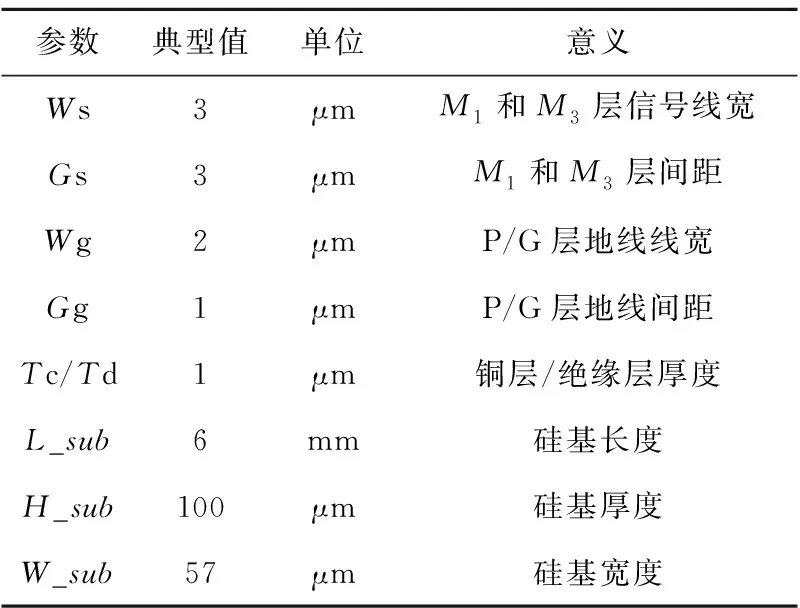

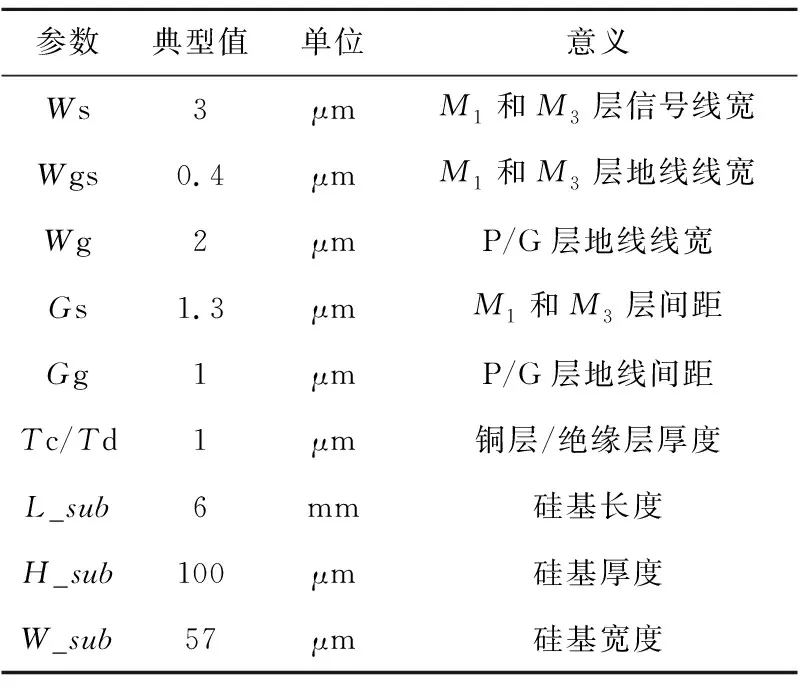

基本模型的参数类别及其意义如表1所示,屏蔽模型参数类别及意义如表2所示。电地层,即图中的P/G层采用栅格结构,所以也具有线宽和间距2种参数。栅格结构便于硅基铜工艺制造,同时对于近硅层的线损耗起到抑制作用。2种模型中材料参数相同,如表3所示。

Table 1 Parameters of basic model

Table 2 Parameters of shielding model

Table 3 Material parameters of model

4 结果分析

4.1 特征阻抗

PCB印制线特征阻抗计算通常采用Johnson and Graham的近似理论公式[11],商用软件Polar9000与该理论计算结果误差小于1 Ω。但是对于硅基板上的HBM信号线,传输线铜厚与线宽比值,以及传输线铜厚与介质厚度比值均大于PCB传输线的相应比值,与近似条件相违背。所以,无论近似公式的数值计算还是商用阻抗计算软件,对HBM信号传输线阻抗分析都不适用。本文从基本的RLGC参数着手,先理论计算用RLGC描述的特征阻抗,然后对HBM传输线进行三维仿真,提取物理结构对应的参数,最后对HBM信号线阻抗特性进行分析。

Z=R+jωL=γZ0

Y=G+jωC=γ/Z0

G=G0+Gd·f

其中,Z0为信号线的特征阻抗,γ是传播常数,Z和Y分别是信号线的阻抗和导纳,R和G是随频率变化的电阻和电导,R0和G0是低频条件下的电阻和电导,RS和Gd是由趋肤效应和介质损耗造成的高频电阻和电导。L和C是电感和电容。Z0的计算方式如下所示:

通过对基本模型中单信号线进行三维电磁场仿真可以提取参数R0、Rs、G0、Gd、L、C,从而得到信号线的阻抗频率曲线。HBM2/HBM2E信号目标速率在2 Gbps~4 Gbps,对应奈奎斯特频率为1 GHz~2 GHz,这里称为目标频率。频域曲线横坐标统一采用对数坐标形式,便于观察目标频率结果及高频趋势。每幅图中线条采用了不同形状进行标识区分,为了清晰显示,标识密度远远低于实际仿真频点。

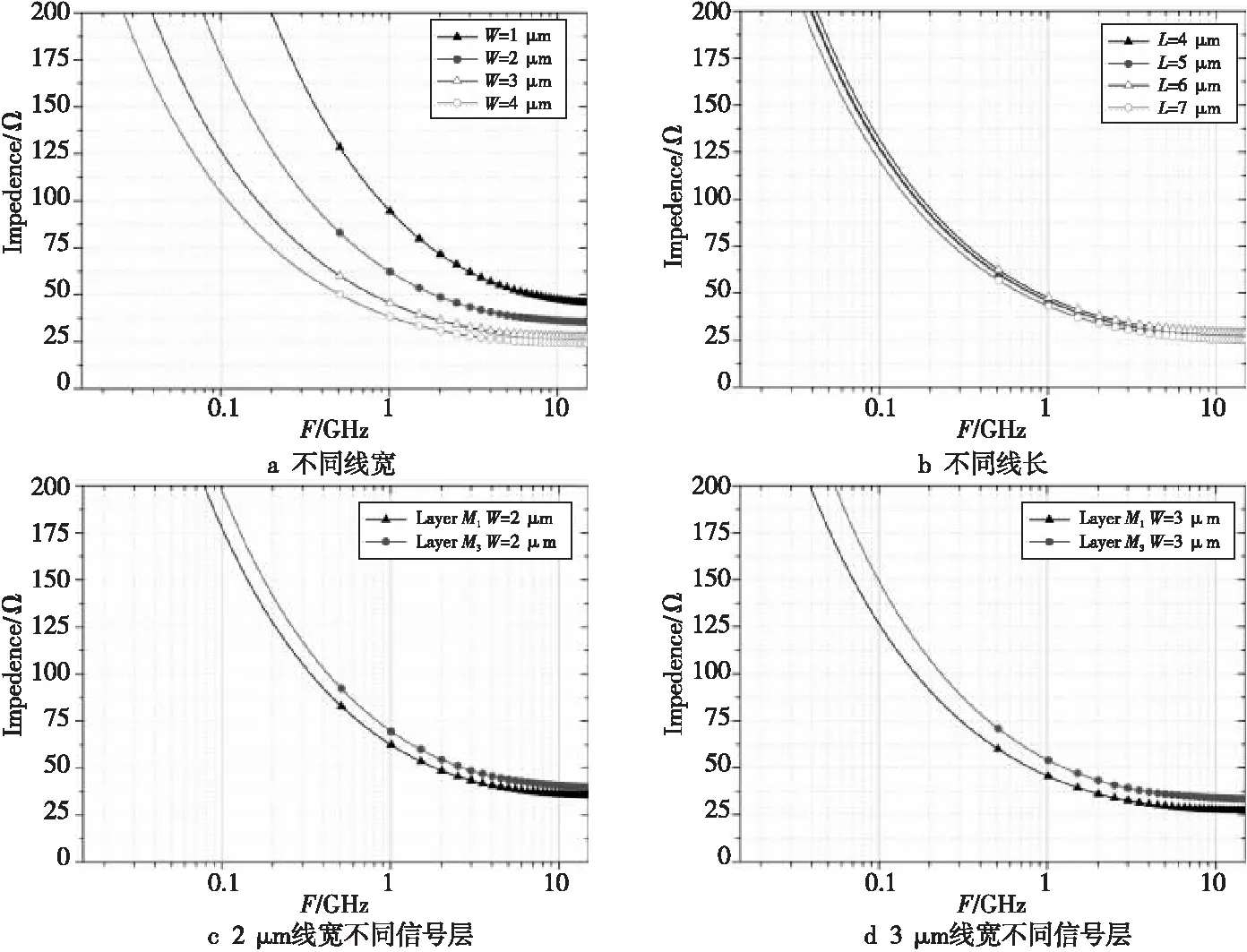

图4a是固定线长5 mm和信号层M1,线宽从1 μm增加至4 μm时的阻抗频率曲线,可以看出,随着频率的增加,不同线宽的阻抗都逐渐降低。5 GHz以下,阻抗下降趋势明显;;5 GHz以上,阻抗值下降缓慢,趋于平稳。随着线宽的增加,各频点的阻抗值降低。目标频率内,1 μm线宽阻抗范围为95 Ω~72 Ω,2 μm线宽阻抗范围为63 Ω~49 Ω,3 μm线宽阻抗范围为46 Ω~36 Ω,4 μm线宽阻抗范围为37 Ω~31 Ω。图4b是固定线宽3 μm和信号层M1,线长从4 mm增加至7 mm时的阻抗频率曲线。结果显示,线长的改变对各频点的阻抗影响极小。图4c和图4d是不同信号层在2 μm线宽和3 μm线宽时的阻抗对比。可以看出,无论线宽是否变化,各频点M3层的信号线阻抗都比M1层的信号线高6 Ω~8 Ω。

Figure 4 Impedance curves under four conditions图4 4种条件下的阻抗曲线

4.2 插入损耗

在基本模型基础上仿真4种不同条件对应的插入损耗,分析HBM信号线的损耗特性及敏感参数。

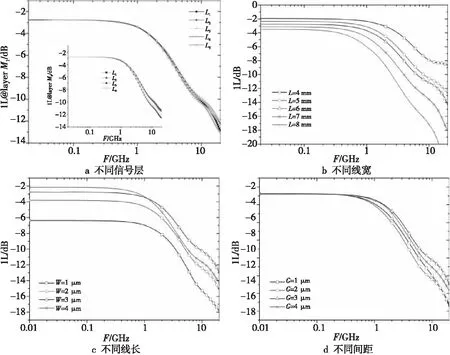

图5a是在基本模型参照表1参数条件下,M1层和M3层多条信号线的插损曲线。其中,嵌入的小图为M1层信号线插损曲线,大图为M3层信号线插损曲线。L1至L5代表各层中多条参数相同的信号线。可以看出,每个信号层的不同信号线差损曲线比较一致,2个信号层的差损曲线差异很小。200 MHz以下,插入损耗值稳定在-2.8 dB,可以把该值称为与结构对应的固有损耗;200 MHz~1 GHz,插入损耗缓慢增加;1 GHz以后随频率增幅明显。目标频率内,插入损耗值为-3.5 dB~-4.8 dB。

Figure 5 Curves of insertion loss under four conditions图5 4种条件下插入损耗曲线

图5b是在基本模型基础上,固定线宽为3 μm,间距为3 μm,信号层M1,线长从4 mm增加至8 mm时的插入损耗曲线。每一种线长的插损曲线具有相同的低频区平稳,高频区急剧下降的趋势。随着线长的增加,每个频点对应的损耗相应增加,从4 mm至8 mm,固有损耗增幅为1.6 dB。频率越高,增幅越大。

图5c是在基本模型基础上,固定线长为6 mm,间距为3 μm,信号层M1,线宽从1 μm增加至4 μm时的插入损耗曲线。线宽越大,固有损耗越小。1 μm与4 μm线宽的固有损耗相差4 dB。频率大于500 MHz时,插入损耗与线宽不再是单调递减关系:线宽从1 μm增加至3 μm时,各频点的插入损耗都逐渐变小,差值与固有损耗差值相当;线宽从3 μm增加至4 μm时,插入损耗曲线存在相交点。相交频点以前,细线宽损耗大。

图5d是在基本模型基础上,固定线长为6 mm,线宽为3 μm,信号层M1,间距从1 μm增加至4 μm时的插入损耗曲线。间距的改变对固有损耗没影响。高频区域,插入损耗随间距变化没有固定规律,虽然存在差异,但幅度明显小于线长和线宽改变引起的损耗变化。

4.3 总串扰

本节进一步仿真分析信号线之间的相互影响以及消除干扰的办法。

首先,选定M1层最中间的信号线为目标线,M1层其它信号线及M3层所有信号线为干扰线。借鉴文献[12]中的总串扰计算方法,用总串扰值评估不同结构参数的串扰情况。总串扰PSXT的计算如下所示:

PSXT(f)=-10 log(10-PSNEXT(f)/10+10-PSFEXT(f)/10)

选择目标传输线一侧端口为目标端口,用i标识。近端串扰NEXT(f)为:干扰线在与i端口同侧的所有端口的Sni(f)参数,n代表近端打扰端口。远端串扰FEXT(f)为:干扰线与i端口异侧的所有端口的Smi(f)参数,m代表远端打扰端口。

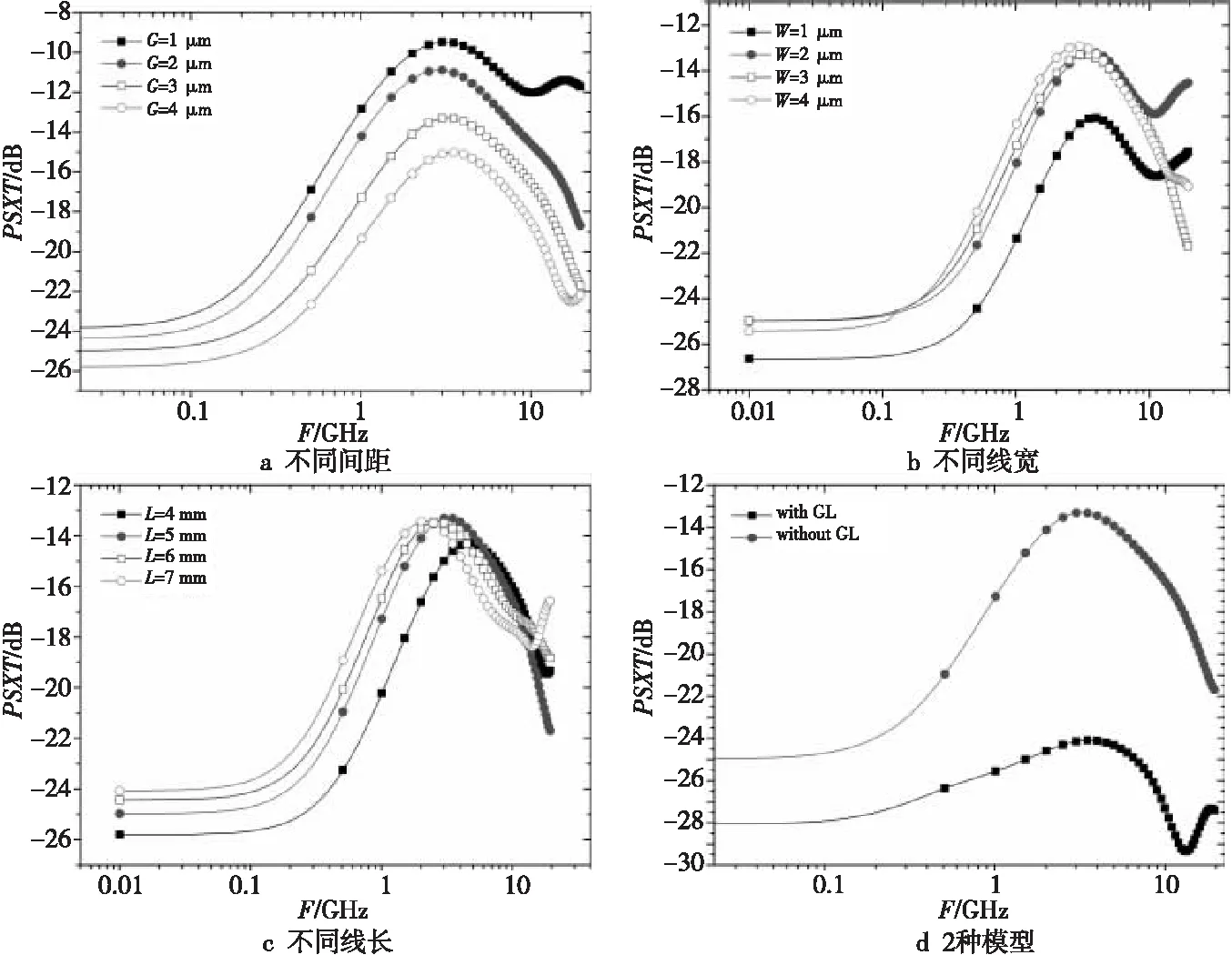

计算结果如图6所示,图6a是在基本模型基础上,固定线长为6 mm,线宽为3 μm,信号层M1,间距从1 μm增加至4 μm时的总串扰频变曲线。图6b是在基本模型基础上,固定线长为6 mm,间距为3 μm,信号层M1,线宽从1 μm增加至4 μm时的总串扰频变曲线。图6c是在基本模型基础上,固定线宽为3 μm,间距为3 μm,信号层M1,线长从4 mm增加至7 mm时的总串扰频变曲线。

Figure 6 PSXT curves under four conditions图6 4种条件下总串扰曲线

图6a~图6c中所有结构的总串扰最大值均在3 GHz频点附近,全频段内,总串扰与信号间距呈反比关系,间距越大,耦合作用越小,总串扰值越小,间距增加1 μm,总串扰值减小约1 dB。线宽从2 μm增加至4 μm对总串扰曲线几乎没影响,线宽为1 μm时,总串扰有2 dB~3 dB左右改善。目标频段以下,线长与串扰成正比关系,这时的耦合距离与耦合作用正相关,从4 mm至5 mm,总串扰增幅为1 dB,从5 mm至7 mm,每mm串扰增幅为0.5 dB。可以看出,增加间距是全频段内改善串扰的有效途径,其它结构参数也对串扰值有一定影响,但需要明确工作频点进行筛选。并且,根据第2节对线宽和间距极值的评估,这些改善幅度十分有限。

在信号线中加入地屏蔽线,搭建地屏蔽结构仿真模型,设置如表2中满足极值6.8 μm的结构参数,总串扰频率曲线如图6d中方形标注线所示。可以看出,加入地屏蔽线后,总串扰值大幅降低,在目标频段内降低8 dB~12 dB。

4.4 时域眼图

频域分析可以快速反映HBM信号通道结构参数对阻抗、损耗和串扰特性的规律性影响,便于参数优化设计。但是,JEDEC规范中对于HBM收发信号是基于时域进行要求的,需要再从时域角度进行验证。

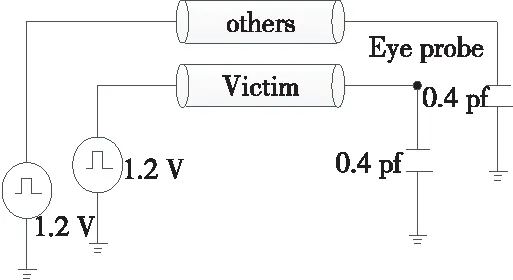

搭建如图7所示的时域仿真拓扑,用1.2 V、3.2 Gbps脉冲信号作为发射源,传输线采用对应模型在频域仿真中提取的S参数,接收负载根据规范要求设置为0.4 pf,在传输线末端查看接收眼图。Victim通道为M1层最中间通道,others代表除目标通道外的其它所有通道。为最大程度反映通道间的相互作用,目标通道与其它通道采用不同信号源码型。

Figure 7 Topology of time-domain simulation图7 时域仿真拓扑

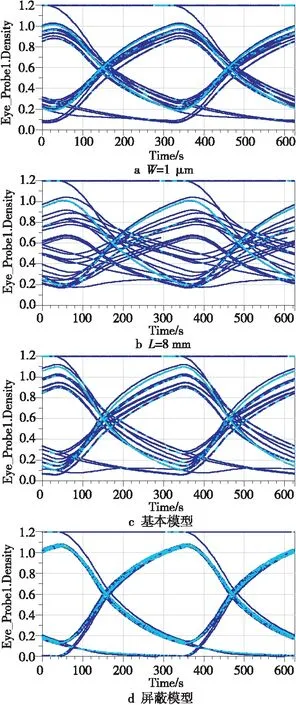

图8a是在基本模型基础上改变线宽为1 μm的信号通道对应的接收眼图,图8b是在基本模型基础上改变线长为8 mm的接收眼图,图8c是基本模型信号通道接收眼图,图8d是屏蔽模型信号通道接收眼图。可以看出,8 mm长度通道眼图已经闭合,基本模型3 μm线宽通道的眼高略高于1 μm线宽通道,但是3 μm线宽通道受串扰影响抖动极大。地线屏蔽模型既具有3 μm线宽的低损优势,又有效解决了信号间的干扰,所以眼高和抖动参数明显优于3 μm线宽的,在满足规范中的200 ps最小脉宽和600±240 mV电平要求上,裕量充足。

Figure 8 Eye_Probel.Density of different signal channel structures图8 不同信号通道结构对应的时域眼图

5 结束语

本文从HBM颗粒管脚阵列结构出发,分析信号分布及单信号线布线空间极限值。通过建立2层信号线传输模型,提炼频域阻抗分析方法和总串扰计算方法,从频域角度分析信号层数、线宽、间距和线长对电性能传输参数的影响。进一步结合规范要求,从时域进行部分模型分析验证,结果显示:

(1)阻抗是频变的,5 GHz以上趋于平稳。线宽越大,阻抗越小。目标频率范围内3 μm线宽更接近于50 Ω。线长对阻抗影响微小,远硅层阻抗比近硅层阻抗大6 Ω~8 Ω。

(2)线宽和线长是插入损耗敏感参数,其中,针对低频区的固有损耗,线宽影响占主导,针对高频区线损耗,线长影响较大。间距和布线层对损耗影响较小。

(3)增加间距是全频段内改善串扰的有效途径,但由于布线空间限制,改善幅度十分有限。在信号线中加入地屏蔽线,总串扰值大幅降低,在目标频段内降低8 dB~12 dB。

(4)地线屏蔽模型既具有3 μm线宽的低损优势,又有效抑制了信号间干扰,眼图参数质量高,是HBM信号传输结构设计中的优选。