一种CDC信号滑动窗口时序分析方法*

马驰远,雷国庆

(国防科技大学计算机学院,湖南 长沙 410073)

1 引言

同步数字电路设计经常需要使用不同来源的多个异步时钟,这些异步时钟间信号的传递称为跨时钟域信号传递CDC(Clock Domain Crossing)。跨时钟域传递的信号称为CDC信号,该信号对于目的时钟域来说是异步信号,即不能确保被稳定地采样。这种不稳定性会造成意想不到的错误[1],使电路无法正常工作。针对这种情况,研究人员在设计中通常会插入CDC逻辑,将CDC信号稳定地传递到目的时钟域[2]。

对于一个多位总线CDC信号的CDC逻辑,多位信号之间还需满足一定的时序要求才能确保信号正确地传递到目的时钟域。CDC信号的时序分析是分析源时钟域寄存器发出的多位CDC信号是否能被目的时钟域寄存器正确地采样。CDC信号的一般时序要求是目的时钟域采样时刻范围内同时变化的CDC信号不超过1个[3],因此CDC信号被目的时钟域采样的时刻偏差只要不超过一个源时钟周期就可以满足时序要求。

CDC信号产生时序违反的主要原因是时钟频率过高导致约束较严或CDC逻辑过于分散。近年来随着设计频率的逐渐提升、设计规模的逐渐增大,CDC信号时序检查开始成为芯片投片前的必备检查项。通常CDC逻辑采用固定约束分析方法进行时序检查,但这种方法由于约束条件过严会导致虚假时序违反及不必要的时序修复,从而增大了设计面积。

本文提出了一种CDC信号滑动窗口时序分析方法,在每种工艺角(corner)的每条CDC通路上单独设置适合的检查窗口进行时序分析,有效避免了固定约束分析方法的问题。

2 背景

随着设计频率的逐渐提升、设计规模的逐渐增大,CDC逻辑电路的失效率也逐渐增大。为了避免CDC问题导致的电路错误,近年来国内外学者对CDC电路和时序展开了大量研究。Cummings[3]对CDC电路原理进行了阐述,给出了一种通用CDC逻辑结构并对这种结构的应用提出了具体实施方案。Chaturvedi[4]提出了一种CDC结构检查和时序分析的流程并在芯片投片时应用成功。Matsuda等[5]在FPGA中对CDC结构进行了验证方法学和时序分析的研究。Talupuru等[6]也提出了一种通过形式验证和时序分析来避免CDC电路毛刺的方法。还有些学者针对CDC逻辑结构展开了研究[7,8]。

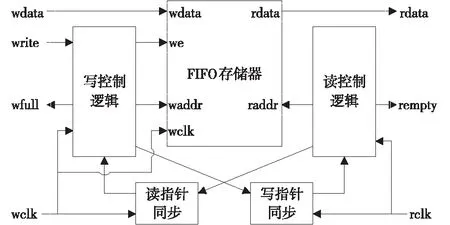

目前存在多种多位CDC信号的CDC逻辑,最常见的是如图1所示的CDC逻辑结构[3],它包括2个方向的CDC信号:从写时钟wclk到读时钟rclk的CDC信号有写指针信号和数据信号,从读时钟rclk到写时钟wclk的CDC信号有读指针信号。这些CDC信号都应该满足一定的时序要求。

Figure 1 Structure of CDC logic图1 CDC逻辑结构

不同设计对CDC信号的时序要求是不一样的。如果一个设计的时钟频率只有几百兆赫兹并且CDC逻辑所在设计模块面积不大,这时CDC信号几乎不会违反时序要求,因此对这种设计不用检查CDC信号的时序。如果设计频率很高并且经过后端设计后的CDC逻辑比较分散,CDC信号就有可能违反时序约束。为了保证设计的功能正确,CDC信号就必须进行时序分析和收敛。

目前主要的CDC信号时序分析方法是固定约束分析方法[3 - 5],它在分析CDC信号是否满足时序要求时,对所有CDC信号统一设置固定的约束参数。因为CDC逻辑一般在2个方向传递信号,所以既要分析源时钟域到目的时钟域的CDC信号,也要分析目的时钟域到源时钟域的CDC信号。以源时钟域到目的时钟域的分析来说,约束参数要设置2个:最大延时和最小延时。最大延时是指源时钟域的CDC信号到目的时钟域采样时的最大延时约束,最小延时是指源时钟域的CDC信号到目的时钟域采样时的最小延时约束。对源时钟域到目的时钟域的所有信号统一设置约束参数且参数是固定的,电路满足最大延时约束和最小延时约束后就能确保正常工作。芯片投片前设计人员会在多个corner下进行时序分析。深亚微米工艺的corner数可能会有二、三十个且不同corner的时序情况差别很大,同一条时序路径在针对setup分析的corner下和针对hold分析的corner下的延时会相差一倍甚至更多。固定约束分析方法只能选择最严格的约束参数进行分析,以保证功能正确,并且为了通过检查不得不加入一些不必要的逻辑。此外,2个时钟域间可能存在多条CDC通路而不同通路的时钟树延时不一定相同。为了保证电路的时序正确性,固定约束分析方法可能在本来能满足时序要求的电路上加入更多的逻辑,这些额外逻辑都是不必要的面积开销,会导致电路的成本升高、功耗变大。

3 CDC信号滑动窗口时序分析方法

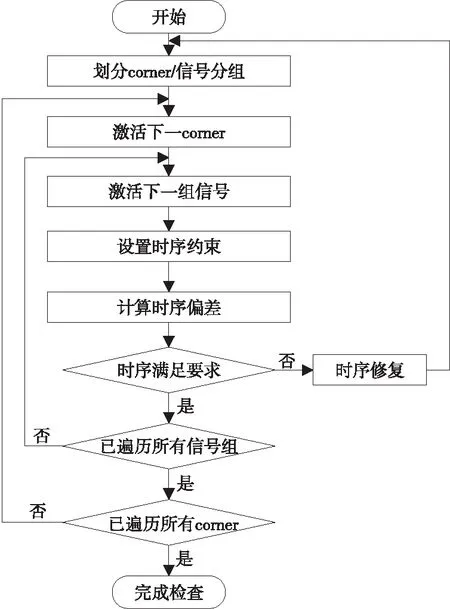

为了解决固定约束分析方法带来的逻辑和面积增大的问题,本文提出了一种CDC信号滑动窗口时序分析方法。这种方法在每种corner的每条CDC通路上单独设置适合的时序分析检查窗口进行时序分析,分析流程如图2所示。

Figure 2 Flow chart of the sliding window timing analysis method of CDC signals图2 CDC信号滑动窗口时序分析方法流程图

首先对设计进行corner划分和CDC信号分组。设计在不同corner下的时序情况差别很大,所以要在所有corner下对设计进行时序分析并修复。2个异步时钟域之间可能存在多组CDC通路,如果对多组CDC通路统一设置时序约束显然会使约束过于严格,从而导致虚假的时序违反并增加额外的时序修复工作,因此根据通路对CDC信号进行分组会使时序检查更加精确。当然,能够对CDC信号进行分组的前提是能完全理解CDC逻辑,这对设计人员来说通常不是问题,但某些继承的设计或重用的IP可能使用了特殊的CDC逻辑,从而造成分组困难。

其次,本文方法对于某一corner下的某一组CDC通路会单独设置时序约束。在worst corner下和best corner下的设计频率一般是不一样的,这种差别也同样要反映在CDC信号的时序约束上。如图1所示,每一组CDC信号包括3类:写指针信号、读指针信号和数据信号。同一CDC通路信号的时序偏差不能超过1个源时钟周期,按此原则可设置相应的约束。每一类信号可用最大延时命令和最小延时命令进行约束,最大延时和最小延时具体设置的值并不重要,但对CDC信号设置的最大延时和最小延时之差不能大于1个源时钟周期。为了方便后续分析,同一个CDC通路写指针信号和数据信号最小延时的设置最好一样。

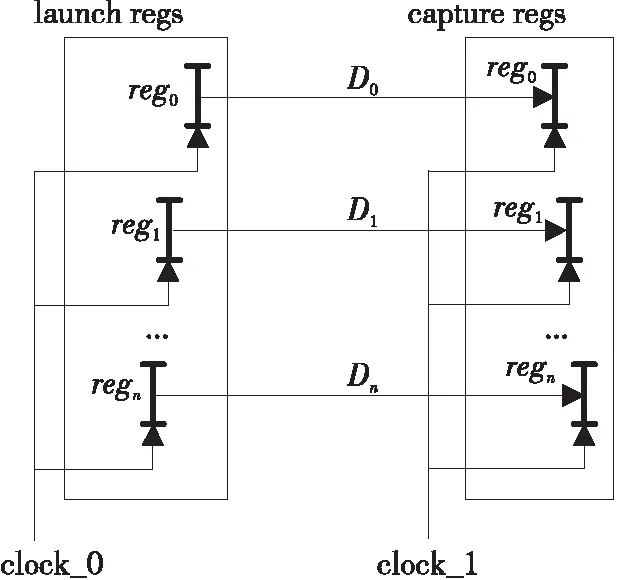

接着要计算每组CDC信号的时序偏差是否满足时序要求。CDC信号时序满足要求的关键在于每个总线的多位信号是否能在一个要求的时间段内被目的时钟捕获,也就是要在一个源时钟周期内被捕获,因此单个信号即使违反了时序约束也并不意味着有真正的时序违反。图3所示是一个多位总线的CDC信号,clock_0是源时钟,clock_1是目的时钟,launch regs是n位源时钟域寄存器,capture regs是n位目的时钟域寄存器,在CDC逻辑里这些寄存器一一对应。时钟到不同寄存器的时钟树延时是不一样的,所以图3中每组regs的不同reg并没有对齐。本文方法是先计算出每个信号的时序偏差,以图3中reg0为例,它的时序偏差是clock_0从产生点出发经过launch regs中的reg0并经过D0的延时减去clock_1从产生点出发到capture regs中的reg0的延时,这个偏差与clock_0和clock_1的时钟树偏差有关,结果可能是正值也可能是负值。对所有信号的时序偏差分别进行计算后,可以找出最大偏差值和最小偏差值,二者的差值如果小于时序约束值就可认为此类CDC信号的时序满足要求。

Figure 3 CDC signals circuit图3 CDC信号电路

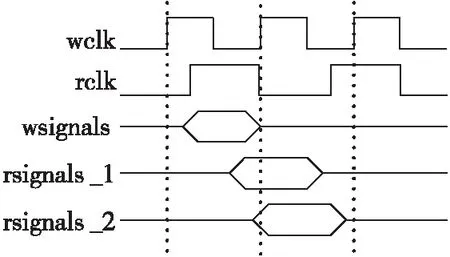

本文方法实际上是划定了一个时序约束窗口,这个窗口的宽度对于同一corner下同一组内的信号是固定的,但对不同corner或不同组的信号窗口是不同的。如图4所示,wsignals是写时钟wclk相关寄存器发出的一组多位CDC信号,rsignals_1和rsignals_2分别是在不同corner下这些CDC信号到达读时钟rclk相关寄存器的输入信号范围。由于不同corner下的电路延时不一样,因此rsignals_1和rsignals_2的到达时间范围是有区别的。但是,只要所有CDC信号的捕获时刻落在约束要求的窗口内,就可认为满足了时序要求。所以,本文方法对于CDC信号的路径延时没有要求。信号捕获窗口在不同情况下是可以左右移动的,因此本文将这种方法称为滑动窗口时序分析方法。逻辑在后端设计时会生成时钟树,不同时钟的时钟树延时是不一样的,固定约束分析方法无法避免时钟树延时的影响,而本文方法可以避免时钟树延时的影响,降低了时序要求,获得了最精确的分析结果,避免了由于约束过严而导致加入额外逻辑的情况。

Figure 4 Sliding window waveform of CDC signals图4 CDC信号滑动窗口波形

计算完每一类信号的时序偏差后,根据时序报告可判断当前CDC信号是否满足时序要求。如果不满足要求就需进行时序修复,常用的修复手段是在时钟路径或数据路径中加入缓冲器来缩小时钟树偏差或弥补数据路径的偏差,这些方法都会加入额外的逻辑,增加芯片面积。

上述时序约束设置和时序计算及修复需要在每种corner下对每条CDC通路分别进行,以确保在所有条件下功能都正确。因此,在完成物理设计和正常的静态时序分析外,还要额外对设计进行CDC通路的分析。这种分析无需改动设计,只要通过时序分析软件编写程序进行分析即可。当然,这相对于固定约束分析方法来说增加了一定的软件运行时间和分析工作量。

4 实验与结果分析

CDC逻辑通路在布局布线后的放置通常较为集中,因此较少出现真正的数据捕获错误。本文方法针对规模较大且频率较高的多个真实CDC设计进行时序检查,只有极少数的CDC电路出现了时序违反。而采用固定约束分析方法经常会检查出时序违反的情况,大部分的时序违反是由于分析方法不当而产生的,在实际工作中这部分电路时序是没有问题的。

对于CDC信号时序功能正确的情况,本文方法能精确确认时序而无需改动逻辑。而固定约束分析方法要求每一位信号都要满足时序约束,这无疑使检查过于严格,因此常常会出现虚假时序违反,不得不进行额外的时序修复,时序修复规模和源时钟树/目的时钟树的偏差以及CDC逻辑特性相关。

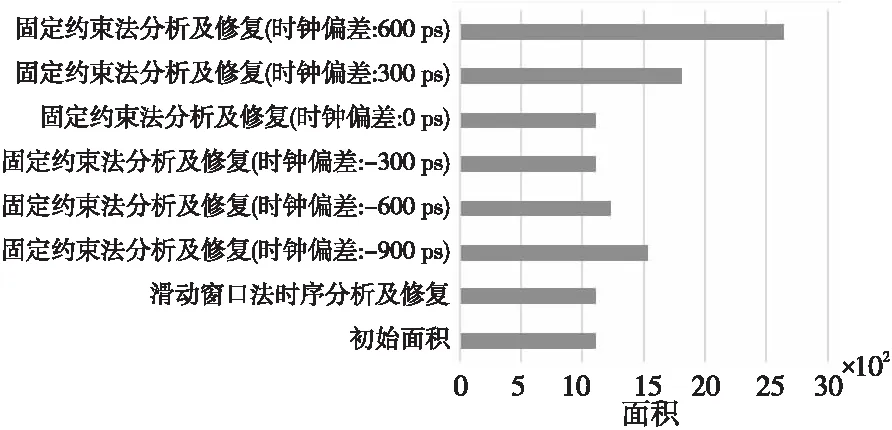

假设写时钟和读时钟的频率都是2 GHz且同一时钟到相关寄存器时钟引脚的时钟树延时相等,图5和图6是在16 nm工艺下使用typical库在CDC逻辑FIFO深度为4且通路位宽为32位时,分别评估读写时钟树延时不等时采用本文方法和固定约束分析方法进行时序修复后的面积对比情况。采用的设计经过验证都没有时序问题。图中的时钟偏差是读时钟树延时减去写时钟树延时的差。固定约束分析方法设置的最大延时和最小延时的值不一定是固定的,只要二者的差为一个时钟周期就可以,但这2个值一旦设置好就不会随设计的物理实现情况而改变,因此称这种方法为固定约束分析方法。为了简单起见,固定约束分析方法的最小延时和最大延时分别设为0和一个时钟周期,设置成其他值的效果也是一样的。固定约束分析方法是时钟树延时偏差敏感的,它会根据设置将CDC信号的读写时钟树延时取平。对于违反延时约束的信号,在写时钟树延时比读时钟树延时短的时候,写时钟树可能会被加大延时;在写时钟树延时比读时钟树延时长的时候,读时钟树可能会被加大延时。加大延时的方法是在每个相关寄存器的时钟端插入缓冲单元。图5给出了自动时序修复情况下在时钟偏差为-900 ps~600 ps时使用固定约束分析方法和本文方法进行时序修复后的面积对比。由于时钟偏差大小对本文方法的分析结果无影响,时序修复后的面积没有变化;而对于固定约束分析方法,由于每位信号都要满足时序要求,时钟偏差的不同造成结果差别很大。

Figure 5 Area comparison of two timing analysis methods after automatic timing repair (FIFO depth is 4)图5 2种时序分析方法自动时序修复后的面积对比(FIFO深度为4)

由图5可知,使用固定约束分析方法在时钟偏差为0时读写时钟树的延时相等,此时所有信号都满足时序要求,因此不需进行时序修复,面积结果和本文方法是一样的。时钟偏差为负时表示写时钟树延时大于读时钟树延时,在一定范围内所有信号还是可以满足时序要求的,如图5中时序偏差为-300 ps时,因此面积不会因为时序修复而增加。但是,偏差一旦超过某个阈值,就需要减小读写时钟树偏差进行时序修复,由图1可知读时钟CDC信号为写指针和读数据,修复的方法是加大这些信号相关寄存器的读时钟树延时。如图5中时序偏差为-600 ps和-900 ps的情况,时钟偏差越大插入单元越多,因此造成面积增大。时钟偏差为正时表示写时钟树延时小于读时钟树延时,在一定范围内所有信号也是可以满足时序要求的,因此面积不会因为时序修复而增加。但是,偏差一旦超过某个阈值也需要减小读写时钟树偏差进行时序修复,由图1可知写时钟CDC信号为读指针和FIFO寄存器,修复的方法是加大这些信号相关寄存器的写时钟树延时。如图5中时序偏差为300 ps和600 ps时,时钟偏差越大插入单元越多,因为FIFO寄存器数量较大且FIFO数据的每一位会通过mux直接连接到读时钟域,在自动修复过程中所有FIFO数据寄存器的时钟端都会被插入延时单元,因此最终插入的单元数量取决于FIFO的容量。在时序偏差为600 ps时,采用本文方法的CDC逻辑面积是采用固定约束分析方法进行修复后面积的42%。从图5中还可以观察到,采用固定约束方法修复时时钟偏差为600 ps和-600 ps的面积相差很大。这是因为加大写时钟树延时要插入单元的寄存器数量很多(主要是FIFO寄存器),而加大读时钟树延时要插入单元的寄存器数量较少。

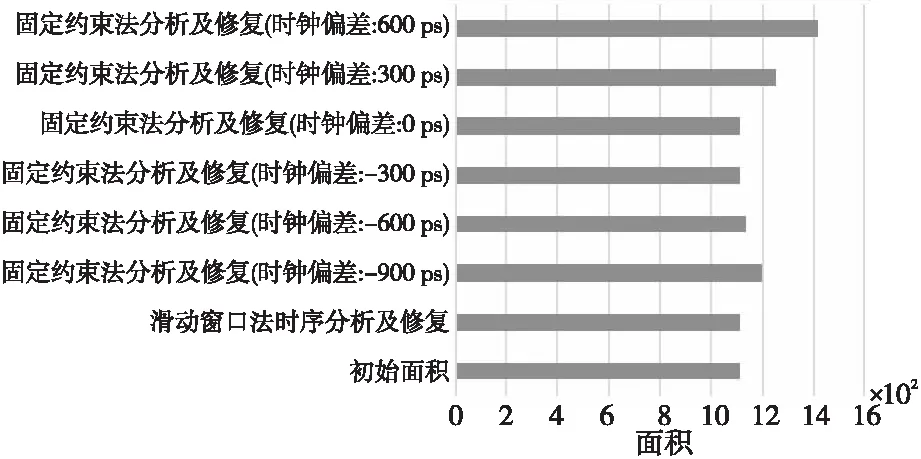

物理设计阶段有2种时序修复方式。一种是工具自动插入单元进行时序修复,图5就是自动时序修复的结果,这种方式会在每个跨时钟域寄存器前插入缓冲单元。另一种是手工时序修复,就是由设计人员手工插入延时单元进行时序修复,这种方式的好处是可以找到时钟树的公共点插入缓冲单元,在达到相同效果的同时减少插入的缓冲单元数。假设平均5个寄存器的时钟端能找到一个时钟树的公共点,插入的单元数量就可以减少到自动时序修复的1/5。图6给出了手工时序修复方式下的面积评估结果,可以看到这种方式下的面积比自动时序修复方式的小,在时序偏差为600 ps时采用本文方法的CDC逻辑面积是采用固定约束分析方法进行修复后面积的78%,这比自动时序修复的效果好,但手工时序修复使物理设计工作量加大。

Figure 6 Area comparison of two time analysis methods after the manual timing repair (FIFO depth is 4)图6 手工时序修复时2种时序分析方法的面积对比(FIFO深度为4)

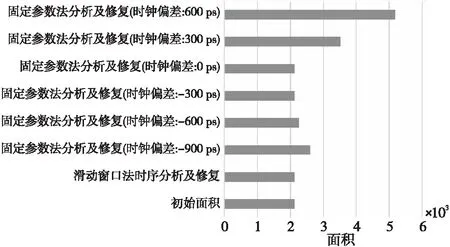

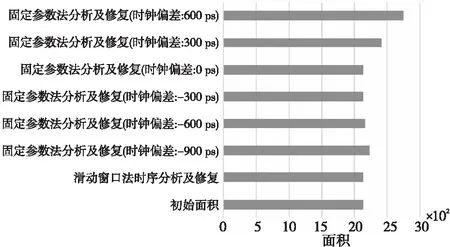

以上是FIFO深度为4时使用2种方法进行分析时的面积对比。在设计中FIFO深度为4是最小深度,更大的FIFO深度在实际设计中也经常会用到,本文进一步评估了FIFO深度为8时的情况。图7为FIFO深度为8时自动时序修复方式下使用2种方法进行时序修复后的面积对比。图8是FIFO深度为8时手工时序修复方式下使用2种方法进行时序修复后的面积对比。

Figure 7 Area comparison of two time analysis methods after automatic timing repair (FIFO depth is 8)图7 2种时序分析方法自动时序修复后的面积对比(FIFO深度为8)

Figure 8 Area comparison of two time analysis methods after the manual timing repair (FIFO depth is 8)图8 手工时序修复时2种时序分析方法的面积对比(FIFO深度为8)

从图7和图8可以看出,FIFO深度为8时本文方法在2种修复方式下相对固定约束分析方法的面积比例和FIFO深度为4时是基本一样的,实验表明,更深的FIFO深度的情况也类似,但固定约束方法增加单元的绝对面积要远远超过FIFO为4的情况。这是因为FIFO深度增加后无论加大写时钟树延时还是加大读时钟树延时都需要插入更多的缓冲单元,因此FIFO深度越大本文方法相对固定约束分析方法的优势越明显。

无论采取何种时序修复方式,固定约束分析方法都可能会导致单元面积的增长,而本文方法只在真正违反时序的路径上进行时序修复,因此采用本文方法避免了由于检查条件过严而增加不必要的逻辑,加速了时序收敛且最终能得到最优的实现结果。

5 结束语

多异步时钟域设计中CDC信号的时序分析及修复是保证设计功能正确的必要手段。本文提出的CDC信号滑动窗口时序分析方法在每种corner的每条CDC通路上单独设置适合的检查窗口进行时序分析,有效避免了常用的固定约束分析方法由于约束条件过严导致的虚假时序违反及不必要的时序修复而使设计面积增大的问题,同时减轻了后端设计工作量。实验结果表明,本文方法显著节省了单元面积。

本文方法针对的是图1中的CDC结构,这种结构也是目前使用最广泛的CDC结构。本文方法对其他类型的CDC结构同样适用,但具体实施方式需要相应地进行调整优化。