抗功耗攻击的RSA 协处理器*

蔡梓文,崔 超,肖 勇,赵 云,林伟斌

(南方电网科学研究院有限责任公司,广东 广州 510663)

随着通信和网络技术的不断发展,国家安全、企业机密和个人隐私均存在泄漏风险;如何防止类似信息泄漏、保护信息安全已成为业界所关注的热点问题[1]。RSA 由于其安全性高,已成为应用最广泛的非对称加密算法。但在RSA 算法的硬件实现过程中,仍存在一些问题:一方面,为了确保加密算法安全性,RSA 的密钥长度一般要选择1 024 bit 及以上,运算速度慢、计算时间长;另一方面,没有添加保护手段的RSA 硬件实现过程中很容易受到功耗分析等技术的攻击[2]。

目前,RSA 硬件系统主要是对模乘算法进行改进与优化[3];而RSA 抗功耗攻击的相应手段主要是集中在模幂算法中。本文根据现有的抗功耗攻击RSA 算法,在模幂运算过程中选择指数随机化掩盖和添加伪操作的RTL 二进制扫描方法;在模乘运算中,拟结合CSA 加法器和2 层Karatsuba 乘法器实现的基256 免减Montgomery 模乘算法。最后在不消耗过多面积的前提下,设计了一种快速、抗功耗攻击的RSA 协处理器,并开展功能仿真与综合分析。

文章第1 节主要介绍抗功耗攻击的RSA 算法设计;第2 节详细描述抗功耗攻击的RSA 协处理器的硬件架构设计;第3 节给出了RSA 协处理器的仿真验证和性能分析。

1 抗功耗攻击的RSA 算法设计

1.1 功耗攻击

在针对密码算法硬件系统的侧信道攻击方式中,功耗分析攻击是一种十分有效的方法。目前,功耗分析攻击主要分为简单功耗分析(SPA,Simple Power Analysis)和差分功耗分析(DPA,Differential Power Analysis)[4]。

SPA 攻击是一种对密码设备运行过程中所产生的功耗信息进行直接分析的方式。对于RSA 的二进制模幂运算而言,当扫描到的指数位是0 时,只执行模平方操作;当扫描到的指数位是1 时,执行模乘和模平方操作,因此运行时间和功耗信息会存在明显差异。

DPA 攻击是以SPA 为基础建立的更具有破坏性的方法;通过采用统计分析方法和纠错技术,DPA可从大量的密文和功耗波形中分析获取密钥信息。

1.2 抗功耗分析攻击的模幂算法

在算法层面,RSA 算法的加解密操作十分简单,即采用大数的模幂运算。但对于RSA 算法的硬件实现而言,需要综合考虑消耗面积和计算速度等;如果先计算出模幂值再求模,那么会占据大量的存储;所以模幂运算可采用二进制扫描模幂算法,将模幂运算分解成一系列模乘运算[5]。

为了能够防御简单功耗分析和差分功耗分析攻击,根据现有文献提出的抗功耗攻击措施[6],选择了指数随机化掩码和添加伪操作的形式。抗SPA和DPA 的模幂算法如下所示:

算法1抗SPA 和DPA 的二进制模幂

这个算法能够防御SPA 和DPA 攻击,通过随机数ran[0]的比特值判断是否执行伪操作,而且执行的伪操作是X=M*1 modN,其结果不进行寄存器存储,在减少伪操作计算量的同时也能消除模幂算法中不同比特值执行的功耗差异。

1.3 高基Montgomery 模乘算法

由上述分析可知:RSA 的模幂运算是通过迭代多次模乘运算来实现。因此在实际硬件设计中,限制RSA 算法运算速度的瓶颈是模乘运算,也就是说模乘运算是RSA 算法的核心运算。

在现存模乘算法中,蒙哥马利(Montgomery)模乘被广泛认为是最高效的模乘算法,只需要通过简单的移位和加法操作,而不需要涉及求模过程中耗费时间的除法运算,因此很适合用于RSA 的硬件系统设计。

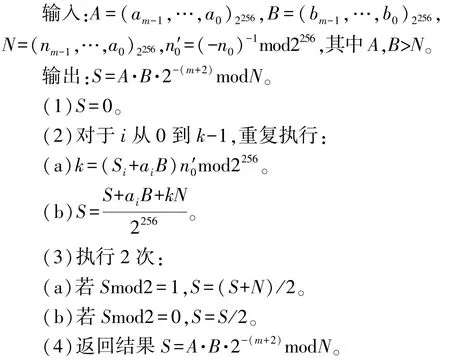

在大部分的RSA 硬件实现中,一般选择基2 的Montgomery 模乘算法,该方法需要n次循环才能得到模乘结果,因此需要的运算时间很长。在高级Montgomery 模乘的基础上,折中考虑运算速度和面积消耗,选择基256 的免减Montgomery 模乘算法,如下面所示:

算法2基256 的免减Montgomery 模乘算法

算法2 主要由3 个大数加法和3 个大数乘法组成。以1 024 位RSA 密钥长度为例,该算法会循环执行第二步4 次,同时为了保证结果S小于N以及免去减法判断操作,第3 步需要执行2 次,所以最后的结果是S=A·B·2-(m+2)modN。

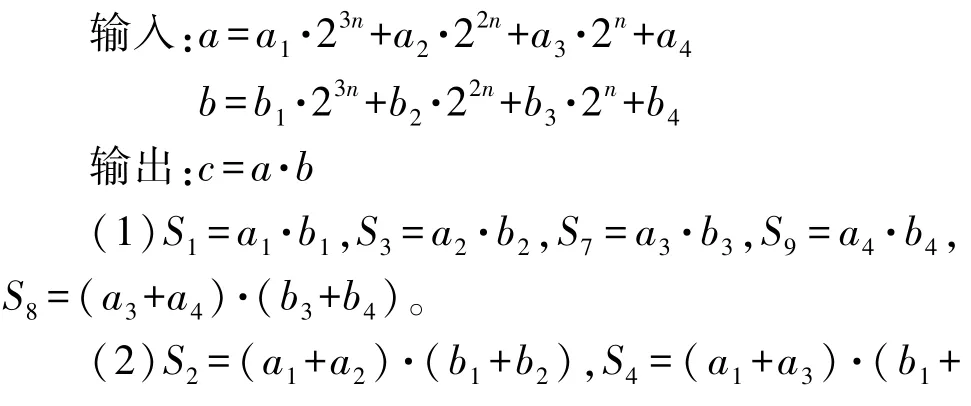

1.4 两层Karatsuba 大数乘法

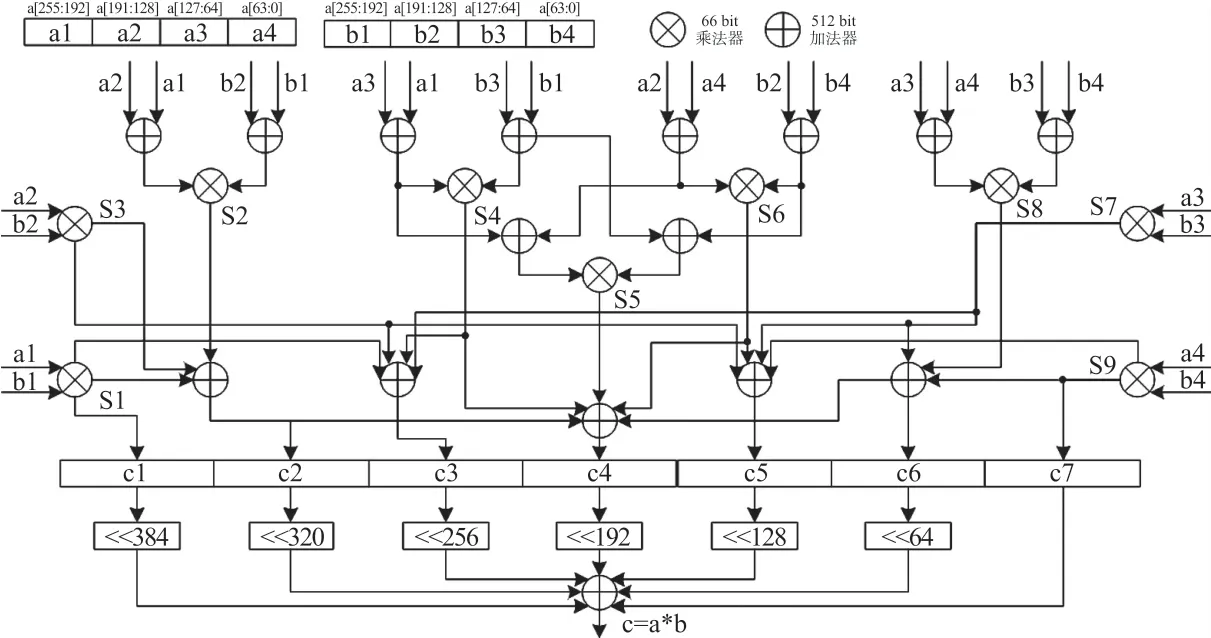

由上面模乘算法可知,模乘运算过程中,会涉及到256 bit×1 024 bit 的乘法运算,直接选择256 bit×256 bit 的乘法会耗费比较多的硬件资源,因此选择2层Karatsuba 算法实现256 bit 乘法,算法如下所示:

算法3两层Karatsuba 大数乘法

由算法3 可以看出,当执行256 bit×256 bit 的乘法运算时,不会直接例化256 bit 的乘法器,而是在面积和速度2 个方面均衡考虑,选择了64 bit 的乘法和512 bit 的加法。

2 RSA 协处理器的硬件设计

选择密钥长度为1 024 bit,按照自顶向下的设计理念,通过模块化和层次化的设计方法,以进行抗功耗攻击的RSA 协处理器硬件设计;在不消耗过多面积的基础上提高了RSA 系统的运算速度,并能够防御简单功耗攻击和差分功耗攻击。

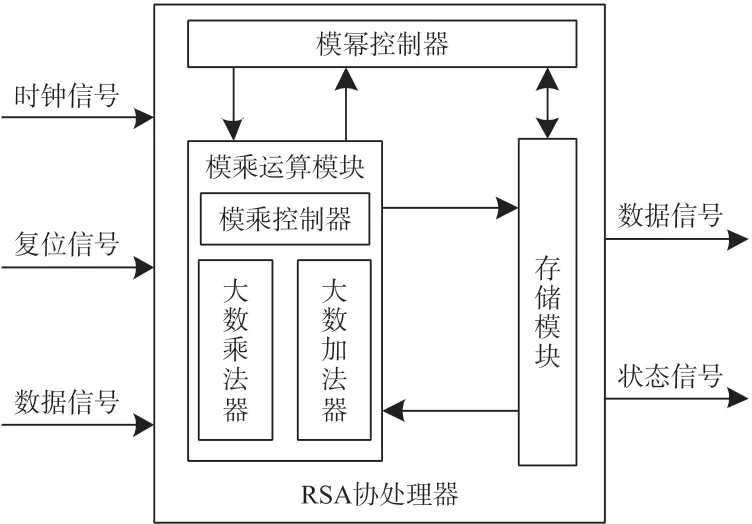

2.1 RSA 协处理器总体架构设计

RSA 协处理器的总体架构如图1 所示,整个设计主要由模幂控制器,模乘模块,大数乘法器,大数加法器和存储模块5 个部分组成。

图1 RSA 协处理器的总体架构

其中决定RSA 计算速度的核心部分是模幂单元,模幂单元经由模幂控制器由状态转换控制调度模乘运算模块来实现;由上面一节可知模幂运算可以由多次迭代模乘运算来完成,因此实质上模乘运算模块是RSA 算法的核心,该模块通过模乘控制器,利用有限状态机调用大数乘法器和大数加法器来实现Montgomery 模乘;存储器模块用于存放控制数据、状态数据和一些中间运算结果。

2.2 模乘运算模块硬件结构

根据算法2 设计的Montgomery 模乘器硬件结构如图2 所示,模乘运算模块包括模乘控制器,大数加法器和大数乘法器,其中实现模乘运算最重要的是大数乘法器。

图2 模乘运算模块的硬件结构

可以看出,模乘运算模块包括大数加法、大数乘法、移位、取模以及判断操作,由于下一运算步骤的值与上一运算步骤的值有关联,因此没有考虑并行处理。同时,为了能够在面积和速度进行均衡选择,只用了1 个大数加法器和1 个大数乘法器,其中的移位操作选择取高位加拼接完成,取模操作选择取低位完成。

2.3 大数乘法器硬件结构

大数乘法器的硬件结构如图3 所示。

图3 大数乘法器的硬件结构

从算法3 可知,乘法器采取“分而治之”的思想,选择2 层Karatsuba 算法来实现,把256 bit 的输入数据各自分解为4 个64 bit 的数据进行运算,在大数乘法器的硬件实现过程里,只需要例化1 个66 bit 的乘法器和4 个512 bit 的加法器,通过串行计算,总共需要9 个周期即可完成256 bit 的大数乘法操作。

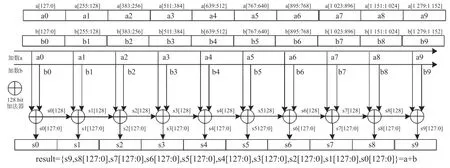

2.4 大数加法器硬件结构

经过综合分析,不直接采用1 280 bit 加法器,而是选择CSA 加法器,把1 280 bit 的输入值拆分成10 个128 bit 的数据再进行加法,CSA 加法器的硬件结构如图4 所示。

图4 CSA 加法器的硬件结构

3 功能仿真和性能分析

3.1 功能仿真

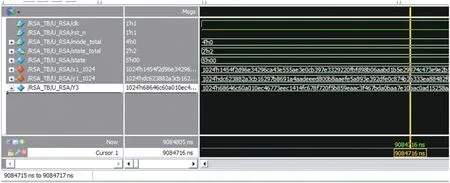

选择Verilog 语言对抗功耗攻击的RSA 协处理器进行RTL 代码的设计实现;然后使用Mentor 公司的Modelsim 工具对RTL 代码进行了功能仿真;最后把得到的结果与采用标准函数库的软件模型的输出结果进行大量的重复比较,从而验证该RSA 协处理器功能上的正确性。图5 为抗功耗攻击的RSA 协处理器模幂运算的RTL 仿真结果,图6 为采用软件标准函数库的模幂运算输出结果。

图5 RSA 协处理器模幂运算的RTL 仿真结果

图6 模幂运算的软件输出结果

以其中一组数据为例,从图5 和图6 中可以知道,硬件RTL 代码的结果Y3 信号和软件代码的结果A 是完全相同的,从而验证了结果的准确性以及硬件设计的正确性。同时,在仿真时钟周期为10 ns的条件下,还能从图5 中看出完成一次完整的1 024位的加密过程,大概需要9 084 610 ns,即约908 461个时钟周期。

3.2 侧信道分析

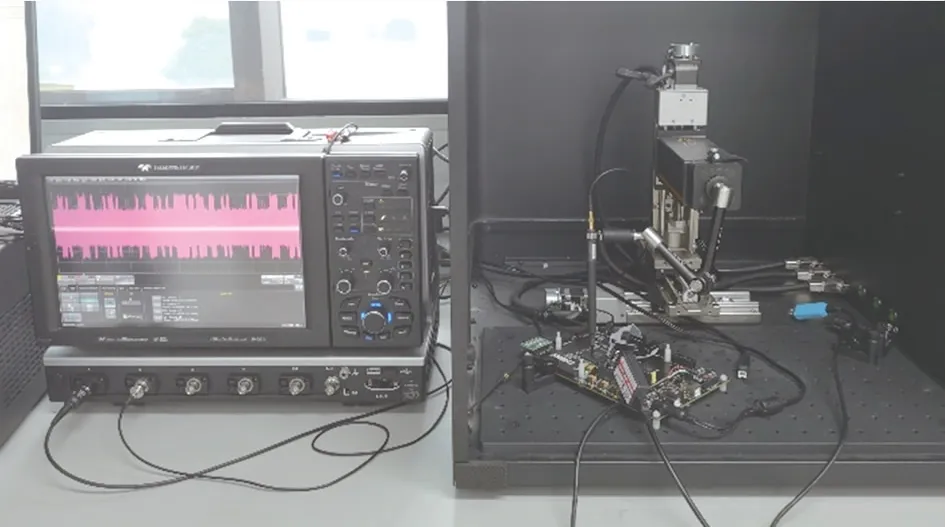

采用OSR 侧信道攻击平台对提出的抗攻击RSA 协处理器进行防护性能的侧信道分析验证。如图7 所示,实验设备包括中天XC7A200T 开发板、力科WAVERUNNER 610Zi 示波器、智能采集平台、高精度三轴平台、电磁探头及放大器等。

图7 侧信道攻击平台

首先对未添加抗攻击设计的RSA 硬件实现进行侧信道采集,使用电磁探头获取芯片进行加密运算时泄露的功耗信息。图8 清晰地反映出加密时由于密钥每一位的不同而体现出的功耗差别。当出现功耗尖峰时,表示此时在进行模乘和模平方;而未出现功耗尖峰时,则表示此时只进行模平方。因此,可以通过分析脚本对采集到的功耗曲线进行区分,从而根据是否有尖峰轻松判断出密钥的每一位是1 还是0。

图8 未加抗攻击的RSA 功耗波形

而所提出的抗攻击RSA 协处理器添加了基于指数随机化掩码和伪操作的防护。指数随机化掩码使得整个模幂运算中的指数都是随机变化的,而存在于整个循环中的伪操作会打乱功耗曲线,使得攻击者无法对齐运算时间与数据,更难以区分函数或相关性系数并以此分析出有用的信息。

用同样的方法对所提出的抗攻击RSA 协处理器进行侧信道攻击,得到功耗曲线如图9 所示。可以看出在加密开始后,曲线没有出现明显尖峰,泄露信息得到了有效隐藏,攻击者无法分辨当前操作,也难以通过功耗曲线的相关性分析破解出密钥。

图9 本文提出的抗攻击RSA 功耗波形

3.3 性能分析

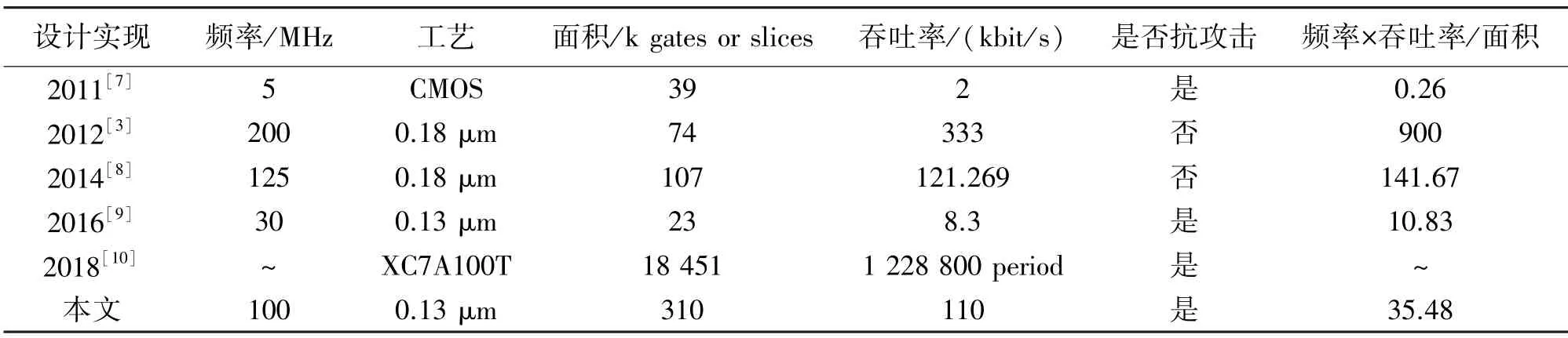

提出的抗功耗攻击RSA 协处理器能够以FPGA或者ASIC 实现。完成硬件设计后,在SMIC 0.13 μm工艺库和100 MHz 时钟频率的前提下,对其进行DC 综合,结果显示所耗费的面积约为310 k 门,其吞吐率为110 kbit/s。

表1 是所实现的RSA 协处理器跟其他文献的性能比较。从对比结果可以看出,虽然所设计的RSA 协处理器耗费面积较大,但是吞吐率以及能达到的频率也较高,而且能够防御SPA 和DPA 的攻击。在可抗攻击的设计里,频率吞吐率与速度的比值是最高的,说明此设计的单位面积性能最好。而文献[3]和[8]的设计虽然性能十分优秀,但缺少抗攻击防护。综上,所提出的抗功耗攻击RSA 协处理器拥有最好的综合性能。

表1 抗功耗攻击的RSA 协处理器性能比较

4 结论

设计了一款抗功耗攻击的RSA 协处理器。该处理器通过指数随机化掩盖和添加伪操作的方法,可有效防御简单功耗分析和差分功耗分析攻击;结合CSA 加法器和2 层Karatsuba 乘法器实现的基256 免减Montgomery 模乘器,能够在不消耗过多面积的基础上提高RSA 的运算速度。跟其他类似工作相比较,本系统的性能资源消耗比具有一定优势。