基于FPGA的激光测距鉴相算法实现及优化研究

吴鑫渊,冯国英

(四川大学电子信息学院,成都 610065)

0 引言

激光角分辨力高、抗干扰能力强,可以有效避免微波贴近地面的多径效应和地物干扰问题,被广泛用于测距领域[1]。相位式激光测距作为一种高精度、非接触的测量方式,在大地、空间位置高精度测量等领域起着很重要的作用[2]。鉴相方法可分为模拟法和数字法两大类。模拟鉴相法适应鉴别信号的频率高,鉴相速度快,但是实现电路复杂、元器件要求高、精度差等缺点;数字法通过采样模拟信号转化为数字量进行鉴相,优化了硬件结构,测量精度高。近年来,基于高速采样和数字运算的数字鉴相方法越来越多的应用在工程中。数字法主要包括自动数字鉴相法、数字相关法和FFT鉴相法。由于激光回波信号受测量范围,光电探测器件等影响信噪比浮动较大,自动数字鉴相法误差较大;而数字相关法限制了鉴相范围为0~π;FFT鉴相法在进行频谱分析时,若信号频率不是频谱分辨率的整数倍,则会出现严重的频谱泄露和栅栏效应,造成鉴相误差[3],故工程中多采用FFT算法的改进算法全相位FFT算法进行鉴相。2012年中国科学院光电研究所缑宁祎等人设计了全相位FFT法的FPGA信号处理方案,利用傅里叶的变换共轭性实现了高速实时鉴相,在500 KHz测距速率,频率偏移1%时,鉴相精度可达0.09度[4],2015年该所张云雷等人在FPGA上实现了鉴相精度0.08度的双频测尺鉴相系统,通过控制两测尺之间的频差,有效降低了测尺之间的干扰,满足了大尺度空间中相位式激光测距的应用需求[5];2018年上海理工大学吴丹丹等人在CycloneⅤ系列FPGA上实现了FFT算法鉴相,在0-100 KHz测量带宽下,测量精度可达0.01度[6]。

目前,对于要求高速,实时且精度高的测距应用场景,还没有成熟的设计方案和相关产品,为了满足该领域的需求,文中硬件部分选择现场可编程逻辑器件FPGA,鉴相算法选择全相位FFT算法,在FPGA上实现了从AD采集,数据流缓存、处理到鉴相结果的输出显示,并基于整个系统数据处理流程提出了一种流水线式的数据处理优化方法。

1 全相位FFT鉴相原理

全相位FFT具有良好的频谱分析特性,能够有效地抑制频谱旁瓣泄漏[7];在能量中心多谱线范围内,具有信号初相的“相位不变性”[8]。相比于传统FFT,它不受信号频率必须为频率分辨整数倍的制约,在实际工程实践中,能显著提高测相精度。

全相位FFT相较于传统FFT法鉴相[9-10],增加了一个数据预处理过程,通过对采样数据的预处理得到一个新数字序列进行FFT变换。

设定初始信号频率为f,初始相位为θ,A为幅值,t为时间变量,初始信号为:

X(t)=Acos(2πft+θ)

(1)

设采样频率fn=1/ΔT,ΔT为采样时间间隔,n为采样点数,经过AD采样后得到信号的数字序列X(n):

(2)

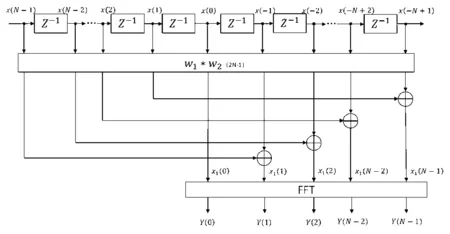

全相位FFT的数据预处理过程如图1所示。

图1 全相位FFT预处理框图

首先对2N-1个采样点进行预处理,过程如下:

(1)两个宽度为N的汉宁窗函数进行卷积得到新的函数w1*w2;

(2)新窗函数对中心样点为x(0)的2N-1个采样点进行加权:

P(n)=(w1*w2)·S(n),n=0,1,…,2N-1

(3)

(3)加权后的2N-1个采样点隔N相加得到新的N点序列:

Q(n)=P(n)+P(n+N),n=0,1,…,N-1

(4)

然后对新的N点序列Q进行傅里叶变换,并整理得:

(5)

其中k为傅里叶变换后的频率点序数,N为变换点数。可以得到信号的初始相位

(6)

2 鉴相系统仿真与设计

此鉴相模块应用的相位式激光测距系统如图2所示,大体分为激光调制发射端,激光回波接收端,FPGA鉴相模块以及电脑数据分析4个部分。激光调制发射端包含函数信号发生器、激光二极管以及准直透镜;激光回波接收端包含聚焦透镜及光电探测器模块;FPGA鉴相模块包含双路AD采集模块、FPGA算法设计模块以及液晶显示模块;电脑数据分析部分包含示波器以及电脑。系统工作流程如下,首先信号发生器发出高频调制信号调制激光二极管发射强度随时间变换的激光信号,经过反射物反射后,光电探测器检测反射的回波信号,进行信号整形、滤波、AD采集进入FPGA实现两路正弦信号的相位差计算;同时示波器采集探测器的输出信号,使用MATLAB软件进行数据分析并鉴相。

图2 相位式激光测距系统

2.1 仿真及验证

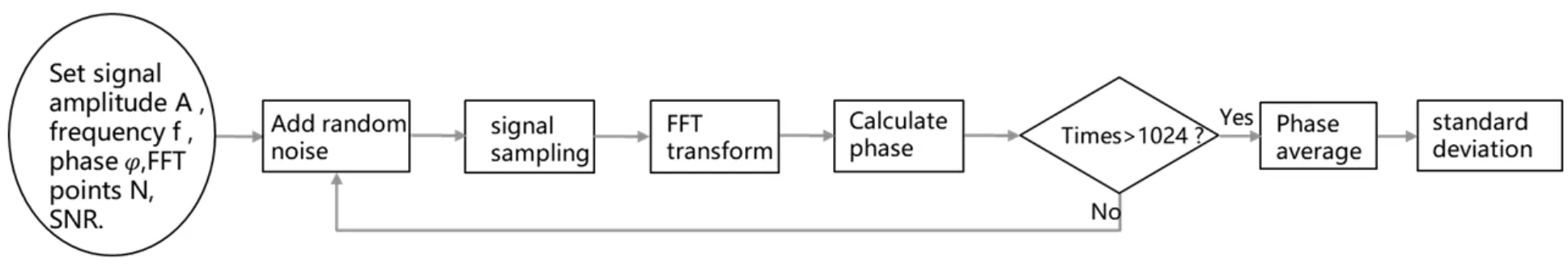

为了研究FFT变换点数,信噪比等因素对全相位FFT法鉴相的影响,通过控制变量的方法进行仿真设计,具体仿真流程如图3所示。设置初始信号为:

图3 仿真流程图

(7)

其中A为信号振幅,f为调制频率,P为初始相位(单位度),噪声干扰分为三类,一类为Dc直流信号干扰,另一类为谐波干扰,最后一类为用高斯函数模拟的随机噪声。仿真流程为先设置初始信号的幅值、初相、FFT变换点数并加入设定信噪比的随机噪声,经过采样,FFT变换加反正切求出单次的相位差,由于FPGA鉴相模块设置的平均次数为1024,所以这里每1024次计算求平均值,最终得出1024次鉴相的标准差,通过比较鉴相标准差判断不同条件对于鉴相结果的影响。

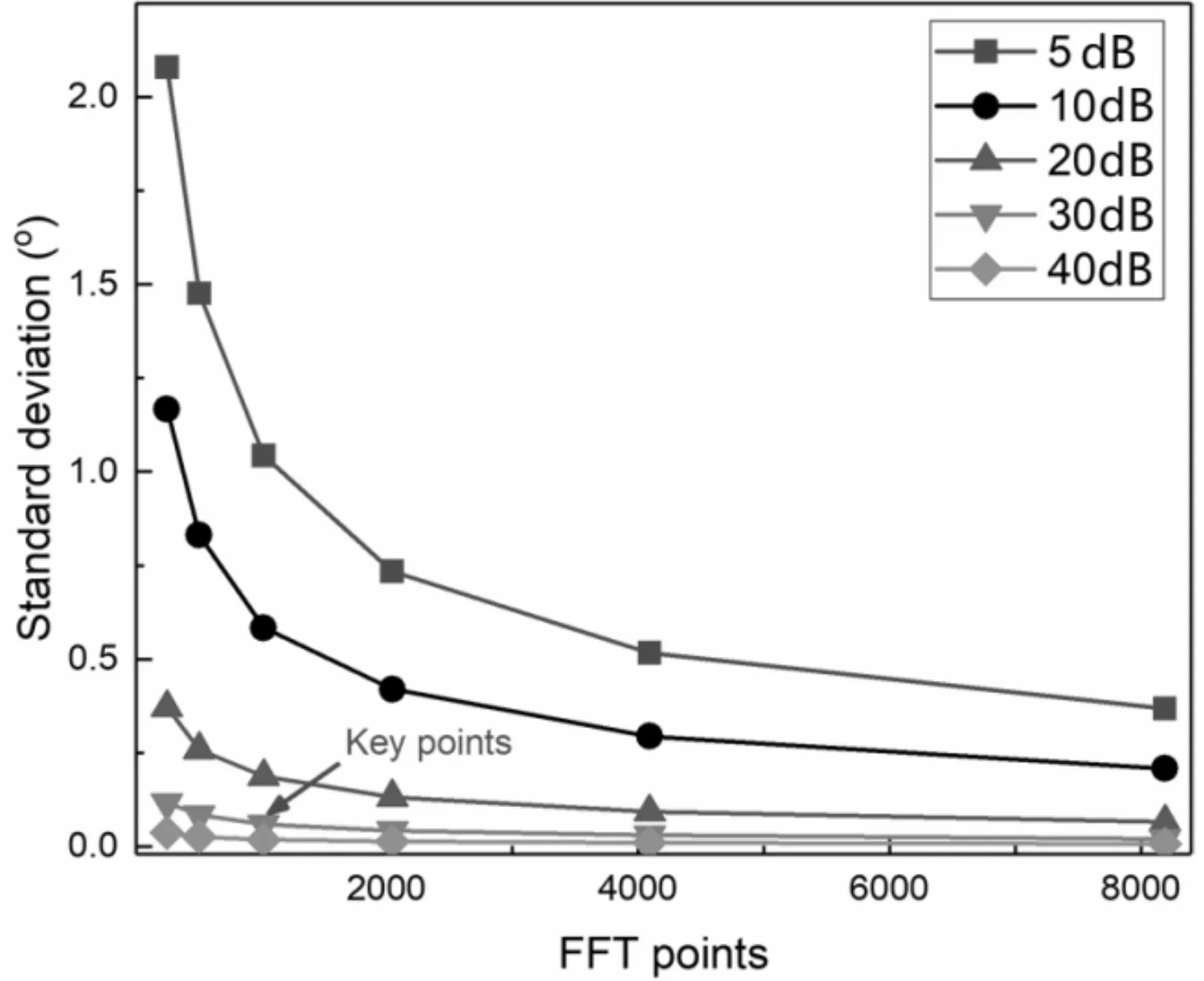

设置变量为信噪比和FFT点数,初始信号的调制频率f为10 MHz,初始相位φ为30度,采样频率fs为64 MHz(调制频率整数倍),信噪比的变化范围从5-40 dB,全相位FFT变换点数为511-4095点,1024次仿真求鉴相平均值和鉴相标准差。

仿真结果如图4所示,从图中可以看出随着FFT点数的增多,鉴相标准差明显减小,点数超过4095点之后,对鉴相标准差影响达到较小可忽略的程度;信噪比越大,鉴相标准差亦越小。考虑到具体实验环境(室内信噪比约为30 dB)和实验要达到的测距速率和精度,实际工程中选择了1023点全相位FFT点数进行鉴相算法设计,对应图中的关键点(FFT点数1023,信噪比30 dB),既满足了精度要求,也不会因为信号处理花费大量时间而影响鉴相速率。

图4 信噪比与FFT点数影响

2.2 FPGA鉴相模块设计

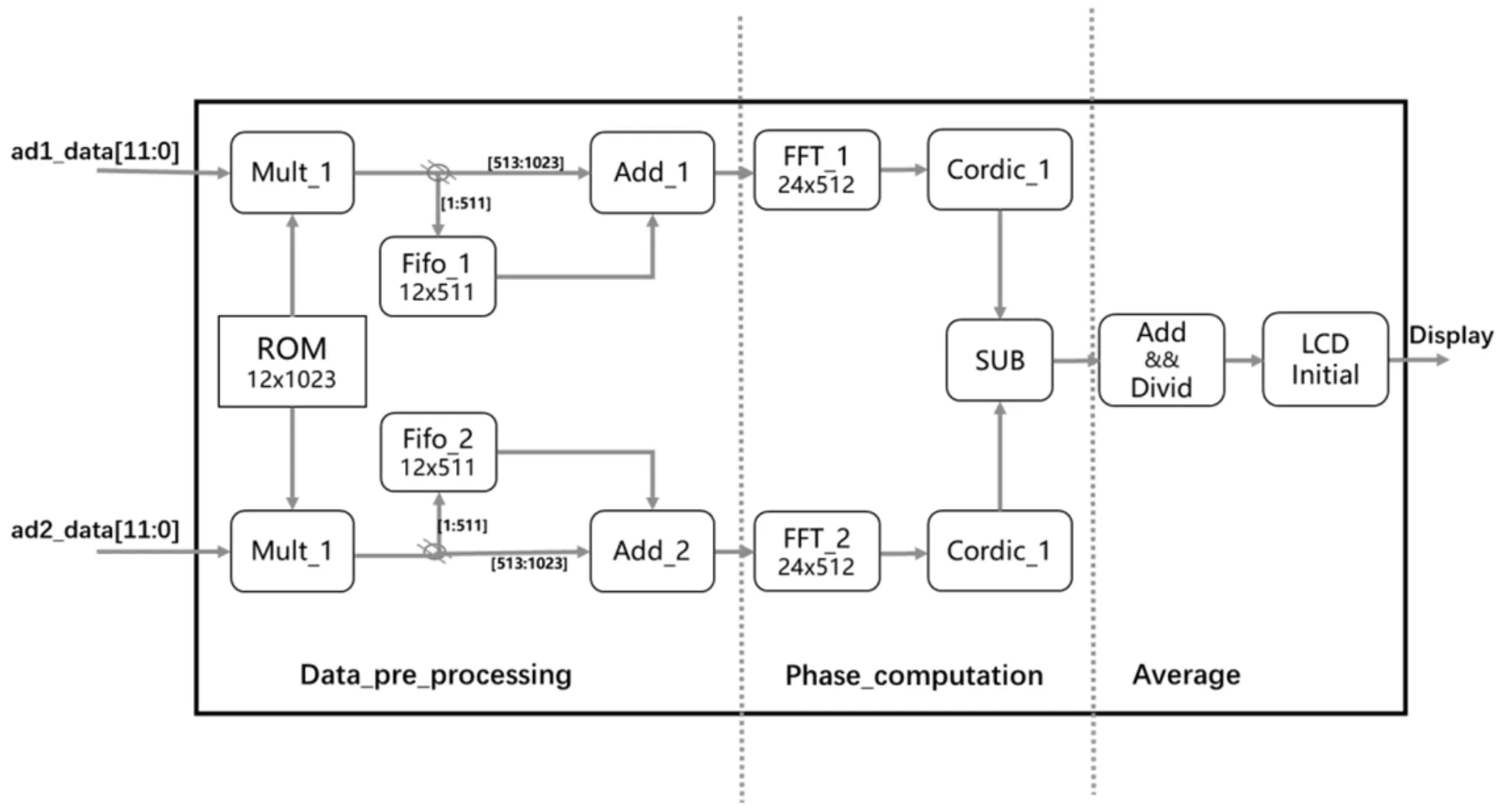

FPGA内部的设计框架如图5所示,主要分为三个部分,数据预处理模块、相位计算模块以及鉴相结果平均模块。数据预处理主要是FPGA与外部双路AD采集模块进行交互,得到两路12 bit的数据流,接着用含有窗系数的ROM IP核(经卷积汉宁窗系数初始化)对数据流加权,然后将数据流的前511个数据用FIFO缓存后与后511个数据隔N(N为变换点数)相加进行数据的预处理;计算相位的部分主要包含FFT和Cordic IP核的初始化与调用,将两路经过预处理的数据流进行FFT变换后,调用Cordic IP核进行反正切求出信号初始相位,最后将两路信号相位差得出;数据平均部分主要是将计算出的相位差缓存进行数据的平均以达到输出一个稳定的鉴相结果。

图5 FPGA设计框图

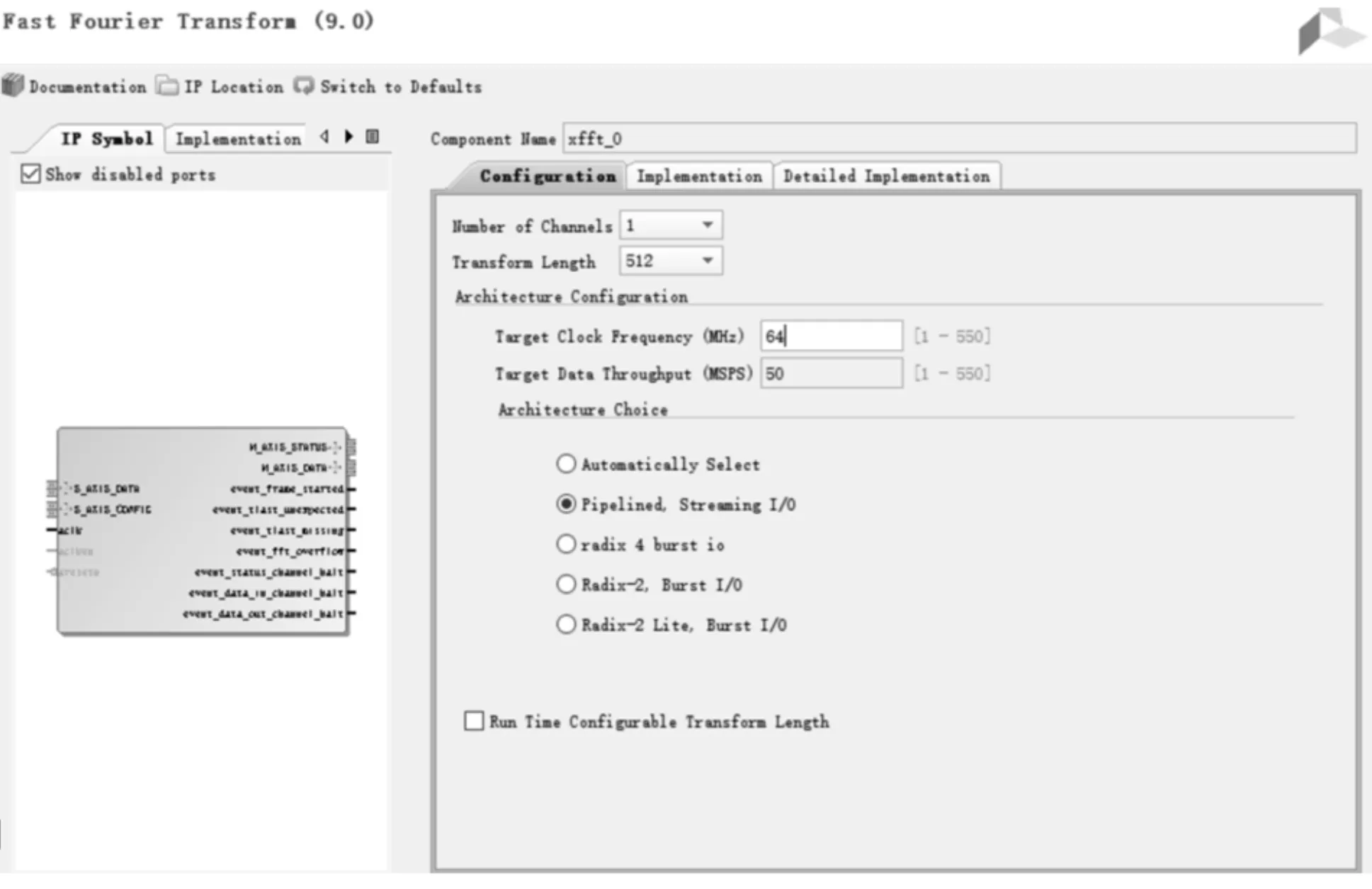

(1)FFT算法IP核设计

整个FPGA鉴相系统的最关键部分为相位计算模块,其中最主要的为FFT IP核的调用与设计。如图6所示,设置FFT的点数为512点,运算方式选择Pipelined Streaming I/O,速度最快,但占用资源较多,系统时钟及采样频率设置为64 MHz。

图6 FFT IP核设计

Xilinx FFT IP核采用的是AXI4-Stream总线,主要由master(信号开头为m)和slave(信号开头为s)两部分组成,生成后的IP核如图7所示,其中较重要的端口功能描述如表1所示。

图7 FFT IP核原理图

表1 FFT IP核端口功能描述

在设计IP核时,配置信息s_config_tadata尤为重要,其包含四个部分,分别为:

①NFFT,变换点数。该值为log2(point_size),由于变换点数为512,这里该二进制值为1001。

②CP_LEN,循环前缀,该值仅在循环前缀加入时有效,这里设置为0。

③FWD_INV,FWD_INV为0表示IFFT运算,为1表示FFT运算,这里为1。

④SCALE_SCH,缩放因子,这里经过多次测试,设置为二进制0110101010。

(2)流水线式数据处理优化及仿真

从图5可以得出,在FPGA处理流程的第三部分要进行鉴相结果的一个平均过程,文中提出了一种流水线式的数据处理方法,可以在进行多次平均的数据处理流程中,大大减少系统的数据处理时间,提高系统鉴相速率。

图8可以形象地反映出在数据平均过程中此优化方法节约时间的原理,一次鉴相循环包含三个信号处理过程,三种形状分别代表信号预处理过程,FFT IP核运算过程以及Cordic IP核运算过程,红线上方为未经过优化的数据处理流程,下方为优化后的流程,通过在循环求平均的过程中复用数据预处理和Cordic IP核运算时间,达到节约整个系统的时间成本。

图8 信号处理流程优化

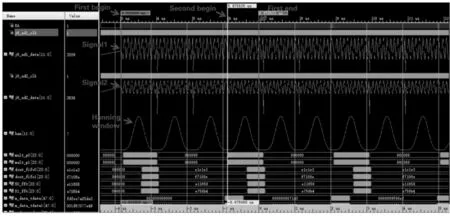

为了尽可能切合实际,在进行FPGA级仿真时,设置的参数基本与实际测距参数一致,设置系统时钟64 MHz,AD采样速率与系统时钟一致,仿真的正弦波信号使用MATLAB进行模拟,双路正弦波信号频率为10 MHz,信噪比设定为30 dB,双路信号相位分别设置为30度和45度,仿真时将全相位FFT点数设定为63个点,这样即大大减少了仿真时间且能在FFT后频谱谱线的10 MHz处存在一个参考点,便于采样计算相位。

在FPGA级的仿真时,其中耗时最长的过程为进行FFT运算,因为处理的数据越多,FFT的时间越长,仿真时32点的FFT需要的处理时间为2.83微秒,实验时的512点FFT需要的处理时间为25微秒,鉴相速率为20 KHz。所以在进行流水线式设计时把第二次循环开始的时间点设置到上一次FFT运算结果刚开始输出的时间点,从而可以避免两次循环导致FFT IP核的一个共用情形,且可以节约FFT运算后数据处理的时间。

在图9的仿真结果图中,Signal1,2分别为采样后的两个正弦波信号,Hanning window为初始化的窗函数,三条标记线分别为第一次鉴相循环的起点标记线,第二次循环的起点标记线以及第一次循环的结束标记线,从底边刻度可以看出,进行一次循环的时间大约为3.83 μs,优化后的两次循环的间隔时间大约为2.96 μs,可节约时间0.875 μs,约占一次循环时间的百分之三十,实际测试中,一次循环时间为30 μs,在1024次平均过程中,可节约时间约9.2 ms,由此可见,在进行大规模的平均过程中,节约的时间成倍增长,此流水线式的数据处理流程可大大节约系统的计算时间,提高整体鉴相速度。

图9 FPGA仿真结果

3 实验及数据分析

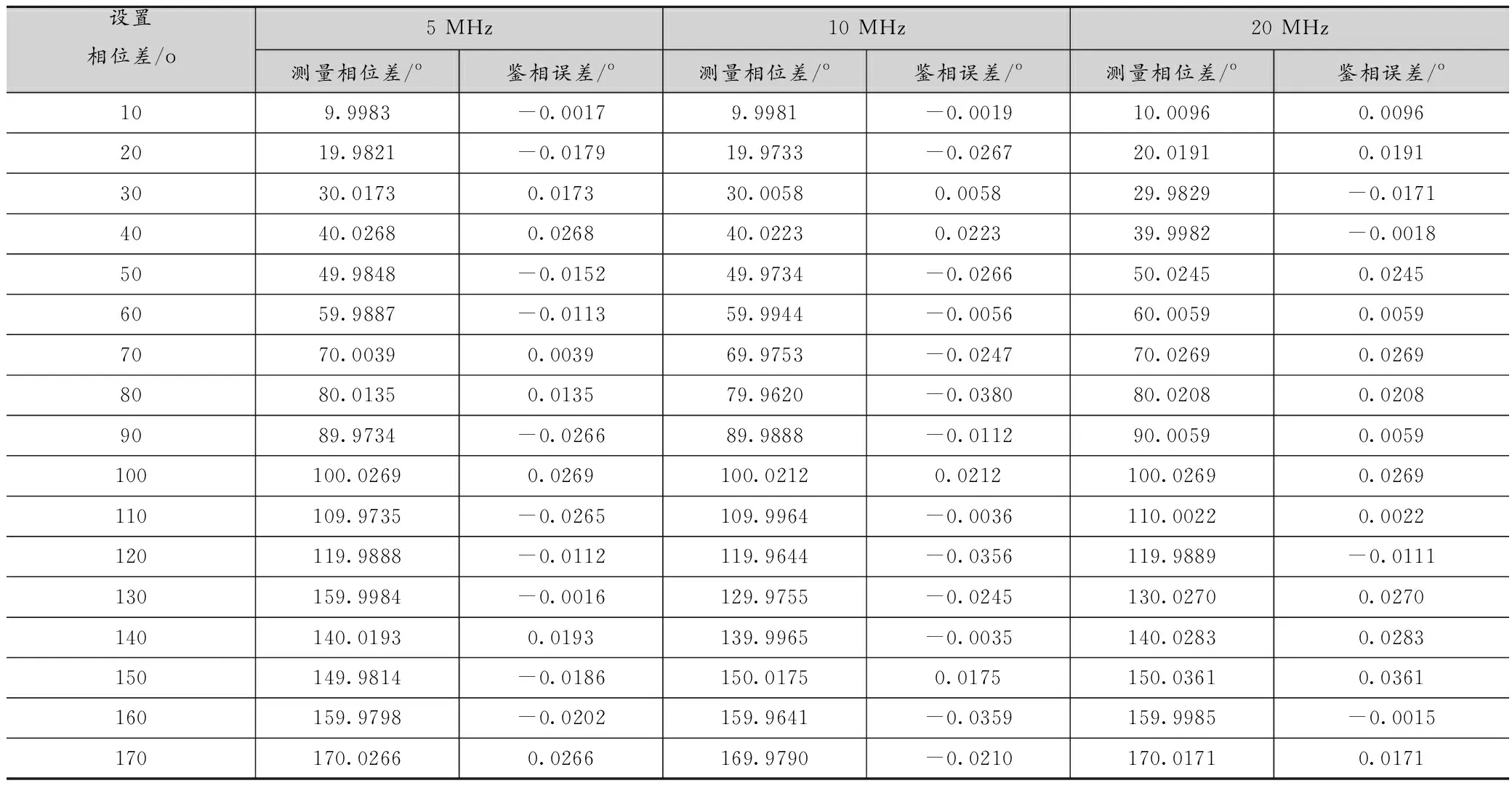

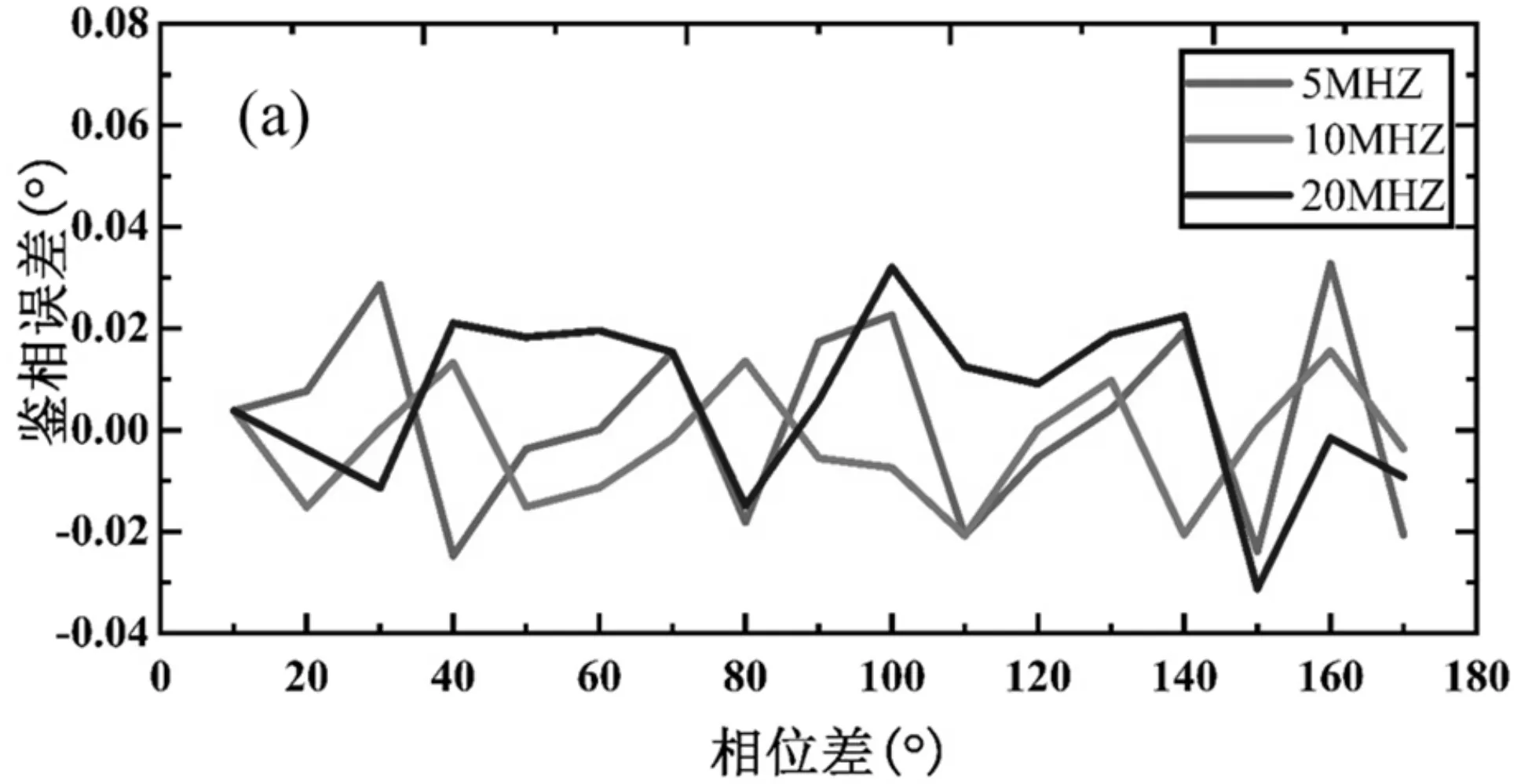

本节将对FPGA鉴相模块进行测试及功能验证,验证流程为:通过信号发生器(型号为普源DG1000Z系列)产生两路频率相同,相位不同的正弦波信号,由双路AD模块采样并由FPGA进行相位差检测及显示。产生的正弦波信号类型由有两种,一种为没有直流偏置,幅度为3V的正弦波;另一种正弦波信号幅度为2V,并加上3V的直流偏置。由于激光二极管工作时的调制信号为直流偏置加上正弦波,第二种类型正弦波信号则是为模拟实验时调制激光的正弦波信号。两种类型的信号都分别测试3组不同频率,分别为5 MHz、10 MHz、20MHz(AD采样频率64 MHz),每组信号从0-180度每隔10度变化,每次测量1024次,再进行相位差及鉴相误差的计算。表2和表3分别为两种类型不同频率输入信号的鉴相结果及鉴相误差。

表2 无直流偏置输入信号的鉴相结果及误差

表3 有直流偏置输入信号的鉴相结果及误差

如图10所示,可得出以下结论:此鉴相系统在不同频率的输入信号下,鉴相结果无明显区别,鉴相误差基本保持在±0.04度以内;输入信号有无直流偏置时对鉴相结果基本无影响,符合实际激光测距中的实际应用需求。

图10(a)无直流偏置输入信号鉴相结果(b)有直流偏置输入信号鉴相结果

4 结语

本文为了满足高速高精度的激光测距应用场景,在FPGA中实现了全相位FFT的鉴相算法,并通过仿真分析不同SNR和FFT变换点数下的鉴相标准差,对比实际实验环境,选取了最符合条件的实验参数;同时在整个数据计算流程中提出了流水线式的数据处理优化方法,通过FPGA仿真及实验证明该方法可大大节约鉴相时间。实验结果表明,该鉴相系统可在激光调制频率为20 MHz的条件下,鉴相速率达到20 KHz,鉴相精度达到0.04度以下,基本达到高速高精度的测距场景应用需求。