应用于MOEMS集成的TSV技术研究*

胡正高,盖 蔚,徐高卫,罗 乐

(1.中国科学院上海微系统与信息技术研究所,传感技术联合国家重点实验室,上海 200050;2.中国科学院上海微系统与信息技术研究所,信息功能材料国家重点实验室,上海 200050;3.中国科学院大学,北京 100049)

作为典型的微光机电系统(MOEMS)之一,微镜阵列(MMA)被用于许多宏观光学领域[1],其中扭转镜因其优异的动态响应性能而广泛应用于微光刻技术[2]。大阵列是微镜装置发展的方向之一,将扫描所需的较大的光学表面细分成较小的镜元可带来更高的固有频率,更大的倾角以及更低的驱动电压和更小的平动。然而,镜元数目增加的同时也会带来I/O数量的增加。对于64×64微镜阵列,其I/O数量超过16 000,如此规模的I/O数量给MMA和高压ASIC(HV-ASIC)之间的互连带来了挑战。

随着高密度集成、低功耗和高带宽密度等需求的持续增加,越来越复杂的互连技术需要被开发。三维(3D)集成由于具有功耗低、形状因数小、性能高、功能密度高等优点,被认为是一种新型解决方案[3-6],它通过缩短互连的长度来满足低延迟和低功耗的互连需求。为了实现三维(3D)集成,需要几个关键技术,如硅通孔(TSV),晶圆片减薄,拿持,以及晶圆/芯片的键合。其中TSV由于具有缩短连接路径,实现最短和最多样化的Z方向互连、减小封装面积的优点,被认为是三维(3D)集成的核心[7-9]。TSV的制备主要包括激光钻蚀[10]、深反应离子刻蚀(DRIE)[11]以及湿法腐蚀[12]。激光钻孔不适用于小孔径、高深宽比的通孔制作,湿法腐蚀通孔占用面积大、反应速率不易控制,DRIE刻蚀通孔其工艺可控,通孔深宽比高。TSV的填充材料主要包括液态金属[13]、铜(Cu)[14]以及多晶硅(Polysilicon)[15],其中铜(Cu)的填充应用最广。

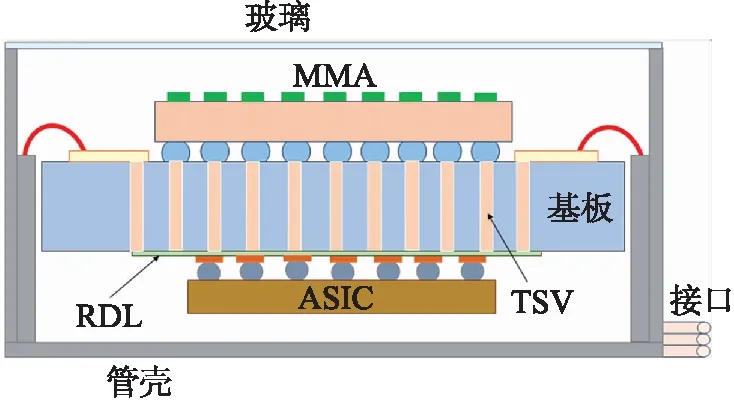

为了解决MMA和高压ASIC(HV-ASIC)之间的高密度互连问题,可通过TSV技术,将硅基板正面电极引到背面,然后在基板正反两面分别贴装MMA芯片和HV-ASIC芯片,实现MMA芯片与HV-ASIC芯片的互连,其方案如图1所示。该MMA单元有如下特点:①MMA芯片面积大(64mm×64mm),I/O数量多(>16 000),因此与之对应的TSV数量大,且TSV互连的均匀性要求高;②高压ASIC驱动MMA时功耗较大,产生热量较多,而整体结构对温度控制要求较高,因此通过TSV对整体结构的散热需求大。综上,该方案的核心在于TSV的制备与无缺陷填充。目前关于TSV的制备与填充已有较多文献报道,但对于这种高密度、高可靠性、高散热需求TSV的应用很少报道。本文对应用于微光机电系统(MOEMS)集成的TSV工艺进行了研究,采用深反应离子刻蚀TSV,使用热氧化进行TSV的绝缘,利用电镀铜(Cu)实现TSV的无缺陷填充,最后对无缺陷填充的TSV进行电学表征,包括TSV的导通和电阻测试、TSV电容测试以及TSV漏电流测试。

图1 MMA单元的3D集成示意图

1 TSV制作工艺流程

基于DRIE刻蚀速率可控,刻蚀深宽比高等优点,本文采用DRIE进行通孔刻蚀。DRIE刻蚀通孔主要有两种方式:直接刻蚀形成通孔;刻蚀形成盲孔,然后背部减薄至通孔漏出。由于MMA芯片面积大(64 mm×64 mm),其与硅基板的热应力问题需要考虑,因此基板厚度很关键,若基板太薄,一方面在制作过程中容易碎片,另一方面由于热应力的存在,硅基板将发生严重翘曲,影响可靠性。因此最终选择直接刻蚀来形成通孔。

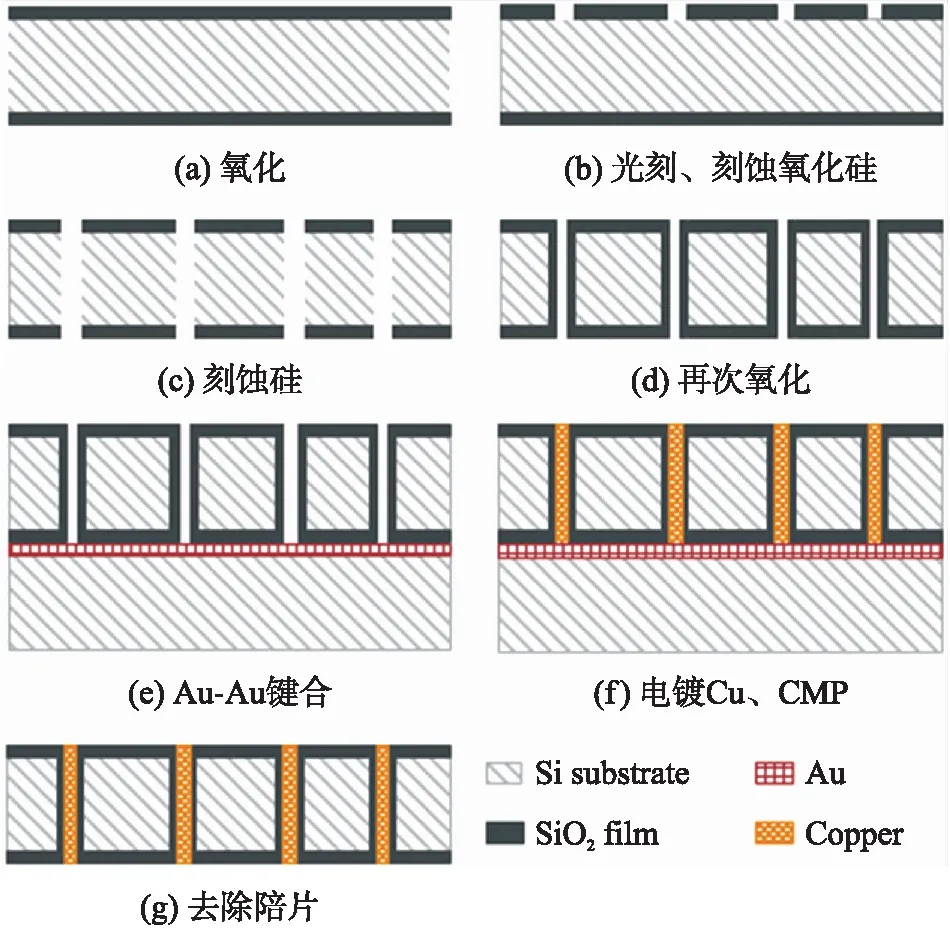

硅基板的主要制作工艺流程如图2所示,具体制作过程如下:①在双抛低阻硅片上首次生长氧化层,其厚度为2 μm,如图2(a)所示;②在硅片正面光刻,去除窗口中的氧化硅,如图2(b)所示;③利用电感耦合等离子体深刻蚀技术(ICP-DRIE)对硅片正面进行干法刻蚀,直至通孔被刻穿,如图2(c)所示;④采用BOE溶液(Buffered Oxide Etchant)去除硅片正反面上残余的二氧化硅层,重新进行热氧化形成二氧化硅层作为TSV的绝缘层,如图2(d)所示;⑤将TSV硅片与裸支撑硅片的Au层面进行金-金键合,以形成电镀种子层,如图2(e)所示;⑥对TSV进行铜电镀填充,待填充完成后,进行化学机械研磨(CMP)处理,如图2(f)所示;⑦去除裸支撑硅片,如图2(g)所示。

图2 硅基板制作工艺流程图

2 实验

2.1 TSV的刻蚀与绝缘隔离

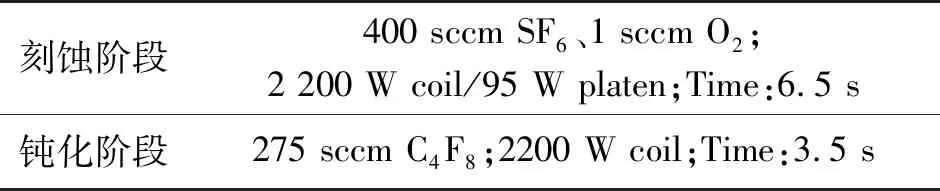

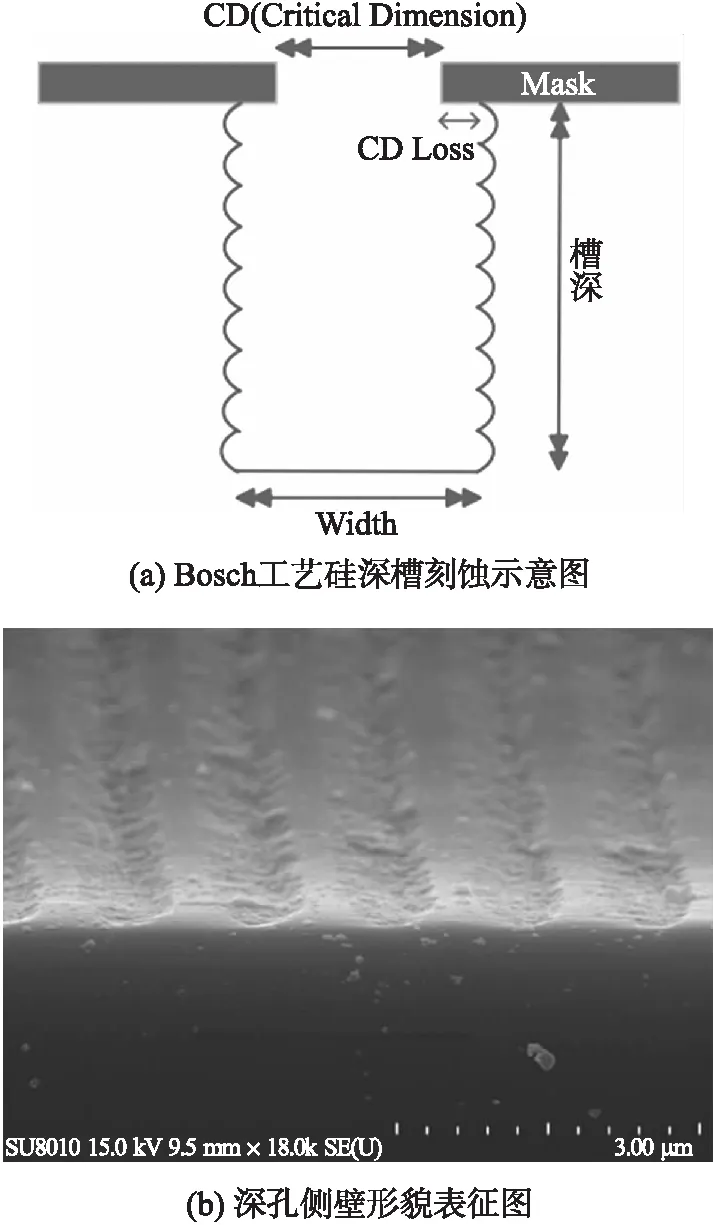

实验中选用4英寸N型的<100>双面抛光硅片,硅片厚度为(425±5)μm,电阻率为3 Ω·cm~8 Ω·cm,通孔直径为100 μm,间距500 μm。利用电感耦合等离子体深刻蚀技术(ICP-DRIE)对硅片正面进行干法刻蚀,采用刻蚀和钝化交替进行的Bosch工艺,实现对侧壁的保护,最终形成高深宽比的TSV。

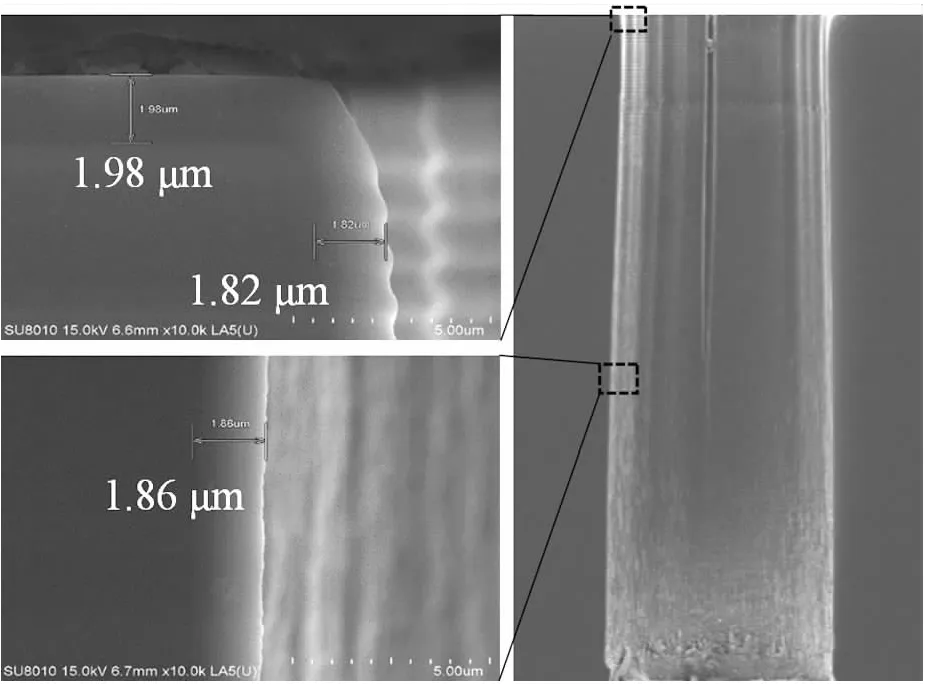

在Bosch工艺中,聚合物对侧壁起到了钝化保护作用,但是每一个循坏刻蚀的过程中会形成扇贝纹结构,如图3(a)所示,并且刻蚀过程会造成横向钻蚀,从而产生线宽损失(CD Loss),导致制作的TSV直径偏离理论值。通过优化工艺参数,如表1所示,可以将侧壁波纹的起伏控制在较小范围,如图3(b)所示。ICP-DRIE过程中刻蚀和钝化阶段SF6和C4F8的流量分别为400 sccm和275 sccm,一个周期内,刻蚀时间和保护时间分别为6.5 s和3.5 s。

表1 BOSCH刻蚀工艺的实验参数

图3 Bosch工艺深孔刻蚀示意图侧壁形貌表征图

对于垂直形貌的TSV,其侧壁一般采用淀积SiO2或者旋涂有机介质层进行绝缘处理,而淀积SiO2的台阶覆盖性差,旋涂有机介质层的TSV通常为环形孔,其结构较常规TSV更为复杂。实验中的TSV为常规通孔TSV,为保证其侧壁绝缘,最终采用热氧化法形成一层2 μm厚的SiO2。通孔边缘及中间部位氧化层厚度如图4所示,其厚度均在2 μm左右,具有一致性。

图4 通孔边缘及中间氧化层厚度

2.2 TSV的填充

本文采用金-金键合及bottom-up电镀方式对TSV进行填充。圆片级金-金键合的主要作用是为电镀通孔时提供种子层。实验中使用SUSS SB6E晶圆键合机,采用3 000 mbar的键合强度,300 ℃的键合温度,将TSV硅片与裸支撑硅片的Au层面进行金-金键合,以形成电镀种子层。

由于种子层存在于通孔底部,这就要求电镀液必须充分浸润通孔,但当通孔深宽比较高时,毛细现象较严重,电镀液无法充分浸润整个通孔,导致TSV电镀无法进行。因此,实验中一方面采用配备循环搅拌喷嘴的电镀槽,通过喷嘴对电镀液的喷射,使电镀液尽可能的进入通孔底部;另一方面,在电镀之前,将圆片进行真空处理,使电镀液充分浸润整个通孔。

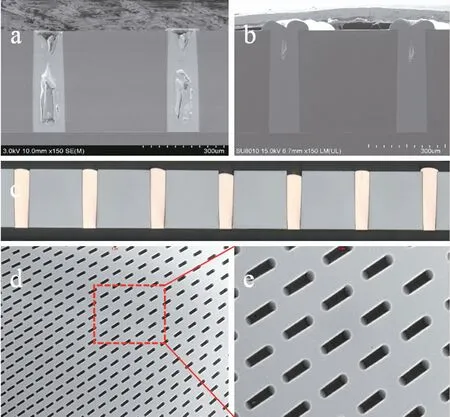

图5 不同工艺参数条件下TSV电镀结果

本文在甲基磺酸铜系电镀液和特殊添加剂的作用下对高深宽比的垂直通孔进行电镀,铜离子的质量浓度为55 g/L,甲基磺酸的质量浓度为10 g/L,氯离子的质量浓度为50 mg/L,有机添加剂的配方为加速剂∶抑制剂∶平坦剂=3 mg/L∶10 mg/L∶7 mg/L。图5为不同工艺参数下的TSV电镀结果,1ASD电流密度下,通孔中存在较大空洞,如图5(a)所示;0.6ASD电流密度下得到的填充效果较之前有明显改善,虽然空洞仍然存在,但空洞明显减小,如图5(b);先在0.6 ASD的条件下电镀一段时间,然后改用0.5 ASD的电流密度进行后续电镀的结果如图5(c)所示,此时从其截面图可以看出TSV无空洞存在,为了进一步验证TSV填充效果,利用X光检测仪对其进行检测,其结果如图5(d)、5(e),从中可以看出TSV填充完好,内部无空洞、缝隙等缺陷。

上述结果表明前期采用小电流密度有助于TSV的无缺陷电镀,分析原因如下:TSV的电镀是三种添加剂共同作用的结果,其中起关键作用的是加速剂和抑制剂。加速剂主要分布在铜表面及深孔底部,可降低电镀反应的电化学电位和阴极极化,从而加速沉积速率。抑制剂主要分布在通孔开口及硅表面,抑制该部分铜的沉积。若电镀初期采用大电流,将使加速剂的吸附能力提高,从而增加其在通孔开口处的覆盖率,导致抑制剂失效,最终使通孔开口处的沉积速率大于底部形成空洞。图5(b)之所以在通孔开口附近出现空洞,是因为随着电镀的进行,开口尖端部分电流密度增大,加速剂覆盖率增加使抑制剂失效,最终形成空洞。因此,为了避免空洞的形成,实验中采用减小电流密度的方法可减弱加速剂的吸附能力,进而保持抑制剂的作用,最终形成无缺陷的TSV。

3 TSV的电学特性

3.1 电阻

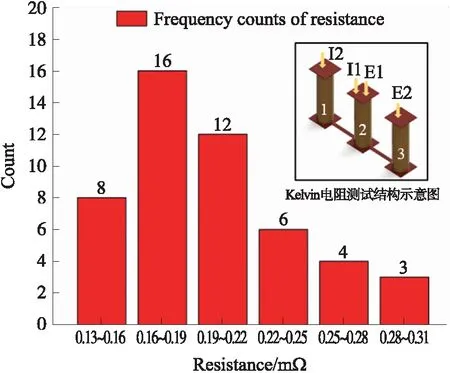

在TSV制作完成后,对其进行电阻测试,电阻采用Kelvin测试法,其优点在于,可以去除探针的接触电阻带来的误差,得到精确地电阻测量结果。具体测量示意图如图6插图所示,I1和I2用来测量电阻两端的电流值I,E1和E2用来测量电阻两端的电压值VRS,被测电阻R即为电压值VRS和电流值I的比值。

图6 TSV电阻分布

随机选取50个TSV分别进行电阻测试,测试结果如图6所示,结果发现50个TSV中有一个TSV不通,TSV导通率为98%。其余导通TSV的电阻值范围为0.130 Ω~0.294 Ω,平均值为0.199 Ω,单个TSV的电阻值分布,基本上呈正态分布,其中处于0.16 Ω~0.22 Ω的样品最多,在总样品数一半以上。实验中测得的单个TSV平均电阻值相比2017年佐治亚理工学院提到的1.2 Ω[16],其数值更小,电学性能更好。TSV无法实现导通主要有两个原因:极个别通孔内部没有被电镀液完全浸润,导致电镀无法进行,造成TSV不通;电镀过程中局部区域的电流密度分布不均,导致少数通孔内存在大量缺陷,造成TSV不通。

3.2 电容和漏电流

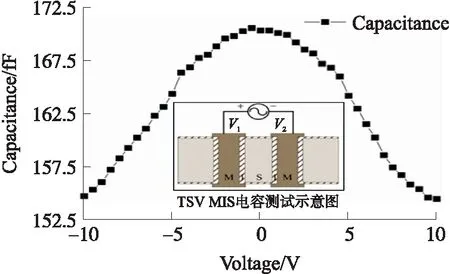

TSV结构可以看成是金属(铜)-绝缘介质(SiO2)-半导体(Si)(MIS)结构。TSV这种典型的MIS结构一方面会在金属和半导体之间产生漏电流,另一方面,会导致寄生的MIS电容。漏电流和MIS电容会导致信号延迟和功率损耗。因此,MIS电容和漏电流的测量很有必要。

MIS电容的测试结构如图7插图所示,相邻两个TSV构成了MISIM结构,左右TSV可以分别看作是ground-TSV和signal-TSV。利用HP4284A进行测量,在1MHz,偏置电压-10 V~10 V的条件下其测量结果如图7所示。C-V曲线基于零伏对称,当偏压为零时,达到最高点,此时电容为170.45 fF,单个TSV寄生MIS电容值在100 fF左右,与现有报道结果一致[17];当偏压为正时,电容随偏置电压的增大而减小;当偏压为负时,电容随偏置电压的减小而减小。测试结果与signal-ground TSV电容耦合理论一致[18]。随着偏置电压的增加,signal-TSV的电容从积累区到耗尽区,最终到反型区,ground-TSV的电容则从反型区到耗尽区,最终到积累区。由于signal-ground TSV结构中每个TSV的C-V曲线一致,因此signal-ground TSV的C-V曲线关于V=0对称。

图7 TSV C-V曲线

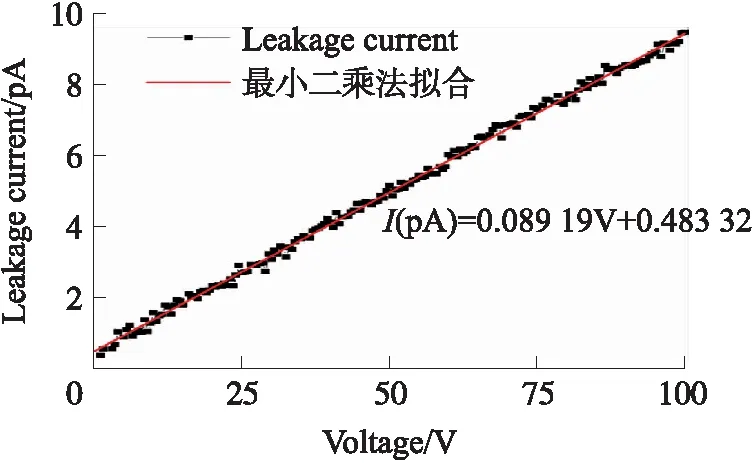

漏电流利用Agilent 4156C进行测试,加载电压为0~100 V,测试结果如图8所示。漏电流I与加载电压V线性相关,随着加载电压V的增加,漏电流I随之增加,当加载电压V为100 V时,漏电流I为9.43 pA。I-V关系基本符合I(pA)=0.089 19V+0.483 32曲线,表明TSV的绝缘电阻大约为11.21 TΩ,其结果远大于[15]提到的10 GΩ,说明其具有很好的绝缘特性。

图8 TSV I-V曲线

综上,制备的高密度TSV在导通性及侧壁绝缘性上均达到了较好的效果,具有良好的电学特性。

4 结论

本文对应用于MOEMS集成的TSV工艺进行了研究。通过ICP-DRIE获得了具有较小扇贝纹的陡直TSV通孔;通过热氧化获得了2 μm厚的侧壁绝缘层;通过金-金键合及bottom-up法,在甲基磺酸铜系电镀液下实现了TSV的无缺陷填充;对填充后的TSV进行电学表征,测试结果表明,单个TSV的电阻平均值为0.199 Ω、相邻两个TSV的电容在无偏压时为170.45 fF、TSV的漏电流在100V时为9.43 pA,具有良好的电学特性。