核磁共振测井仪高压发射控制时序设计与应用

钟剑, 李梦春, 杨德龙, 师光辉, 黎晗, 李斌

(1.中国石油集团测井有限公司, 陕西 西安 710077; 2.中国石油天然气集团公司测井实验基地, 陕西 西安 710077)

0 引 言

随着非常规复杂储层油气资源勘探开发,测井技术面临着复杂储层划分、孔隙结构精细评价、流体性质识别等难题,对核磁共振测井仪器提出前所未有的要求和挑战[1-4]。核磁共振测井仪获取的测井信息几乎不受骨架岩性影响,在储层孔隙结构划分和流体性质识别等方面具有独特的优越性[5-6]。核磁共振测井仪高压发射的控制直接影响地层氢核扳转情况和地层核磁共振回波信号幅度,如果高压发射不能准确控制,就难以准确获取地层真实信息,从而影响地层的评价效果[7-8]。核磁共振测井仪工作主要依靠CPMG脉冲序列,精确控制90°脉冲扳倒和180°脉冲扳倒,实现核磁共振回波信号测量,高压发射控制关键是如何产生初始相位和频率不断变化的2路正交正余弦信号。目前,国外核磁共振测井仪大都采用专用的DDS芯片实现初始相位和频率可控的2路正交正余弦信号,但一般DDS芯片体积大,成本高,趋于淘汰,难以满足高端新仪器研制需求。本文根据核磁共振测井仪高压发射控制原理,借助于高集成、高速度、大容量现场可编程门阵列FPGA,采用Verilog语言进行DDS模块软件设计[9-11],替代专用的DDS芯片,产生初始相位和频率不断变化的2路正交正余弦信号,实现核磁共振测井仪高压发射准确控制。

1 高压发射控制原理

核磁共振测井仪高压发射,主要由主控系统产生的2路正交正余弦信号,控制激励模块产生4路驱动信号,进而控制高压发射器产生高压脉冲大功率信号,由发射滤波器去除谐波信号,再经天线接口模块对高压进一步放大和合成,最终形成大功率高压脉冲信号通过天线发射至井眼周围地层。由此可知,准确产生2路正交的正余弦信号,对核磁共振测井仪高压发射控制至关重要。为准确获取地层信息,核磁共振测井仪一般都采用多回波间隔时间TE、多等待时间TW和多工作频率相结合的测井观测模式,其中多频率工作模式,对高压发射控制提出了更高要求,即控制高压发射的2路正交正余弦信号频率不断变化。由于核磁共振测井数据处理特殊性,高压发射控制时序还必须保证2路正交信号初始相位不断切换,即0相位和1相位交替切换,以便采用PAPS处理技术,提取出核磁共振原始回波信号和噪声,进行后续的测井数据处理与解释。

2 DDS设计

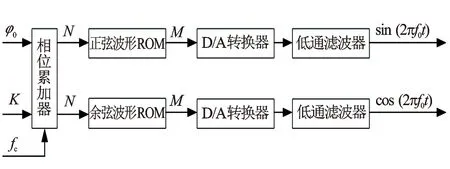

DDS的基本工作原理是利用幅度和相位的对应关系,在固定频率时钟控制下,通过改变频率控制字改变相位累加器的累加速度,得到不同相位累加值,再取样不同的相位累加值作为地址,对存储波形ROM进行寻址,得到与相位累加值对应的幅度序列,经D/A转换器进行数模转换,利用低通滤波器进行高频滤波处理,即可产生所需频率的波形信号。

由于核磁共振测井仪工作频率一般为500~800 kHz,DDS输出的最高频率不能超过时钟频率的40%,时钟频率设为22.5 MHz,能够满足核磁共振测井仪工作频率要求。频率控制字K由相位累加器的位数n、时钟频率fc和合成输出信号频率f0所决定,表达式为

(1)

DDS的设计核心是相位累加器设计,从提高运算速度和节约资源方面考虑,设计没有采用传统的相位累加器,而是基于流水线性技术,重新设计的32 bit相位累加器,采用9级锁存、8级加法实现。

D/A转换器采用12 bit高速数模转换器AD568SQ;正弦和余弦波形ROM利用相位累加器高8 bit作为ROM寻找地址,ROM采用12 bit数据输出,与12 bit的D/A转换器输入直接相连;以AD827SQ集成运放为基础,设计低通滤波器,滤除数模转换器输出波形信号的高频干扰噪声;DDS设计的基本结构框图见图1。其中,可以设置不同的初始相位φ0,K为频率控制字,fc为DDS的工作频率时钟,N为相位累加器输出位数,M为正余弦ROM输出数据位数,sin (2πf0t)和cos (2πf0t)为输出频率为f0的2路正交正余弦信号。

图1 DDS设计的基本结构框图

3 仿 真

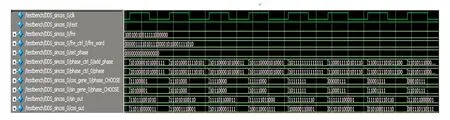

在Actel Libero IDE v9.1软件开发平台上采用Verilog语言,以流水线性技术为基础,设计9级锁存、8级加法的32 bit相位累加器,在ModelSim软件上对32 bit相位累加器进行功能仿真(见图2),仿真时钟频率clk采用22.5 MHz,输出频率设置为600 kHz,可得到32 bit的频率控制字fre_word“0000 0111 1010 1110 0001 0100 0111 1010”,在一个时钟周期内,可以输出1次相位累加值,提高了传统累加器的运算速度,以相位累加值的高16 bit作为输出,满足32 bit流水线性累加器功能要求。

同样,在Actel Libero IDE v9.1软件开发平台上采用Verilog语言,设计DDS整体框图,主要包括频率控制字计算模块fre_ctrl、32 bit流水线性累加器模块acc_pipeline32、相位控制模块phase_ctrl、余弦产生模块cos_gene、正弦产生模块sin_gene。在ModelSim软件上对DDS整体设计进行功能仿真,仿真时钟频率clk采用22.5 MHz,输出频率fre设置为600 kHz,即“1001 0010 0111 1100 0000”,初始相位设为0,最终以2路正交的sin_out信号和cos_out信号输出,满足DDS整体功能要求。

图2 32 bit相位累加器功能仿真图

图3 DDS整体功能仿真图

图4 实际应用效果图

4 应用效果

将设计好的DDS模块移植到核磁共振测井仪主控系统上,在激励模块上测试正交的正余弦信号。通道1表示正弦信号,初始相位为90°,通道2表示余弦信号,初始相位为180°,通道1和通道2为2路正交的正余弦信号,满足核磁共振测井仪高压控制时序要求。

实际测井观察模式中,采用9种工作频率。0相位脉冲序列和1相位脉冲序列交替工作,其中0相位脉冲序列的90°扳倒脉冲初始相位为90°,180°扳倒脉冲初始相位180°;1相位脉冲序列的90°扳倒脉冲初始相位为270°,180°扳倒脉冲初始相位180°;回波间隔时间TE采用0.9 ms和0.6 ms;回波等待时间TW采用12.7 s和2 s;脉冲序列重复次数采用1次和24次。在实际测井应用中(见图4),发射功率B1值和增益值稳定,仪器测井工作正常,在2 248.0~2 255.3 m井段,差谱有显示,综合解释为油层;在2 249.0~2 255.0 m井段试油显示,产油9.3 t/d,效果明显。

5 结论及建议

(1) 基于流水线性技术,设计的32 bit相位累加器,满足核磁共振测井仪高速运算要求;设计的DDS模块具有多频率设置和初始相位设置功能,实际测试结果表明,满足核磁共振测井仪多频工作模式、0°相位和180°相位交替切换和高压发射控制时序要求。

(2) 设计的DDS模块能够替代专用的DDS芯片,减少仪器成本、简化仪器硬件电路,能为偏心核磁共振仪器、随钻核磁共振仪器、实验室核磁共振分析仪研制提供参考。

(3) 井下核磁共振测井仪控制时序错综复杂,应不断采用新方法和新技术进行优化改进。