15 μm/45 μm阶梯覆铜板上75 μm宽精细线路的制作

李晓蔚

(西安工程大学实验室管理处,陕西 西安 710048)

15 μm/45 μm阶梯覆铜板上75 μm宽精细线路的制作

李晓蔚

(西安工程大学实验室管理处,陕西 西安 710048)

提出了一种在15 μm/45 μm的阶梯板上制作75 μm宽精细线路的工艺。首先采用电镀铜工艺在15 μm铜厚的双面覆铜板的基础上制作15 μm/45 μm阶梯板,进而利用蚀刻补偿工艺制作75 μm宽的阶梯线路。通过线宽测量、微观形貌观察和蚀刻因子计算,对所制作的阶梯线路进行评价。结果表明,该工艺不仅能够保证制作的阶梯线路具有较高的精度与质量,而且生产成本较低。

阶梯覆铜板;线路;蚀刻补偿;铜厚;蚀刻因子

随着电子信息产业的发展,电子元器件越来越轻,体积越来越小,功能越来越多。这种现象影响了起连接作用的印制线路板,导致其布线密度越来越大,品种越来越多[1]。应用在发动机电源供应部分、汽车中央电器供电部分、大功率电器的高电压部分的印制线路板[2],要求其不同区域有不同厚度的线路。而提升线路精度是实现信号在高速传输过程中保持稳定以及低损耗的方法之一[3],因此需要在印制线路板上设计精细的阶梯线路。用传统的工艺制作精细阶梯线路存在以下问题:(1)由于板面铜厚的差异性,在两种不同厚度板面的交接处存在梯度差,导致干膜与板面贴合度差,在蚀刻时,蚀刻药水就会从干膜与板面的缝隙处渗入,造成板面线路开路、缺口;(2)由于蚀刻速率跟板面铜厚有关,因此在相同的蚀刻速率下难以保证阶梯线路宽度相同[4],而要想使阶梯线路宽度相同,需要两次蚀刻才能完成,这样便增加了阶梯线路制作的难度和工艺的复杂性,同时造成了线路板成本的增加。为了解决这个问题,深圳崇达[5]提出了一种制作阶梯线路的方法:首先在板面蚀刻出图形线路,然后用干膜覆盖不需要加厚的线路,最后对需要加厚的线路图形进行图形电镀。但是这种方法有明显的缺点:第一,在电镀阶段,由于线路很细,直接对线路进行电镀很难保证同一根线路铜厚的均匀性;第二,要保证阶梯处线路连接良好,对技术的要求非常高,并且成本很大,不适合大规模生产。

本文拟在自制的15 μm/45 μm阶梯板[4]上制作75 μm宽的精细阶梯线路。通过探究蚀刻补偿量与线宽的关系以寻求合适的蚀刻补偿量,继而应用到75 μm宽阶梯线路的制作过程中,期望得到一种低成本、高质量的阶梯线路制造方法,也为实际生产提供一定的理论指导。

1 实验

1.1 仪器及材料

LEE250型铜厚测试仪,天津顺诺;PT-I-I垂直电镀线,Facility;VeriSmart LDI曝光机,Orbotech;UH-DES 30M line水平显影+蚀刻+退膜线,宇宙;CSL-A25E自动贴膜机,志圣;GRC-7N自动涂布机,群翊;XK22线宽量测仪,爱思达;JX23金相显微镜,广东正业;XL30扫描电镜,Philips。

生益双面覆铜板(80 μm 1080PP +15 μm 铜箔),HITACHI DG38干膜(膜厚 28 μm),深乐健液态感光油墨,CuSO4体系电镀液,Na2CO3体系显影液,酸性CuCl2−HCl体系蚀刻液,NaOH体系退膜液。

1.2 阶梯板的制作

(1) 将铜厚为15 μm的双面覆铜板裁剪成为468 mm × 412 mm的规格。

(2) 在温度130 °C和压力0.5 MPa的条件下以1.7 m/min的速率在覆铜板表面热压干膜。

(3) 对上述覆铜板的234 mm × 412 mm区域进行曝光,曝光能量为45 MJ/cm2。

(4) 用显影液喷淋覆铜板露出的待电镀区域,显影速率3.8 m/min,上压力0.20 MPa,下压力0.17 MPa。

(5) 以1.3 A/dm2的电流密度对显影区进行电镀,时间70 min,使铜厚增加到45 μm。

(6) 使用退膜液褪去覆铜板表面干膜,此时所得到的阶梯线路板简称为15 μm/45 μm阶梯板。

1.3 蚀刻补偿的设计

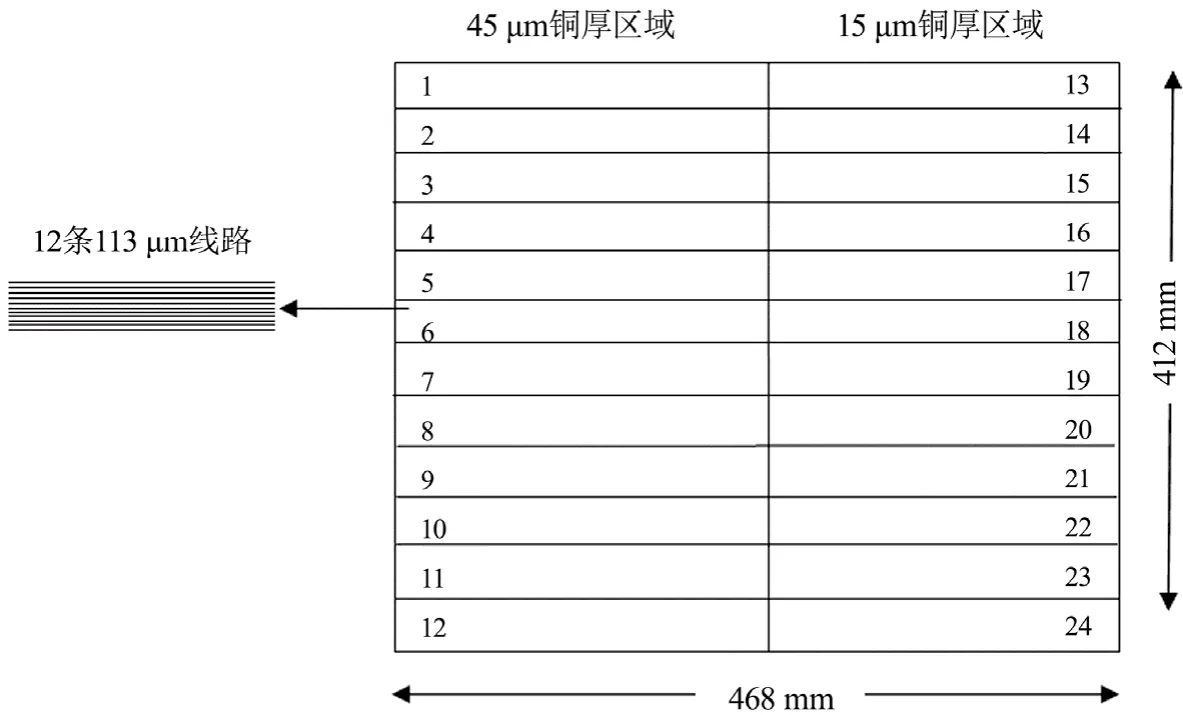

将15 μm/45 μm的阶梯板平均划分为234 mm × 34.33 mm的24个区,其中包含12个45 μm厚区域(依次编号为1−12)以及12个15 μm厚区域(依次编号为13−24),见图1。每个区域均设计有12根孤立线路。对于编号为1−12的区域,按式(1)设定蚀刻补偿量。例如6号区域,按式(1)算得其蚀刻补偿量为38 μm,即在蚀刻之前利用CAD设计的线宽为75 μm + 38 μm = 113 μm。对于编号为13−24的区域,按式(2)设定蚀刻补偿量x。

其中a1和a2分别是经过反复试验得出的15 μm和45 μm铜厚区域的原始补偿量,a1= 13 μm,a2= 38 μm;b是蚀刻补偿的步数,取5 μm;N是区域的标号。

图1 补偿实验的线路排版Figure 1 Layout of conductive lines for compensation experiment

1.4 阶梯线路的制作

按上述设计在15 μm/45 μm阶梯板上涂布液态感光油墨,曝光、显影后蚀刻、褪膜。相关工艺参数如下:涂布温度95 °C,涂布速率2.5 m/min,厚度约为8 μm;显影速率2.5 m/min,显影上压力0.22 MPa,显影下压力0.19 MPa;蚀刻速率2.0 m/min,蚀刻上压力0.25 MPa,蚀刻下压力0.22 MPa。

1.5 75 μm宽阶梯线路的制作

取3块按1.2节制作的15 μm/45 μm阶梯板,每块阶梯板表面平均划分为234.00 mm × 41.20 mm的20个区域,15 μm及45 μm铜厚区各10个,每个区域均设计30条线宽为75 μm的孤立线路(见图2)。按1.4节的流程制作线路后,随机从每个区域的30条线路中抽取5条进行检测。

图2 15 μm/45 μm 阶梯板上 75 μm线路的排版Figure 2 Layout of 75 μm-wide lines on a 15 μm/45 μm stair-stepped copper-clad laminate

1.6 检测方法

1.6.1 铜层厚度

采用铜厚测试仪对所制作的阶梯板上45 μm铜厚区的表面进行测量,然后选取不同的位置打磨切片,用金相显微镜测量铜厚。1.6.2 蚀刻因子

蚀刻因子是衡量精细线路品质最重要的指标。蚀刻因子越大,表明侧蚀越小,线路的横截面越近似于矩形,线路的质量越好[6];相反地,蚀刻因子越小,表明侧蚀越大,线路的横截面越类似于梯形,这将影响线路的阻抗[7]。蚀刻因子按式(3)计算,其中各参数的含义示于图3。

1.6.3 线宽及线路形貌

采用线宽测量仪测量线路宽度,利用扫描电子显微镜观察线路形貌。

2 结果与讨论

2.1 15 μm/45 μm 阶梯板厚度的检测

在所制备的阶梯板45 μm铜厚区表面随机选取15个点(如图4所示)来测量板面铜厚,结果误差在±3.5 μm范围内,满足工业生产的要求。图5为15 μm/45 μm阶梯板在金相显微镜下的截面照片。

2.2 线宽与蚀刻补偿之间的关系

如图6所示,线宽y的自然对数与蚀刻补偿量x线性相关。式(4)和式(5)分别为阶梯板上15 μm和45 μm铜厚区域的蚀刻方程。

在本文的实验条件下,15 μm铜厚的区域补偿62.15 µm,45 μm铜厚的区域补偿38.23 µm后,能够使蚀刻之后的线宽达到75 µm。

图3 蚀刻因子计算示意图Figure 3 Schematic diagram for calculating the etching factor

图5 阶梯板的金相截面照片Figure 5 Sectional metallographic image of the fabricated stair-stepped copper-clad laminate

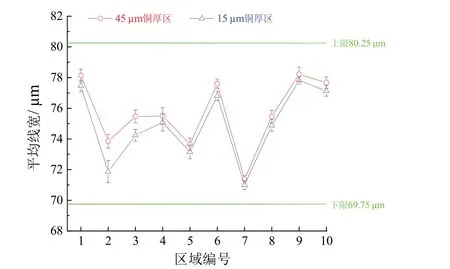

2.3 75 µm宽阶梯线路的质量评价

2.3.1 线宽的均匀性

印制电路企业一般要求线路宽度的误差不超过±7%,即要求75 μm的线路宽度控制在69.75 ~ 80.25 μm的范围内。由图7可知,阶梯线路中15 µm铜厚区域的线宽最大平均值为77.82 µm,最小平均值为70.99 µm;45 µm铜厚区域的线宽最大平均值为78.22 µm,最小平均值为71.37 µm。可见不同区域的线宽均在临界范围之内,符合制作要求。

图6 蚀刻补偿量与线宽之间的关系Figure 6 Relationship between etching compensation and line width

图7 15 μm/45 μm阶梯板不同区域上线路的平均线宽Figure 7 Average width of the lines located in different regions on a 15 μm/45 μm stair-stepped copper-clad laminate

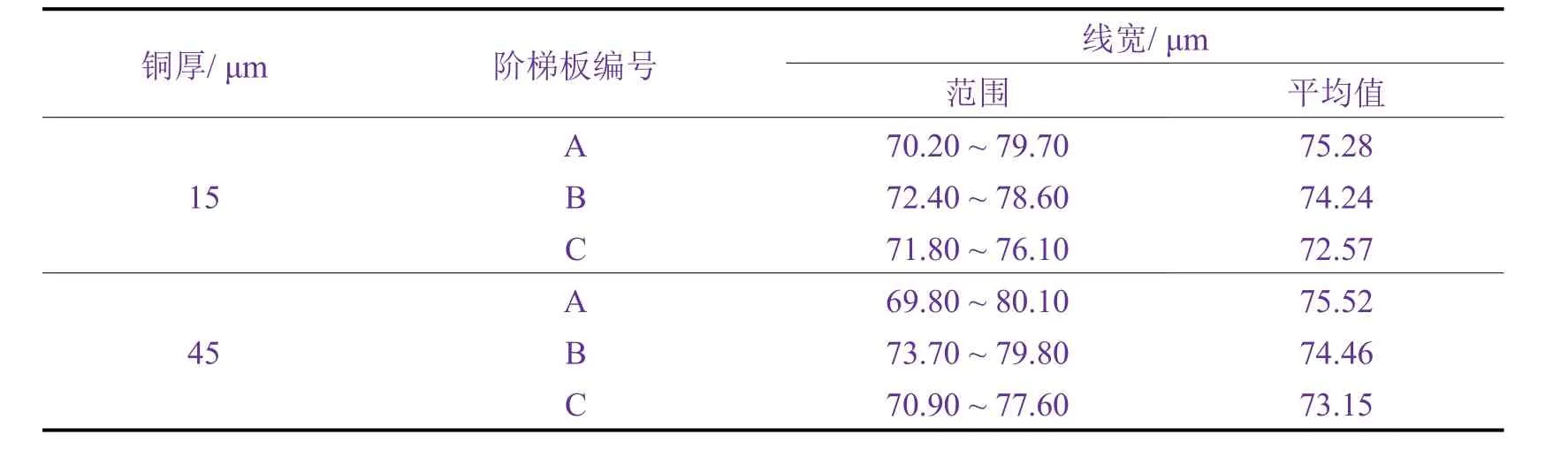

从表1可以看出,3块阶梯板上15 μm铜厚区的最大线宽为79.70 µm,最小线宽为70.20 µm,平均值在72.57 ~ 75.28 μm之间;45 μm铜厚区的最大线宽为80.10 µm,最小线宽为69.80 µm,平均值在73.15 ~75.52 µm之间。由此证明,本文所提出的工艺稳定性较好,可应用于大批量的工业生产。

表1 3块15 μm/45 μm阶梯板上阶梯线路线宽的比较Table 1 Comparison between the widths of lines on three 15 μm/45 μm stair-stepped copper-clad laminates

2.3.2 线路的微观形貌

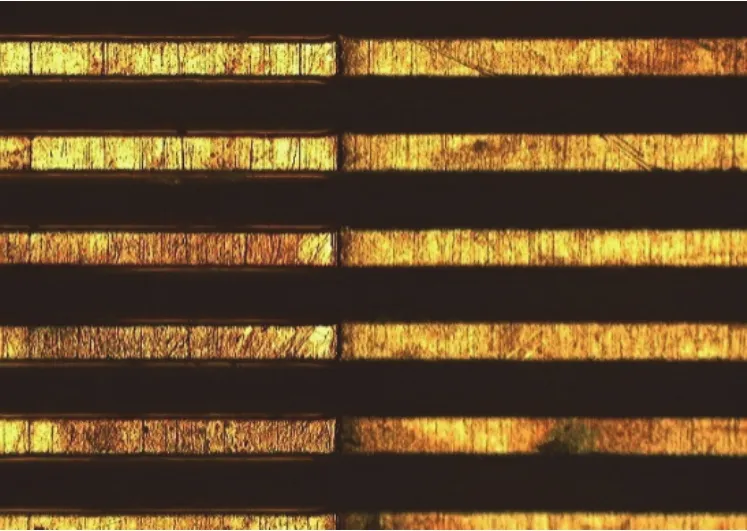

图8左侧为75 μm线宽阶梯板的15 μm铜厚区,右侧为45 μm铜厚区,两区域连接处没有出现断路现象。

由图9可以看出,不同区域的线路表面连接性好,没有出现断路,并且线路比较光滑,满足印制板的可接受性要求(IPC-A-600H–2010)。

图8 15 μm/45 μm阶梯板上75 μm阶梯线路的金相照片Figure 8 Metallographic image of the 75 μm-wide lines on a 15 μm/45 μm stair-stepped copper-clade laminate

图9 75 μm线宽15 μm/45 μm阶梯板上不同铜厚线路的电镜照片Figure 9 Scanning electron microscopic images of the 75 μm-wide lines on a 15 μm/45 μm stair-stepped copper-clad laminate

2.3.3 蚀刻因子

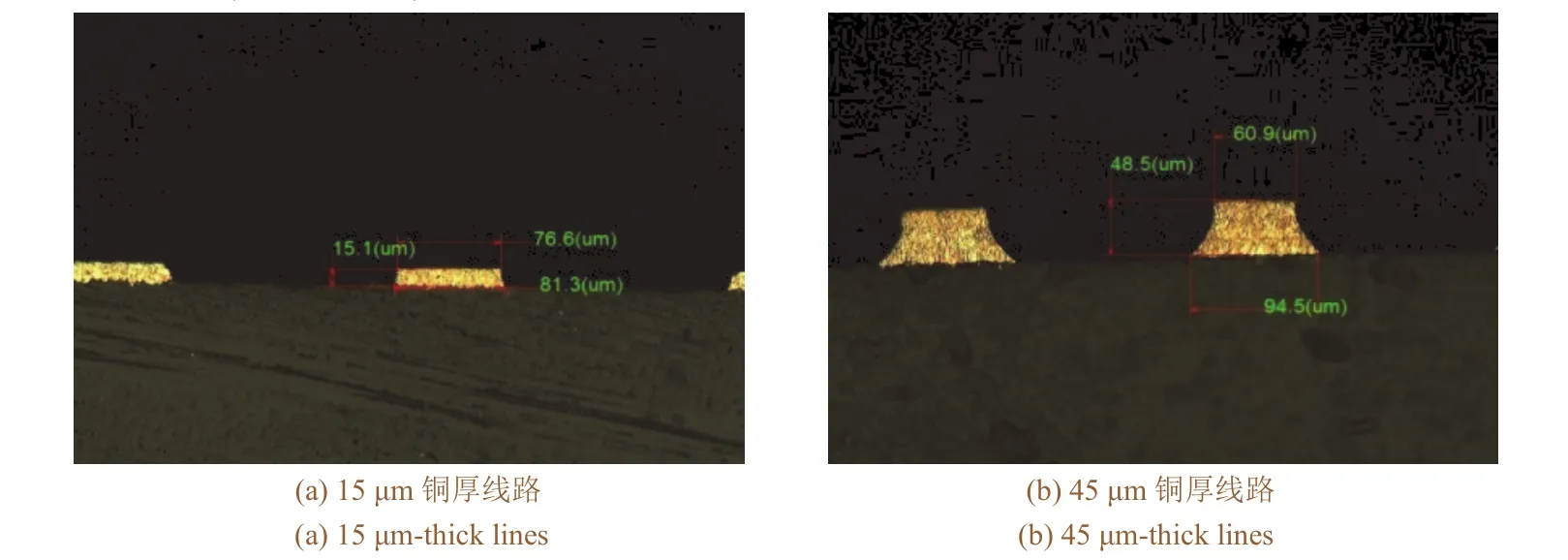

根据图10算得15 μm和45 μm铜厚区域的蚀刻因子分别为6.4和2.88,均在可接受的范围内。

图10 75 μm线宽15 μm/45 μm阶梯板上不同铜厚线路的金相截面照片Figure 10 Sectional metallographic images of the 75 μm-wide lines on a 15 μm/45 μm stair-stepped copper-clad laminate

3 结论

本文提出的在15 μm/45 μm阶梯线路板上制作75 μm宽阶梯线路的方法简单、可靠,可广泛应用于阶梯线路的制作。

[1]HUANG J X, YANG D T, GONG C L.Inspection of PCB line defects based on directionality measurements [J].Circuit World, 2012, 38 (3): 130-141.

[2]皆利士多层线路版(中山)有限公司.厚铜阶梯线路板及其制备方法: 201310288126.9 [P].2013–10–02.

[3]张霞, 陈晓宇, 曾平.影响电路板线路图形精度的因素研究[J].印制电路信息, 2013 (增刊1): 43-50.

[4]博敏电子股份有限公司, 重庆大学.一种阶梯线路板的制作方法: 201410089348.2 [P].2014–10–01.

[5]深圳崇达多层线路板有限公司.一种印刷线路板阶梯线路的制作工艺: 201210097643.3 [P].2012–08–29.

[6]ZHOU G Y, HE W, WANG S X, et al.A novel nitric acid etchant and its application in manufacturing fine lines for PCBs [J].IEEE Transactions on Electronics Packaging Manufacturing, 2010, 33 (1): 25-30.

[7]HE W, CUI H, MO Y Q, et al.Producing fine pitch substrate of COF by semiadditive process and pulse reverse plating of Cu [J].Transactions of the IMF,2009, 87 (1): 33-37.

Fabrication of 75 μm-wide conductive lines on a 15 μm/45 μm stair-stepped copper-clad laminate

LI Xiao-wei

A process for fabricating 15 μm/45 μm stair-stepped copper-clad laminates with 75 μm-wide fine lines was developed.A 15 μm/45 μm stair-stepped copper-clad laminate is initially prepared based on a double-sided copper-clad laminate with a copper thickness of 15 μm by copper electroplating, and then the 75 μm-wide conductive lines are produced via etching compensation.The stair-stepped conductive lines were evaluated by line width measurement, microscopic morphology observation and etching factor calculation.The results showed that the process can produce conductive lines with high accuracy, good quality and reduced costs.

stair-stepped copper-clad laminate; conductive line; etching compensation; copper thickness; etching factor

TN41

A

1004 – 227X (2017) 21 – 1137 – 05

10.19289/j.1004-227x.2017.21.005

Author’s address: Department of Laboratory Management, Xi’an Polytechnic University, Xi’an 710048, China

2017–04–11

2017–10–15

李晓蔚(1989–),女,甘肃白银人,硕士,助理工程师,研究方向为印制电路的制作。

作者联系方式:(E-mail) 729329778@qq.com。

[ 编辑:温靖邦 ]