一种FPGA芯片中DSP模块的内建自测试方法

孙洁朋,魏建民,闫 华,丛红艳

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

一种FPGA芯片中DSP模块的内建自测试方法

孙洁朋,魏建民,闫 华,丛红艳

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

提出了一种针对Xilinx Virtex-4/5系列FPGA芯片中嵌入式数字信号处理器(DSP)的内置自检测试(BIST)和故障诊断方法。该方法可以对DSP电路中乘法器和加法器进行有效的测试,缩短测试时间,减少工作量。同时通过更改DSP的配置信息来实现全芯片DSP的功能测试,提高了DSP模块的测试故障覆盖率。

内置自检测;乘法器测试;加法器测试;DSP;FPGA;Virtex-4

1 引言

目前为止已经开发了用于现场可编程门阵列(FPGA)中一些可配置逻辑块(CLB)、存储模块(BRAM)、时钟模块(CMT)等资源的测试及故障率诊断方法,但是,对于嵌入式数字信号处理器(DSP)内核的测试,除了基本的性能和功能测试,对于故障覆盖率方面的测试所做的工作还很少。Virtex-4和Virtex-5芯片中都嵌入了DSP内核、DSP主要乘法器、加法器和一些逻辑单元,用于执行复杂的数字信号处理运算。由于电路的复杂性,想要使故障覆盖率达到99%比较困难,尤其是乘数器和加法器的测试,因此我们的目标是开发一个Xilinx FPGA系列芯片中DSP内核的BIST方法,用于DSP的故障诊断。这也是本文重点研究的内容。

在本文中,我们以Virtex-4系列FPGA芯片为例,提出了一种用于DSP的BIST方法,提高DSP模块的测试故障覆盖率。

2 Virtex-4架构概述

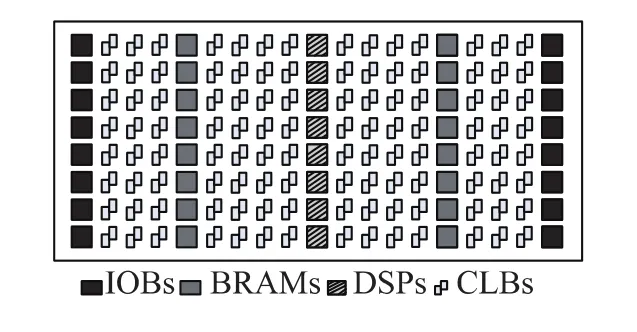

Virtex-4 FPGA的基本架构如图1所示。

由图1可知,芯片由可编程的CLB列、输入/输出块(IOB)、存储块BRAM和数字信号处理模块DSP构成[1]。不同Virtex-4 FPGA系列(LX、SX或FX)的CLB、IOB、BRAM和DSP的行数和列数不同。图1中的DSP是一个DSP title,包含两个DSP slice,其结构如图2所示。

图1 Virtex-4 FPGA的基本架构

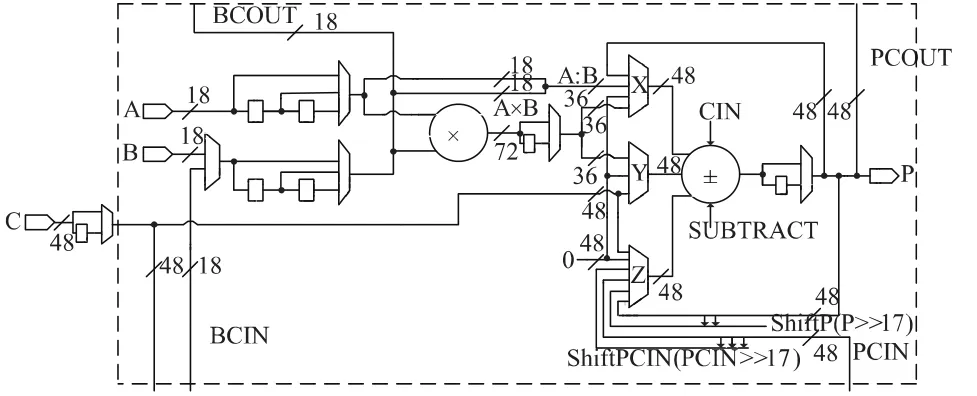

图2 DSP slice结构图

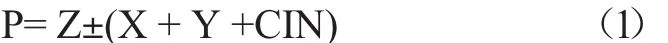

每个DSP Slice都有一个后接多路复用器的2输入乘法器和一个3输入加法器/减法器。对于加/减法单元,其可以实现不同的加/减逻辑组合。其公式为:

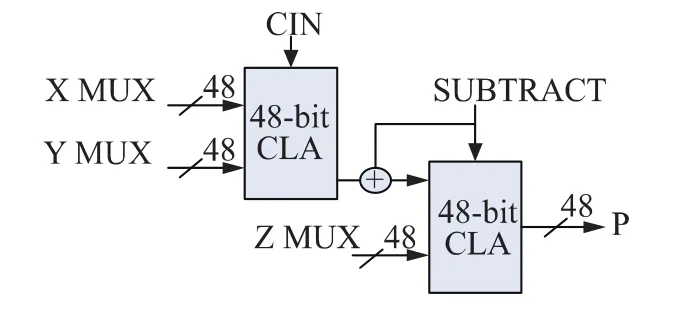

式(1)中P是输出端口,X、Y和Z是多路复用器。根据OPMODE的设置来决定X、Y、Z的选择结果。CIN项为进位输入,SUBTRACT控制加或减,将其设置为0则为加法,1为减法[2]。这个结构就是2级CLA加法器,如图3所示。

图3 2级CLA加法器结构图

3 DSP乘法器和加法器测试方案

DSP的乘法器实现原理,官方数据给的较少。查阅相关资料,同时基于面积和性能分析得出结论,即乘法器的实现是采用Booth编码乘法器。

在文献[3]中,作者提到Virtex-4中的DSP内核是由线性反馈移位寄存器(LFSR)生成,可以采用伪随机激励来测试,但没给出具体的测试算法或测试程序来测试DSP中的加法器和乘法器,也没有提到能检测到的故障率覆盖范围。

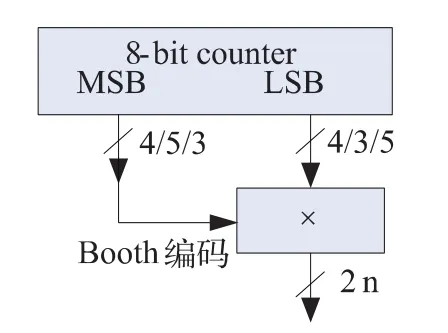

在文献[4]中,作者采用Booth/Wallace树的方法来测试乘法器,提高故障覆盖率。如图4所示,该方法使用8位二进制计数器,生成测试方案所需要的任何数据,可以适应任何位宽的乘法器并获取故障覆盖99%的范围[4]。

图4 乘法器结构图

一种方法是4×4算法,其中4个最高有效位(MSB)组成乘法器一输入端口,4个最低有效位(LSB)组成另一输入端口,用8位计数器的高低4位组成输入激励,然后重复运行。另一种方法为5×3算法,5个MSB位组成Booth编码乘法器的一个输入端口,3个LSB组成另一个端口。然而,我们不知道哪两个乘数输入端口与Booth编码相关联。因此,无法证明5×3算法是最好的测试方法。

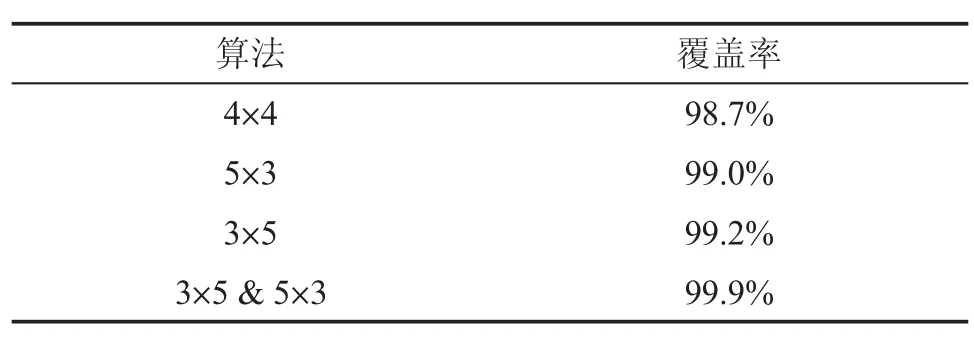

为了提高测试覆盖率,我们采用5×3和3×5两个测试算法相结合的方法来确保我们在两个测试序列之中将5个MSB应用到了Booth编码端口。这虽然会使测试时间加倍,但也只是增加了从256到512的测试向量的数量,测试时间不算太长。表1所示为不同算法的乘法器覆盖率,这些算法适用于任何位宽的乘法器。

表1 乘法器测试覆盖率

加法器的实现原理同样是基于资料和理论分析,确定采用超前进位加法器(CLA)来实现。

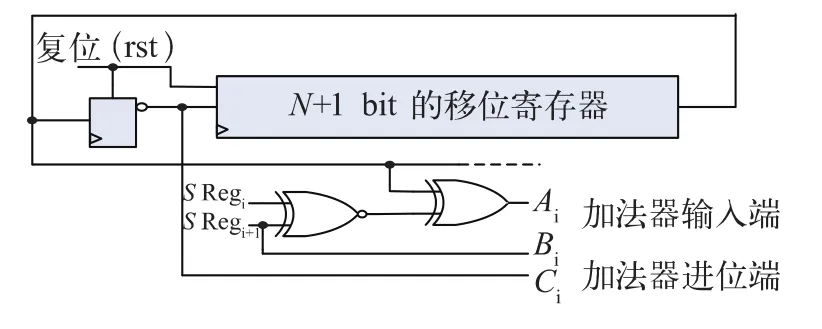

在文献[5]中,作者给出了超前进位加法器(CLA)的BIST方法,即通过测试模式发生器(TPG)产生2×(N+1)个测试向量序列来测试1个N位加法器。TPG由1个N+1位移位寄存器、N个异或门、N个XNOR门和逆变器组成。然而通过研究测试,该方案并不能保证故障覆盖率达到100%,还需要两个额外的测试项来检测缺失的测试向量。为了提高测试故障覆盖率,这里对TPG进行简单修改来产生这两个缺失的向量,如图5所示,通过用触发器代替环形计数器中的逆变器,并使用触发器的Q-bar输出提供给环形计数器。对TPG的这种微小修改产生了2×(N+2)个测试载体序列,使得加法器测试实现了100%的故障覆盖率。

图5 加法器测试架构

4 DSP的BIST

DSP的BIST方案是两个TPG将相同的测试模式和激励同时发送到DSP Title,每个TPG驱动DSP Title中相同位置的DSP slice,以方便进行级联模式的测试。这里将每个DSP Title中底部的DSP slice用s0表示,顶部用s1表示。每个DSP slice的输出结果都进行两次比较,如图6所示,从而形成两个圆形比较链,一条链比较DSP的s0部分,另一条比较DSP的s1部分。因此,每个DSP slice的输出都是由两个输出相应分析系统(ORA)来监测,并与不同title类型同一位置slice的两个ORA的输出进行比较。这解决了级联测试时使用循环比较的问题,减少了测试时间,同时使用多个TPG也克服了TPG测试向量缺失的问题。

图6 DSP BIST架构

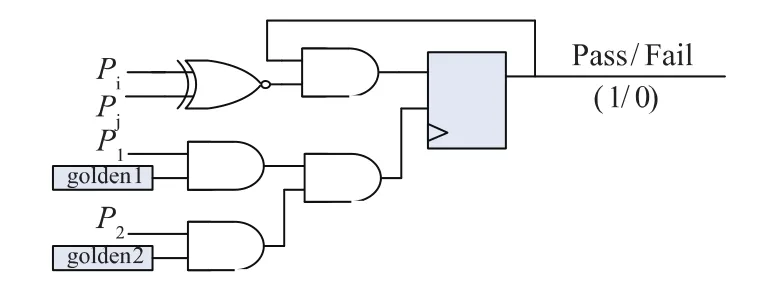

在BIST序列结束时,ORA的内容可以通过寄存器来进行回读。但是,我们关注的是ORA是否检测到故障及有故障时检测到的内容。因此,我们利用CLB中的逻辑资源,设计一个重复的判决器,在BIST结束时,提供1 bit的信息指示pass/fail,使得存储器回读流程简化,因为FPGA中的DSP模块是重复的单元,由于重复单元出现重复故障的概率较高,而这里的测试结构又是比较测试结果,为避免重复故障带来的测试问题,根据现有的测试条件,设计如下的测试结构,如图7所示,这样既可以减少无故障BIST序列的总测试时间,又可以避免重复故障带来的问题。

图7 ORA的实现框图

图7中,golden1和golden2为机台测试中预先设定的模型。判断时必须3条通路都正确才能输出高电平,否则就说明某个或多个DSP单元有故障。

DSP的BIST序列与DSP阵列大小无关,在进行DSP测试时,激励将达到所有的DSP输入端,通过反复更新配置重新进行测试,直到所有向量都被测试到。

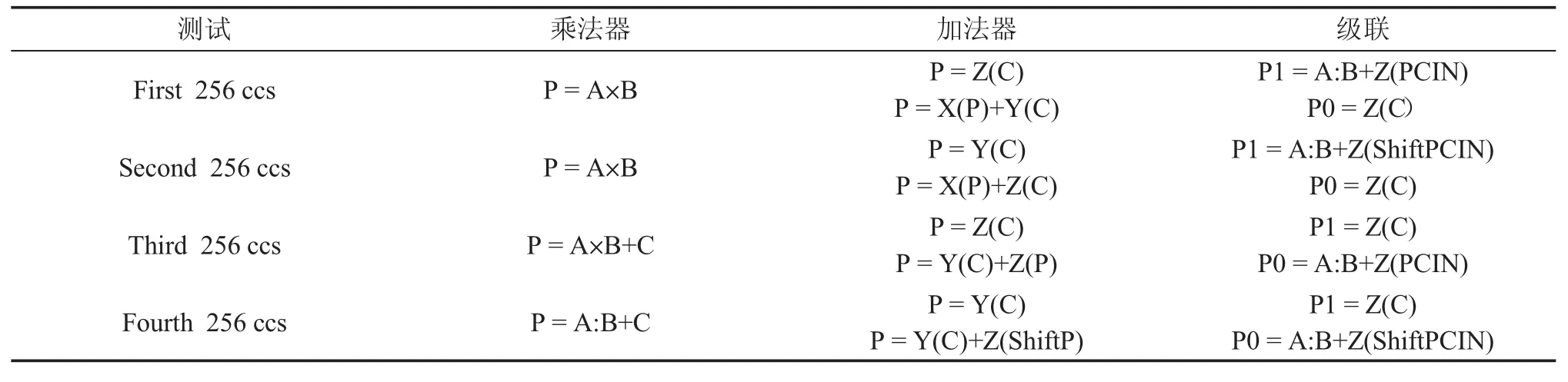

DSP的BIST序列主要有3种模式——乘法器、加法器和级联,如表2所示。

在代码设计时,每个BIST序列为1024个时钟周期,分为4组,每组256个时钟周期(表中的“ccs”)。测试模式根据设计要求输入到DSP slice中。

乘法器的BIST测试,通过设计计数器,采用5×3和3×5测试算法,将计数器的高5或高3位作为一个乘法器输入端口,低3或低5位作为另一端口,经过4组时钟周期的运算,完成乘法器BIST的测试。

表2 BIST测试序列

两级CLA加法器的BIST测试,同样是在4组时钟周期中交替更换配置模式,有所不同的是,在每组周期内,一半时间测试第一级加法器(见图3),另一半时间测试第二级加法器。由于C端口是加法器和累加器中唯一的48位外部输入端口,需要在两个时钟周期里加载每一个测试矢量到加法器中。在每组时钟周期里,在第一个时钟周期,97位测试矢量通过Y或Z多路复用器加载到累加器寄存器中,可以测试到该模式下的输出P(见公式1)。在第二时钟周期,通过C端口输入48位测试向量,通过Y或Z多路复用器,而P位中的48位向量寄存器反馈到X或Z多路复用器,CIN或SUBTRACT的值加载到加法器上,完成一次加法器测试。以此类推,完成所有加法器测试项。

每个DSP title中的两个DSP slice都可以与相邻的DSP级联(除了最底层和最顶层的DSP slice)。测试模式参考表2,其中P0表示s0,P1表示s1,方法和加法器类似,这里不再赘述。

5 仿真及测试结果

根据设计方案开发了DSP的BIST verilog测试代码,用CLB资源产生激励,生成移位寄存器、计数器和ORA,驱动DSP以完成DSP的各项测试。这里以Virtex-4的xc4vlx25为例,其他型号的芯片只需用脚本处理一下程序文件即可使用。代码完成后综合产生ncd文件。为检验程序设计的正确性,在上机台测试前先进行仿真,图8所示分别为加法器和乘法器仿真结果图。

图8 乘法器和加法器仿真结果

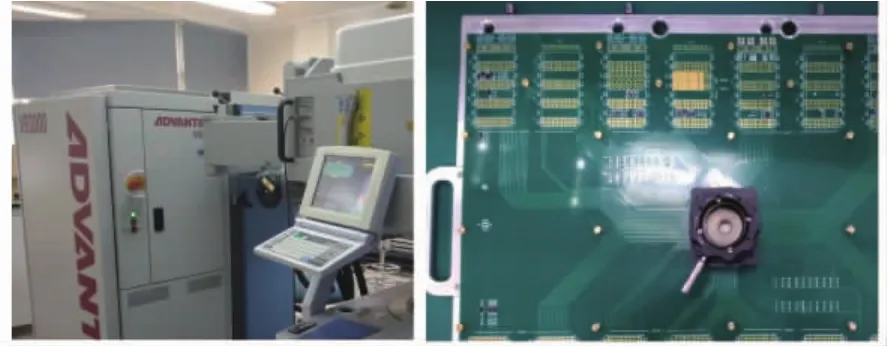

由图8可知,ORA结果为1,即pass。然后根据ncd文件生成RBT文件,转成适合机台的测试码进行测试。机台测试设备及测试板如图9所示。

图9 机台测试设备及测试板

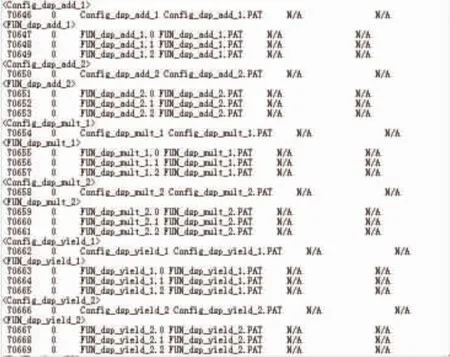

在机台上测试,导出的测试数据如图10所示。

由图10可知,测试结果通过(代码pass时会直接跑下一个代码,fail时会停顿,后面直接给出错误数据),由于V4和V5系列芯片的DSP架构大致相同,因此该BIST方法同样适用于Virtex-5芯片的DSP BIST。

图10 机台测试结果

6 总结

本文给出了DSP的一种BIST方案,通过阐述乘法器和加法器原理,给出DSP的相关测试方案,开发代码并在机台上测试通过,说明该方案的可行性及有效性,既提高了DSP模块的测试故障覆盖率,也为以后类似的乘法/加法器等复杂电路测试提供一种有效的测试方法。

[1]Virtex-4 User Guide.UG070(v1.5)[P].Xilinx,Inc,2006.

[2]Xtreme DSPfor Virtex-4 User Guide[P].UG073(v2.1),Xilinx,Inc,2005.

[3]A Sarvi,J Fan.Automated BIST-based diagnostic solution for SOPC[C].Proc Int Conf on Design&Test of Integrated Systems in Nanoscale Technology,2006:263-267.

[4]D Gizopoulos,A Paschalis,Y Zorian.Effective Built-In Self-Test for Booth Multipliers[J].IEEE Design&Test of Computers,1998(15):105-111.

[5]Mary D Pulukuri,Charles E Stroud.On Built-In Self-Test for Adders[J].Theory&Applications,2009(25):343-346.

A New Method of Built-In Self-Test of DSP in FPGAs

SUN Jiepeng,WEIJianmin,YAN Hua,CONG Hongyan

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

In the paper,a new method of Built-In Self-Test(BIST)for testing and diagnosing the embedded digital signal processors(DSPs)in Xilinx Virtex-4/5 series Field Programmable Gate Arrays(FPGAs)is presented.The method can effectively test the multiplier and adder in the DSP circuit,shorten the test time and reduce the workload.Meanwhile,the function test of the whole chip DSP can be realized by changing the configuration information of the DSP,and the test fault coverage of the DSP module is improved.

built-in self-test;multiplier test;adder test;digital signal processor;field programmable gate array;Virtex-4

TN407

A

1681-1070(2017)10-0009-04

2017-5-12

孙洁朋(1987—),男,河南巩义人,硕士,助理工程师,现从事FPGA芯片的验证和测试工作。