一种低电源电压的多通道UART设计

王雪萍,张国华,,顾展宏,卓 琳

(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司第五十八研究所,江苏无锡214072)

一种低电源电压的多通道UART设计

王雪萍1,张国华1,2,顾展宏2,卓 琳2

(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司第五十八研究所,江苏无锡214072)

为了满足复杂控制场合中多点通讯、低功耗、高速率以及低错误率等的要求,提出了一个低电源电压的多通道通用异步收发器(URAT,Universal Asynchronous Receiver and Transmitter)设计方案。每个通道独立控制,发送端和接收端配置的FIFO(First In First Out)在高速数据传输期间可临时存储数据以免数据丢失。采用自上而下的设计方法,使用Cadence工具进行合成与仿真。测试结果表明,该电路满足设计要求,仿真波形验证了数据收发的完整性。

低电源电压;UART;多通道;FIFO

1 引言

通用异步收发器(UART)是一种能同时支持短距离和长距离数据传输的串行通信接口,广泛应用于微机和外设之间的数据交换。串行通信能够减少信号失真度,UART在串行通信中起重要作用,主要处理串行和并行数据之间的转换,可以实现两个系统之间的数据高速传输[1]。

随着计算机网络的发展以及总线协议等技术的广泛应用,一个串口资源已经无法满足通信需求,在集中控制场合中进行多点通讯可以有效解决此类问题。Wu等人[2]完成了基于异步技术的低功耗UART设计,文献[4]中使用异步FIFO实现了多通道UART控制器,允许以不同的波特需求与多个块进行通信。基于现有的技术思想,给出了一个可扩展的多通道UART设计方案,在发送器和接收器中同时配置发送和接收FIFO,FIFO能够临时储存数据,减少数据丢失。本文进行了双通道UART的设计,该电路在1.6~3.6 V的低电源电压范围内工作,有效降低了功耗,仿真及测试结果表明该电路满足设计要求。

2 主要工作模式

该双通道UART能够完成外部设备与处理器之间的数据发送和接收,在1.6~3.6 V的低压电源电压下工作数据速率可达4~8 Mbps,最高工作频率为64 MHz,工作电流为2.5 mA,主要工作模式有FIFO模式和DMA模式。

2.1 FIFO模式

FIFO(先入先出)用于在高速数据传输期间临时存储数据,FIFO作为不同设备之间的桥梁,是系统中最重要的部分[2]。一个时钟域时,数据值被写入FIFO缓冲器;另一个时钟域时,数据值从同一FIFO缓冲器中读取,其中两个时钟域彼此异步。异步FIFO通常用于快速和安全地将数据从一个异步时钟域传递到另一个异步时钟域。FIFO为队列结构,有一个固定的长度。如果FIFO为空或未完全填充,则只能将数据写入其中;如果FIFO已满,则在相应端向发送器和接收器发送信号“full”;如果FIFO是空的,则它发送信号“empty”到相应端的发射器和接收器。FIFO用于发送器和CPU之间以及接收器和CPU之间,防止在CPU与发送器和接收器之间传输不匹配时发生数据丢失。

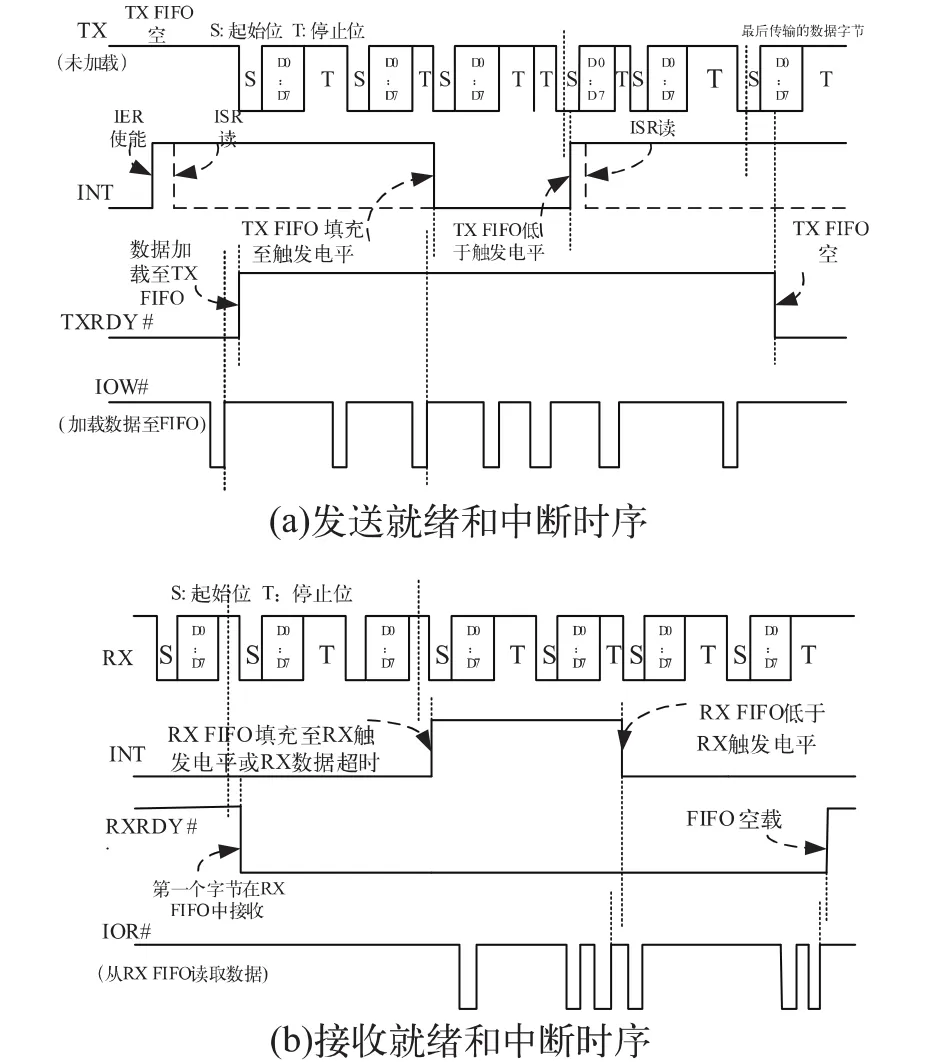

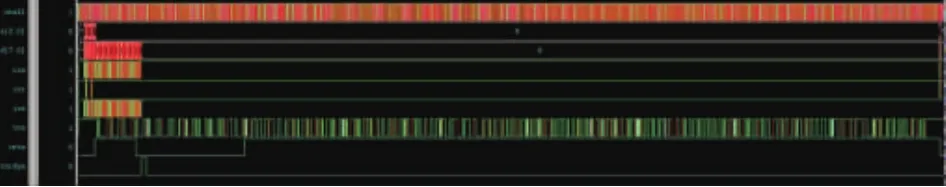

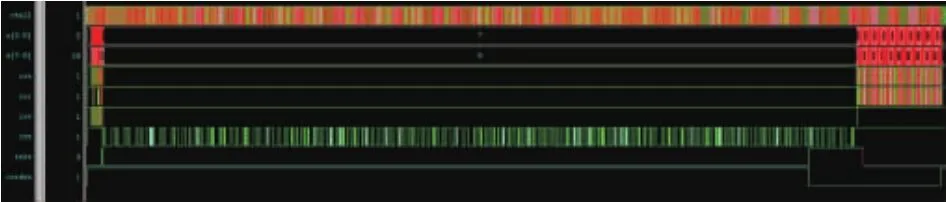

在FIFO模式下,主机填充64 B的发送数据,无论发送/接收FIFO何时空载,发送/接收保持寄存器空载标志都被设置。当FIFO内数据量低于设定的触发点时,发送保持寄存器空载标志可以产生发送空载中断信号,通过中断使能寄存器位1发送空载中断信号激活。当接收FIFO空载时,接收保持寄存器空载标志同样会产生一个接收空载中断信号。通道A、B在FIFO模式下的发送/接收就绪及中断时序如图1(a)、(b)所示。

2.2 DMA模式

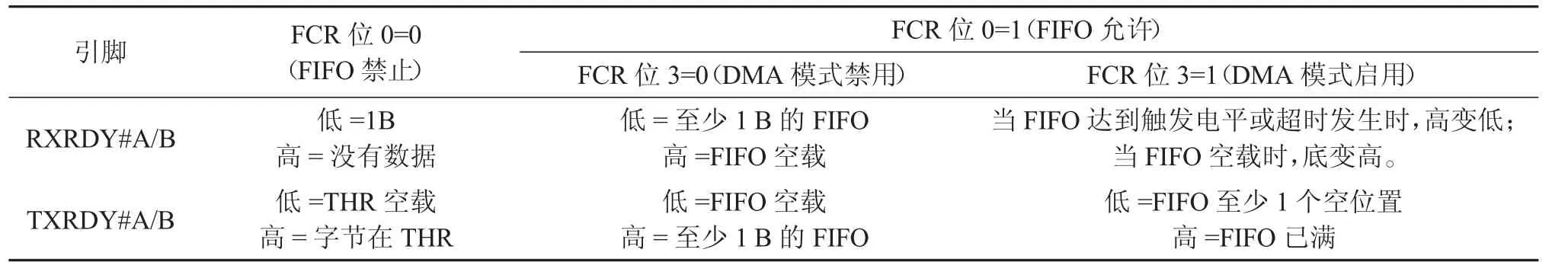

DMA模式指数据块传输操作,该模式会影响RXRDY#A/B和TXRDY#A/B输出引脚的状态。DMA模式操作下,发送和接收FIFO触发电平可以为用户提供额外的灵活性。当发送器为“空”或者具有用于更多数据的空位置时,线路状态寄存器位5-6(LSR)提供指示。用户可以通过控制FCR位3的状态来选择DMA模式进行操作。当使能发送和接收FIFO并且禁止DMA模式(FCR位3=0)时,该电路将置于单字符模式,此时用户可以进行单字符发送或接收操作。当使能DMA模式(FCR位3=1)时,用户可以通过由可编程触发电平决定的块序列加载或者卸载FIFO进行块模式操作。在此模式下,该电路在发送FIFO变为“满”状态时设置TXRDY#引脚,在接收FIFO变为“空”状态时设置RXRDY#引脚。表1给出了在FIFO和DMA共同操作模式下,TXRDY#和RXRDY#引脚的输出状态。

图1 F I F O模式通道A、B发送/接收就绪和中断时序

3 电路设计

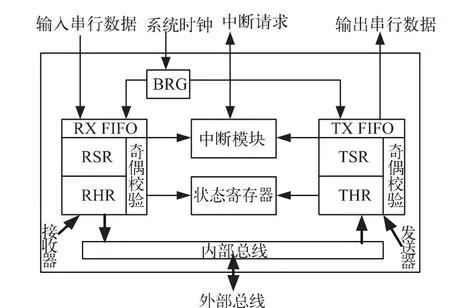

该电路有两个独立的通道A和B,两个通道在电路结构上完全一样,通道A内部结构如图2所示,由于篇幅有限,通道B内部结构图未给出,其主要由三个模块组成:发送器、接收器和波特率发生器(BRG)。发送器由TSR和THR组成,THR从本地CPU加载发送的数据,TSR接收来自THR的数据,并将其逐一发送到TXD引脚。接收器由RSR和RHR组成,RSR从RXD逐一接收数据。波特率发生器为发送器、接收器和FIFO提供时钟,发射端和接收端都配置了FIFO,用于暂时存储高速输入数据,防止数据丢失[3]。每个通道能够独立完成外部设备与处理器之间的数据接收和发送,实现串/并转换。使用的寄存器有RSR(接收移位寄存器)、RHR(接收保持寄存器)、THR(发送保持寄存器)、TSR(发送移位寄存器)、DLL(除数LSB锁存器)、DLM(除数MSB锁存器)、LSR(线路状态寄存器)、FCR(FIFO控制寄存器)。

表1 TXRDY#和RXRDY#输出FIFO与DMA模式

图2 通道A内部结构图

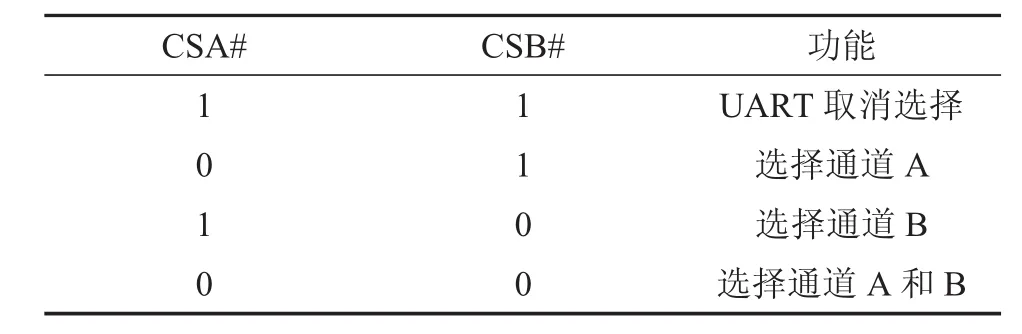

设计的双通道UART可以为用户提供在外部CPU和外部串行通信设备之间双向传送信息的功能。当片选引脚CSA#或CSB#处于低电平信号时,允许用户从电路上选择通道A或通道B进行配置,发送传输数据或卸载接收数据。在上电初始化时,写入相同的内部寄存器期间选择这两个UART是有效的。表2给出了通道A和B的选择情况。

表2 通道A、B选择

3.1 波特率发生器

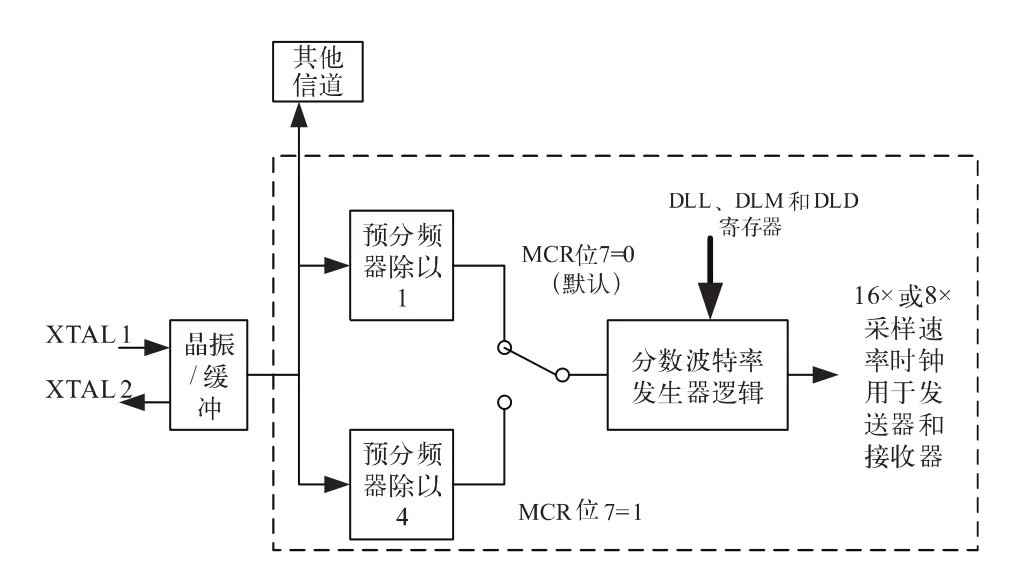

波特率发生器(BRG)为FIFO提供读时钟和写时钟,为发送器和接收器提供公共时钟信号。BRG为指定的波特率创建一个16×或8×的波特率时钟,提供给发送器和接收器模块以产生需要的波特率时钟脉冲。TXRDY#表示发送器发送就绪,RXRDY#表示接收器接收就绪。该电路可以在引脚XTAL1和XTAL2上使用外部24 MHz晶振工作,或者在XTAL1引脚上使用高达64 MHz的外部时钟源工作。BRG内部结构如图3所示,每个通道都配有内置预分频器的BRG,通过调制解调器控制寄存器中的软件流来控制预分配器。调制解调器控制寄存器(EMSR位7为1或0)设置1或4来划分输入的晶振或外部时钟,使得BRG能够提供16×或者8×的采样时钟速率,采样时钟速率不同,可以实现不同数据速率传输。预分频器的时钟输出记录到BRG上,BRG在1到(216-0.0625[216-1+15/16])之间以每隔0.0625(1/16)为单位的增量将这个时钟通过一个可编程的除数进一步划分,获得串行数据速率中16×或8×采样时钟速率。采样时钟用于数据比特移位发送器和数据采样接收器。

图3 波特率发生器

当复位时,该BRG除数(DLL、DLM和DLD寄存器) 默 认 值 为 “1”(DLL=0x01,DLM=0x00 和DLD=0x00),因此,在初始化操作数据速率时对BRG进行编程。该DLL和DLM寄存器提供除数的整数部分,DLD寄存器提供除数的小数部分。只有DLD的低四位生效时,才用它们来选择从0值(设置0000)至0.9375(设置1111)的值。编程波特率发生器,寄存器DLL、DLM和DLD提供了选择操作数据速率的能力。

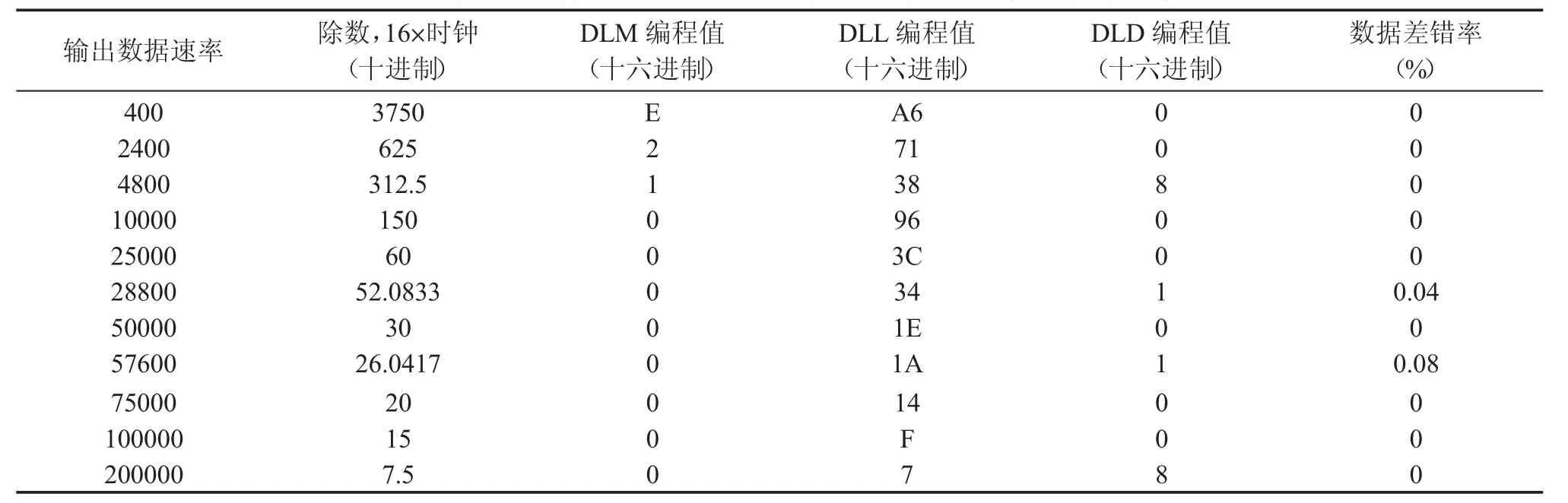

表3给出了采用24 MHz晶振或16×采样时钟速率的外部时钟下的标准数据速率。如果使用预分频器,输出数据速率与表3中所示相比少4倍,在8×采样速率下,这些数据传输速率将增加一倍,此外,当使用8×采样模式时,每当DLD非零时且为奇数,比特时间将有抖动(±1/16)。

当使用非标准数据速率晶振或外部时钟时,除数值可以使用以下公式计算:

16×,EMSR[7]=1;

8×,EMSR[7]=0;

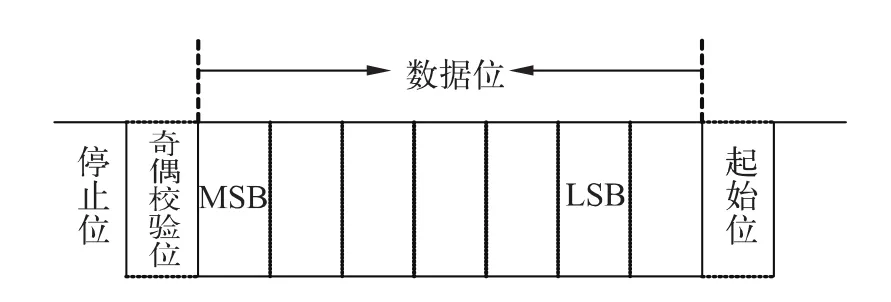

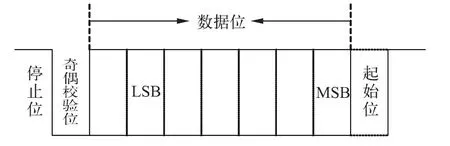

3.2 发送器

发送器部分包括一个8位TSR和1 B宽的THR的64 B FIFO。在16×的内部时钟下,发送状态寄存器移出每个数据位,一个数据位时间为16时钟周期。发送器根据数据位数发送起始位,再发送数据位,激活后插入正确的校验位再加上停止位。TX FIFO和发送状态寄存器的状态记录在LSR上。THR是一个提供数据接口到主机处理器的8位寄存器。主机将发送数据字节写入THR,转换为包括起始位、数据位、奇偶校验位和停止位的串行数据流,最低有效位(LSB)作为第一个数据位发送。当FIFO操作被功能控制寄存器位0激活时,THR成为64 B发送FIFO的输入寄存器。每次THR进行一次写操作,FIFO数据指针自动落到下一个时序的数据位置。图4显示了数据发送过程。起始位指示数据传输开始,校验位用于错误检测,停止位用于指示发送到接收器结束。起始位始终为低,停止位始终为高,数据位的LSB优先发送。

表3 在16×采样时具有24 MHz晶振或外部时钟的典型数据速率

图4 数据发送过程

3.3 接收器

接收器部分包含一个8位RSR和1 B宽RHR的64 B FIFO。RSR使用16×时钟计时,证实并且验证了每个数据位中间的每一位传入字符。在起始位或错误起始位的下降沿,内部接收计数器在16×时钟速率下开始计数,经过8(16×)时钟之后,该起始位时段应该在起始位中间。对此时的起始位进行采样,用这种方法估测起始位可以防止接收器接收到一个错误的字符。对其余数据位和停止位进行采样,用同样的方法验证以防止错误数据结构。如果有任何错误,都会记录在线状态寄存器的位2~4上。从RHR上卸载接收数据字节,接收FIFO指针跳转的同时错误标志会立即刷新,以反映RHR中数据字节的状态。RHR可以在收到字符或延迟信号时产生一个接收数据就绪中断信号,直到达到FIFO触发电平。此外,接收数据延迟中断信号可以确保数据正确传输到主机。该数据是由总线控制寄存器[1:0]定义的4个字长加12个位时间定义的,相当于3.7~4.6字符时间。通过中断使能寄存器位0激活RHR中断。图5显示了数据接收过程。

图5 数据接收过程

RHR是一个8位寄存器,用于存放从RSR接收的数据,提供了到主机的接收数据端口。RHR是64 B 11位宽接收FIFO的一部分,为3个错误标志提供3个额外的位,在线状态寄存器中进行记录。当FIFO被功能控制寄存器位0激活时,RHR包含由FIFO接收到的第一个数据字符。当RHR中数据被读取时,下一个字符就加载到RHR中,与当前数据字节相关联的错误标志,在LSR位2~4中被立即更新。

4 仿真与验证

CPU接口通过8位数据位宽度与3位地址线及控制信号来执行数据总线读和写处理。通过片选和写信号配合,可以通过数据总线对内部寄存器进行写操作,从而完成内部寄存器的配置。通过片选和读信号进行配合,可以通过数据总线对内部寄存器进行读操作,从而可以得出内部寄存器的工作状态。

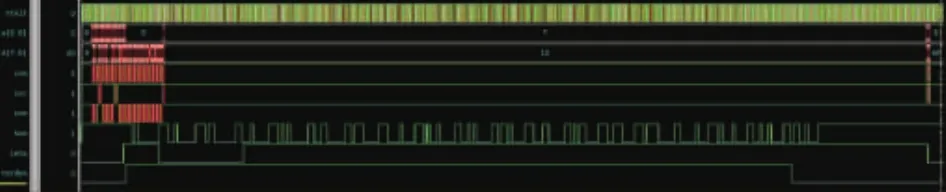

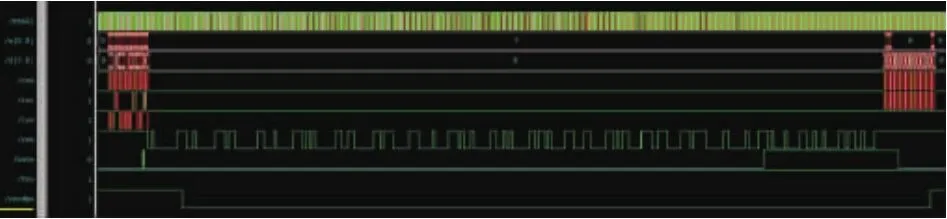

仿真环境设置为2.25 V电源电压,工艺角SS,温度125℃,对FIFO模式和DMA模式分别进行仿真。FIFO模式下发送如图6所示,设置发送FIFO触发点为16,开始往发送保持寄存器中写数据,当发送FIFO中数据大于16时中断拉低;当发送数据到发送FIFO中数据低于16时,中断拉高,仿真结果满足设计要求。FIFO模式下接收如图7所示,设置接收FIFO触发点为16,当接收到第16个数据后中断拉高;当总线从接收保持寄存器中读出数据,接收FIFO中的数据低于16个数据时,中断拉低,从仿真结果可知满足设计要求。

图6 FIFO模式下发送数据仿真波形图

图7 FIFO模式下接收数据仿真波形图

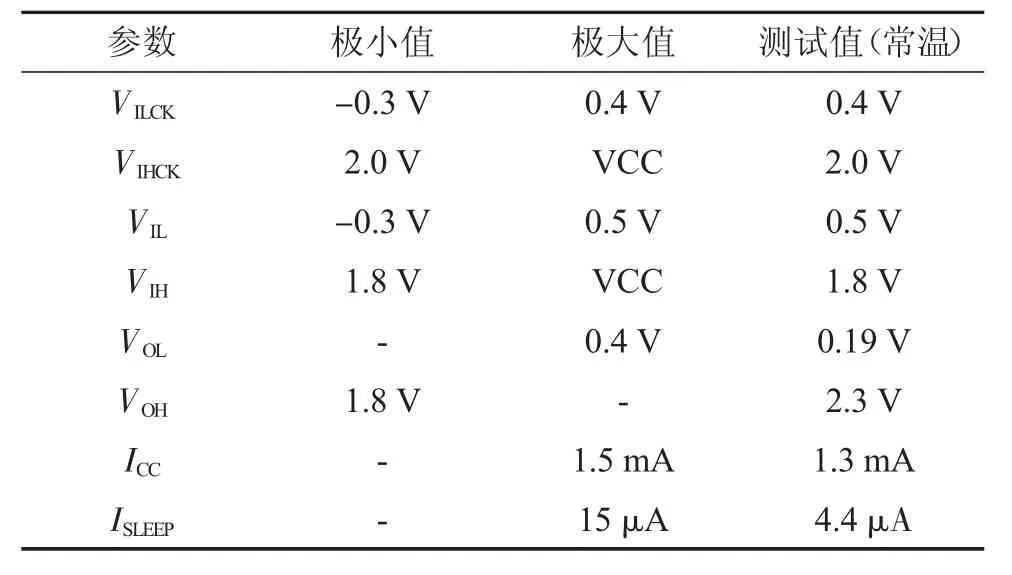

表4 直流参数测试值

图8 DMA模式发送仿真波形图

图9 DMA模式接收仿真波形图

DMA模式发送如图8所示,将电路DMA使能打开,当发送FIFO数据达到设置的触发点后,中断拉高,当FIFO数据满TXRDY拉高;当发送一个数据后,TXRDY拉低,当发送数据到发送FIFO低于设置的触发点后,中断拉高,仿真结果满足设计要求。DMA模式接收如图9所示,将电路DMA使能打开,当接收FIFO数据达到设置的触发点后,中断拉高,RXRDY拉低;当FIFO中数据低于触发点中断拉低,当FIFO为空,RXRDY拉高,仿真结果满足设计要求。

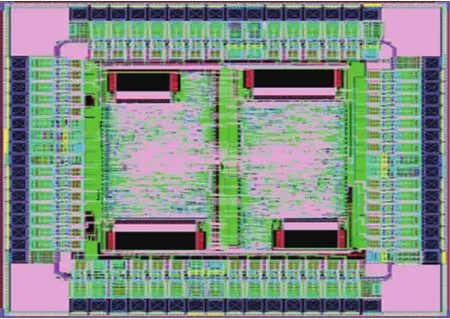

图10所示为整体版图布局,对模块进行功能划分,使用EDA工具进行版图方向设计,采用自动布局布线方法以及在Cadence中模拟和合成来完成整体版图设计,在2.25 V电压及常温条件下测得的直流参数如表4所示。

图10 整体版图布局

5 结束语

本文对波特率发生器、接收器和发送器分别进行设计,该电路在1.6~3.6 V低电源电压下能够实现数据完整收发,3.3 V供电电压和8×采样时钟速率时电路数据传输速度可达8 Mbps。通过完善的逻辑仿真与版图验证,使得功能与参数可以完全兼容,目前已流片验证并应用到产品中。

[1]L K Hu,Q CH Wang.UART-based Reliable Communication and performance Analysis[J].Computer Engineering,2006,32(10):15-21.

[2]X D Wu,B Dai.Design of Interface Between High Speed A/D and DSP Based on FIFO[J].Journal of Beijing Institute of Petro-chemical Technology,2006,14(12):26-29.

[3]R K Agrawal,V R Mishra.The Design of High Speed UART[C].IEEE Conference on Information and Communication Technologies,2013(06):388-390.

[4]U Nanda.Universal Asynchronous Receiver and Transmitter[C].2016 3rdInternational Conference on Advanced Computing and Communication Systems,2016(08):22-23.

Design of a Low Supply Voltage Multi-Channel UART

WANG Xueping1,ZHANG Guohua1,2,GU Zhanhong2,ZHUO Lin2

(1.Schoolof Internetof Things Engineering,Jiangnan University,Wuxi 214122,China;2.China Electronics Technology Corporation No.58 Research Institute,Wuxi 214072,China)

A design scheme for low power supply voltage multi-channel UART is proposed to meet the need of multi-point communication,low power consumption,high speed and low error rate in the complex control occasions.Each channel is independently controlled,and the FIFO configured at the transmitter and receiver can temporarily store data during high-speed data transmission to avoid data loss.The circuit utilizes top-down design method and uses Cadence tool for synthesis and simulation.The test results show that the circuit meets the design requirements,and the simulation waveforms verify the integrity of data transceiver.

low supply voltage;UART;multi-channel;FIFO

TN402

A

1681-1070(2017)10-0021-05

2017-6-13

王雪萍(1991—),女,河南信阳人,硕士研究生,主要研究方向为集成电路设计。