一种用于ESD保护的SCR触发电路

邵 红,张 森,齐 钊,乔 明

(1.无锡华润上华科技有限公司,江苏无锡 214028;2.电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

一种用于ESD保护的SCR触发电路

邵 红1,张 森1,齐 钊2,乔 明2

(1.无锡华润上华科技有限公司,江苏无锡 214028;2.电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

介绍一种检测ESD电压并输出触发或关断信号的电路结构。通过对ESD脉冲的上升沿进行分辨,然后输出触发信号从而触发SCR钳位器件对内部电路进行保护,并在ESD脉冲结束时对脉冲下降沿进行检测,从而输出关断信号关断SCR钳位器件,防止闩锁效应的发生。仿真结果显示,该电路能较好地检测ESD脉冲的上升沿或下降沿而输出不同的信号,从而能降低SCR钳位器件的触发电压,并防止闩锁效应。

ESD防护;触发电路;触发电压;闩锁效应

1 引言

静电泄放ESD(Electrostatic Discharge)是自然界中一种普遍的现象。虽然静电存在于生活的每个角落,但静电泄放对集成电路来说却是致命的威胁。据统计,大概有四成以上的集成电路失效是由ESD失效引起的[1]。随着集成电路工艺的提高,芯片尺寸越来越小,在带来性能提高的同时其抗ESD能力也越来越弱。由此可见,ESD的防护随着工艺技术的进步而变得越来越重要。

在一些先进工艺中,由于芯片内部极易被ESD所损伤,若像传统GGNMOS器件一样依靠结的击穿来触发[2],将很难实现有效的ESD保护。因此ESD器件的触发已经不能单纯依靠PN结的击穿来实现,必须设计辅助触发电路或结构来实现低电压触发。根据研究,可控硅(SCR)器件是一种电流能力很强的ESD保护器件,它能够以最小的面积占用提供最强的ESD电流能力。然而其较低的维持电压使得闩锁效应(latch-up)在ESD的诱导下很难避免[3]。目前对SCR结构在ESD脉冲下的特性研究已成为热点。如何实现超低压触发也是摆在ESD设计者面前的一道难题。

2 典型的ESD触发电路

在实际应用中,该触发电路的设计必须兼顾到如下两个设计难点:其一,在超低压芯片中实现SCR器件的高ESD性能、低寄生效应以及更小的芯片占用面积[7];其二,在高压电源钳位应用中,不会由于其强snapback发生闩锁效应。该触发电路的设计必须兼顾这两个设计难点。此外,抑制闩锁效应的方式通常是进行器件本身的优化,最常用且最可靠的方式是提高器件的维持电压Vh,使其大于被保护芯片的电源电压。但是,在高压应用中,过高的Vh会导致ESD器件在一个很高的电压基准上进行ESD电流的释放,这将导致器件的功耗增加。过高的功耗无疑会直接影响器件的ESD等级,这在设计中是不希望被看到的。因此,若一种电路能够在正确的时间做出正确的触发,即在ESD脉冲的下降沿及时关断器件,那么就可以不通过提高Vh来实现抑制器件的闩锁效应,这样的低Vh器件也具备更强的ESD能力。

3 新型SCR触发电路

对于SCR结构而言,通过提高维持电压来降低闩锁风险已成为当下一个有效的方案[8]。但是维持电压的大小与It2存在矛盾。即SCR结构抗闩锁能力越强,则其ESD能力越弱,人们往往会在两者之间取一个折中。

对此,本文提出一种新型的SCR触发电路,该电路的目的并不是单纯地降低SCR的触发电压,而是在降低SCR触发电压的基础上,辅助SCR的关断,使得闩锁效应不会发生。即:即使SCR的维持电压小于电源VDD,在ESD脉冲结束后SCR虽然不能够自行关断,但是该电路能够辅助其关断从而避免latch-up的发生。

图2 传统的ESD瞬态检测触发电路

3.1 新型SCR触发电路的结构

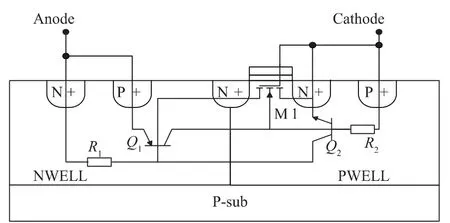

新型电路的主要设计思路为:TLP测试电压通常为一种方波信号,对方波信号而言,微电器电路(CR网络)能够很好地在信号上升沿与下降沿的时刻产生与上升/下降率成正比的正负脉冲。基于该思路,新型的SCR触发电路结构如图3所示,该电路由电容C与电阻R构成检测网络(微分电路),由二极管D1提供单向的触发电流通路。此外,二极管D2、D3为SCR的关断信号提供单向通路,并且两个二极管的串联存在约1.5 V左右的死区电压。该电压使得ESD电流只能通过SCR的寄生NPN管泄放而不会通过触发电路内部电阻R流入GND,保证了ESD电流的路径(即SCR与触发电路实现很好的电隔离)。可以看出,新型电路结构的输出端与SCR的门极相连,SCR门极即可作为触发端,也可作为抽取端,为设计提供了较大便利。

图1 低电压触发可控硅整流器(LVTSCR)剖面图

3.2 新型SCR触发电路工作原理

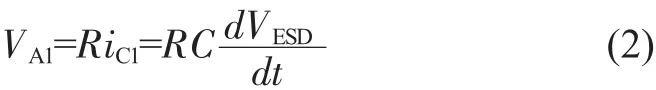

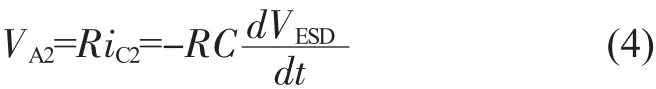

假设SCR器件为普通的低维持电压器件,当ESD来临时,该电路电容C上的瞬态充电电流iC1大小可表示为:

此时在A点上感应出的电压为:

19 构建 PPP(Public Private Partnership)模式血液净化培训中心的实践与探索 王九生,胡方圆,曹 鹏,张晓萍,魏 丽,梅长林

由于该电流iC1是一个瞬态电流,因此VA同样为一个瞬态电压,该电压将会通过二极管D1后加在SCR的门极G,当产生的门极电流iG1流过SCR中的寄生电阻Rpw所产生的压降达到寄生NPN管的发射结开启电压(约0.7 V)时,寄生NPN开启。NPN管开启后,寄生PNP管随之开启,此时SCR器件的正反馈被触发以泄放ESD电流。该过程即为SCR的触发过程,无论SCR的触发电压Vt1有多高,在该电路的辅助下,器件都会在很低的电压下开启。

当ESD脉冲结束(假设ESD下降时间与上升时间相同,且ESD电压在达到峰值后保持不变),其下降沿会在电容C上产生一个瞬态放电电流iC2:

从式(3)可以看出该电流的方向是由A点流入VDD的。因此,该电流在A点所产生的压降VA2则为负压。

由于负压的产生,使得SCR门极电流iG2为负。因此,在ESD结束时,该电流产生的负压将对SCR的门极电流进行抽取,该过程即为SCR结构的关断过程。电容放电电流可将SCR的门极电流抽取,从而关断SCR器件。

由于SCR发生正反馈时的条件为寄生的BJT管共基极放大系数α(pnp)+α(npn)>1,门极电流iG可以引起阳极电流IA的变化,从而引起共基极放大系数的变化。根据研究,SCR关断时需要抽取的最大门极电流IGM应满足:

其中IATO为被关断的最大阳极电流。

由此可见,要想关断SCR,反向抽取电流|IGM|应满足式(5)。反向放电电流iC2在当二极管D2、D3开启以前为电阻R上流过的电流iR,当二极管D2、D3导通后,iC2中大部分由反向抽取电流IGM提供。因此,|VA|的最小值为当:

时所对应的A点电压,即:

4 仿真结果与讨论

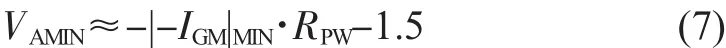

电路采用某平台下0.35μm BCD工艺,并通过Spectre仿真验证。图4为本文所提出的新型SCR触发电路在正常信号上升沿通过时的仿真波形。新型电路的电阻R取值为5 kΩ,电容C取值为5 pF。二极管D1、D2、D3的宽长比均取为5μm/2μm。正常信号由0 V经1 ms的上升时间达到5 V上电并保持。从输出波形可以看出,该电路在电源上电情况下输出0电位,ESD钳位器件不会开启,因此符合ESD设计的最基本要求,即ESD网络不能够影响电路的正常上电或工作。

图4 新型SCR触发电路在正常信号下的仿真结果

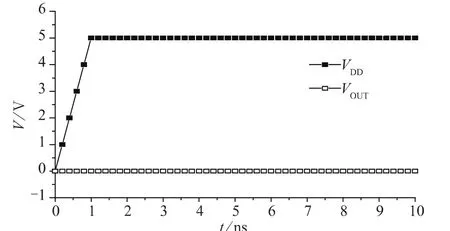

图5为传统ESD触发电路的仿真波形。传统电路的电阻R1取值为10 kΩ,电容C1的取值为10 pF。模拟的ESD信号加在VDD上并以10 ns的上升速度由0 V上升至10 V,保持200 ns后同样以10 ns的下降速度下降至0 V。从输出点的信号波形可以看到,在200 ns的ESD保持时间内,输出信号高电平的维持时间在50 ns左右,电压峰值达10 V左右。由于正常情况下钳位器件的栅极一直输出低电平使该电路处于关闭状态,一旦有快速上升的电压脉冲产生时,就会输出一个瞬态高电压来触发后级钳位器件从而钳位电压。

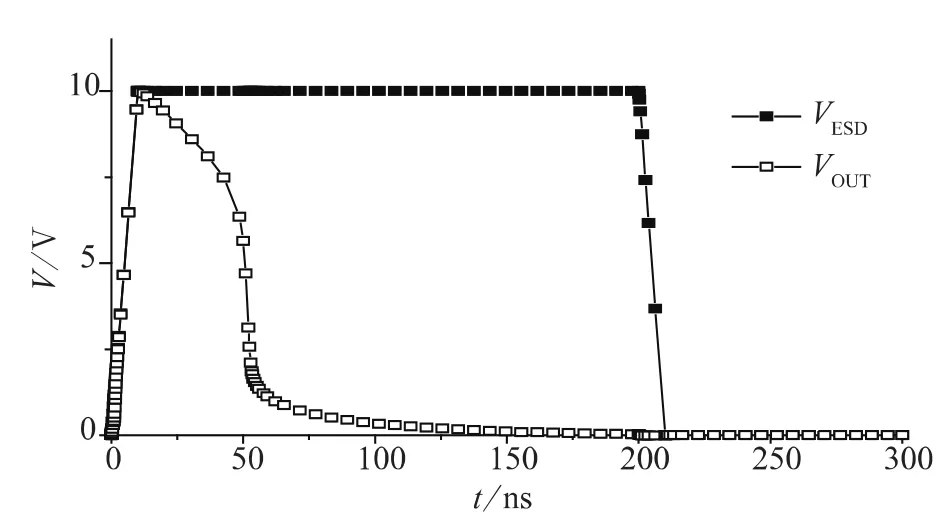

图6为本文所提出的新型SCR触发电路在ESD脉冲通过时的仿真波形。模拟的ESD信号同样加在VDD上并以10 ns的上升速度由0 V上升至10 V,保持200 ns后同样以10 ns的下降速度下降至0 V。从输出波形可以看出,在ESD电压上升的时候,该电流输出为一个瞬态的高电位以触发SCR结构,而在ESD电压下降时,该电流的输出为一个负向的瞬态峰值电位以辅助SCR结构的关断,防止闩锁效应。

图5 传统触发电路仿真图

图6 新型SCR触发电路的仿真波形

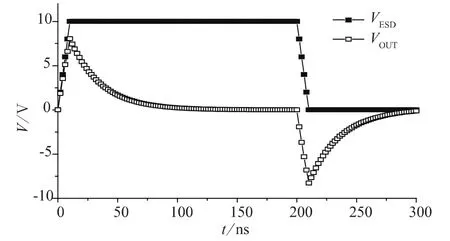

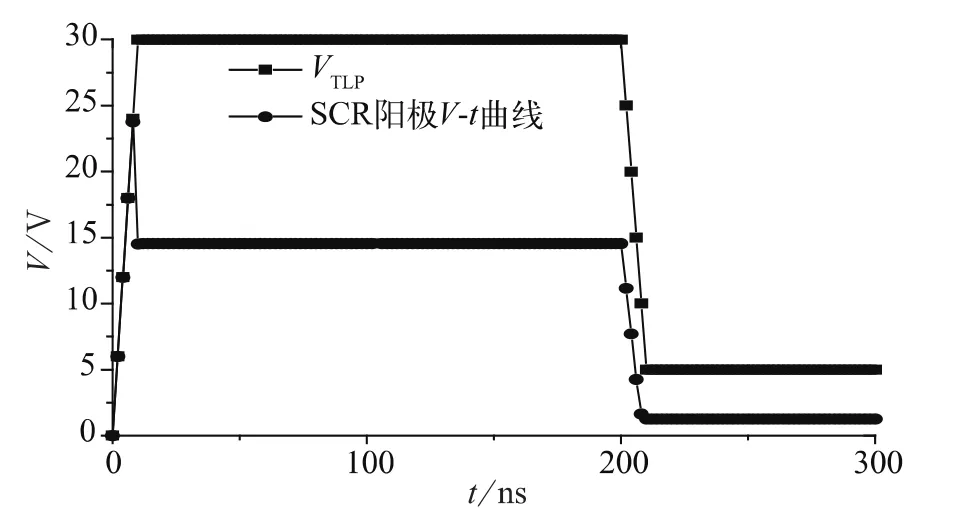

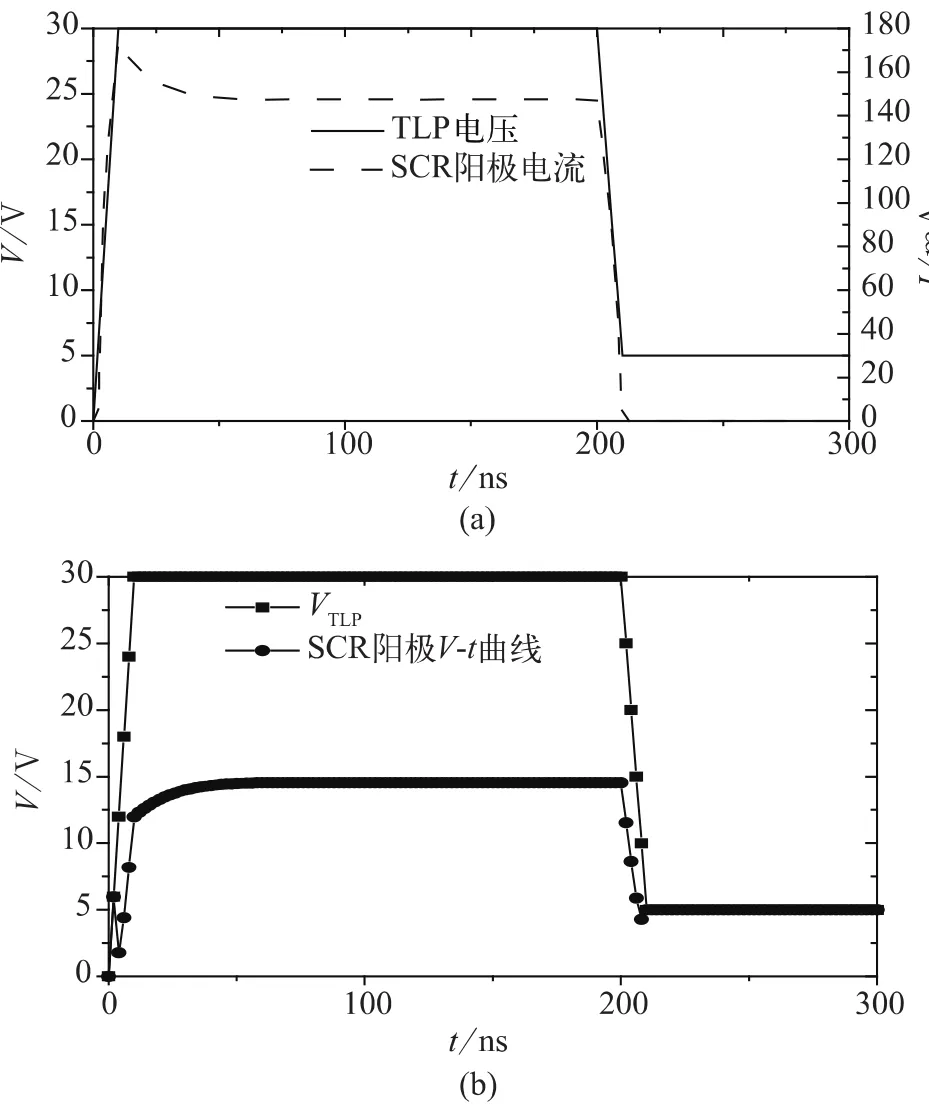

为了进一步说明该电路对抗闩锁效应问题的作用,我们采用了混合模型仿真进行证明。首先对单独的传统SCR结构与带有新型触发电路的传统SCR分别进行了研究。某一时刻,某类TLP方波的脉冲信号(高于SCR触发电压)被加载到VDD电源线上用以触发SCR器件,然后对SCR阳极电压进行检测,模拟出了SCR在脉冲下的瞬态响应。单独的传统SCR结构的瞬态响应如图7所示,可以看出,该期间大约在24 V左右时被触发,随后将电压钳位到约15 V左右,当ESD结束后,可以看出SCR阳极电压被拉低至2.5 V,发生闩锁效应。带有触发电路的传统SCR结构电压电流响应如图8所示。从图8(a)中可以看到,在经过200 ns的高压脉冲后,SCR阳极电流为0 A,这说明在脉冲触发SCR后,SCR是可以被关断的。由于仿真对比器件是采用一定会发生闩锁效应的传统SCR结构,而带有触发电路的传统SCR结构结果却显示闩锁效应没有发生,因此可以说明辅助触发电路对SCR的关断起到关键作用。该电路仿真的电压响应在图8(b)中示出,对比图7可以看出,ESD结构的触发电压从传统器件的15 V被降低到约6.2 V左右,这明显降低的触发电压增加了ESD反应速度。在ESD放电期间,电压同样被安全地钳位在了15 V左右的水平,电路得以安全保护。ESD脉冲过后,当电源电压恢复到5 V的正常电位时,SCR器件由于被触发电路关断,其阳极电压同样保持5 V的电压。因此该电路实现了ESD信号判别、脉冲的快速触发以及辅助SCR关断的功能。

图7 单独SCR结构闩锁仿真

图8 带有新型触发电路的SCR结构闩锁仿真

5 结束语

本文提出了一种用于ESD防护的新型SCR触发电路。该电路通过微分电路对ESD波形进行判断,在ESD上升沿时输出正向触发电压对后级的SCR门极进行开启,并在ESD下降沿时输出负向抽取电压对后级的SCR门极进行关断。将该电路与传统SCR器件相结合,则不需要对传统SCR器件进行特别的优化即可获得精确快速的ESD触发。如此既能保留传统SCR器件低功耗的优势又能克服其容易闩锁的缺点,提高SCR器件的鲁棒性和抗闩锁能力,大大缓解了SCR器件It2与Vh之间的矛盾。

通过混合模型仿真可以看出,在VDD上电时并不能触发该电路,SCR器件关闭;在ESD事件发生时,电路能精确地识别脉冲信号,从而输出约±9 V的触发/关断信号来对后级的SCR进行开启或关断。

[1]刘红霞,刘青山.0.18μm CMOS工艺下的新型ESD保护电路设计[J].西安电子科技大学学报(自然科学版),2009,36(5):867.

[2]B Song,Y Han,M Li,S Dong,WGuo,D Huang,F Ma and M Miao.Substrate-triggered GGNMOS in 65 nm CMOS process for ESD application[J].IEEE.Electron.Lett.2010,46(7):518-520.

[3]李冰,杨袁渊,董乾.基于SCR的ESD器件低触发电压设计[J].固体电子学研究与进展,2009,29(4):561-565.

[4]V Vashchenko,A Concannon,M T Beek,P Hopper.LVTSCR structures for latch-up free ESD protection of BiCMOS RF circuits[J].Microelectronics Reliability,2003,43(1):61-69.

[5]M D Ker.Whole-Chip ESD Protection Design with Efficient VDD-to-VSS ESD Clamp Circuits for Submicron CMOS VLSI[J].IEEE.Transactions on Electron Devices,1999,46(1):173-183.

[6]颜骏,夏兴衡,吴为敬.一种全N型TFT ESD瞬态检测电路的设计[J].天津工业大学学报,2012,31(4):61-64.

[7]Y Shan,J He and B Hu.PLDD/NHALO-assisted low-trigger SCR for high-voltage tolerant ESD protection in foundry CMOS process without extra mask[J].Electron.Lett.,2009,45(1):40-42.

[8]S Dong,J Wu,M Miao,J Zeng,Y Han,and J J Liou.High-holding-voltage silicon-controlled rectifier for ESD applications[J].IEEE Trans.Electron Device Lett.,2012,33(10):1342-1347.

A SCR Trigger Circuit for ESD Protection

SHAO Hong1,ZHANG Sen1,QIZhao2,QIAO Ming2

(1.CSMC technologies corporation,Wuxi 214028,China;2.State Key Laboratory of Electronic Thin Films and Integrated Device,UESTC,Chengdu 610054,China)

The paper describes a new SCR triggering circuit for ESD protection.It can detect the ESD voltage and output a triggering signal and open the SCR device to protect the inner circuit.After the ESD case,the circuit can detect the fall edge of ESD voltage to output a signal.Then the SCR device will be turned off to prevent latch-up effect.The simulation results show the novel triggering circuit can detect the ESD pulse and output different signals,so it is good for reducing the triggering voltage SCR and preventing latch-up effect.

ESD protection;triggering circuit;triggering voltage;latch-up effect

TN402

A

1681-1070(2017)10-0026-05

2017-6-27

邵 红(1969—),男,江苏无锡人,1991年电子科技大学微电子技术专业本科毕业,东南大学硕士研究生,长期从事集成电路设计和工艺集成等开发工作,主要研究方向为半导体器件、集成电路制造工艺等的设计和研究。