晶体管厄利电压对功放电路静态电流影响实例分析

邱静君

(无锡华润矽科微电子有限公司,江苏无锡214000)

晶体管厄利电压对功放电路静态电流影响实例分析

邱静君

(无锡华润矽科微电子有限公司,江苏无锡214000)

通过对某款功放电路的静态电流随电源电压增加而快速增大的实例,分析了晶体管厄利电压对静态电流变化的影响。通过对同款电路在不同工艺平台中测试结果的对比,分析了静态电流随电源电压变化过快的现象跟晶体管参数厄利电压的相关性,并分析了浅结工艺用于制造功放电路的缺点。分析结果表明通过优化或改变工艺条件(即增加基区结深),使晶体管厄利电压增大,可以解决该款功放电路静态电流随电源电压增大增速过快的问题。

功放电路;静态电流;电源电压;基区结深;厄利电压

2 原因分析和设计改进

2.1 原因分析

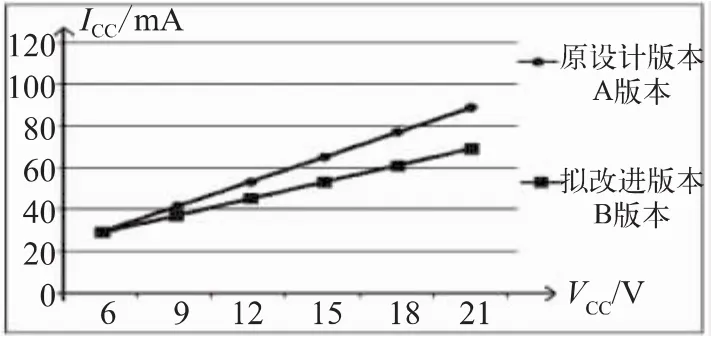

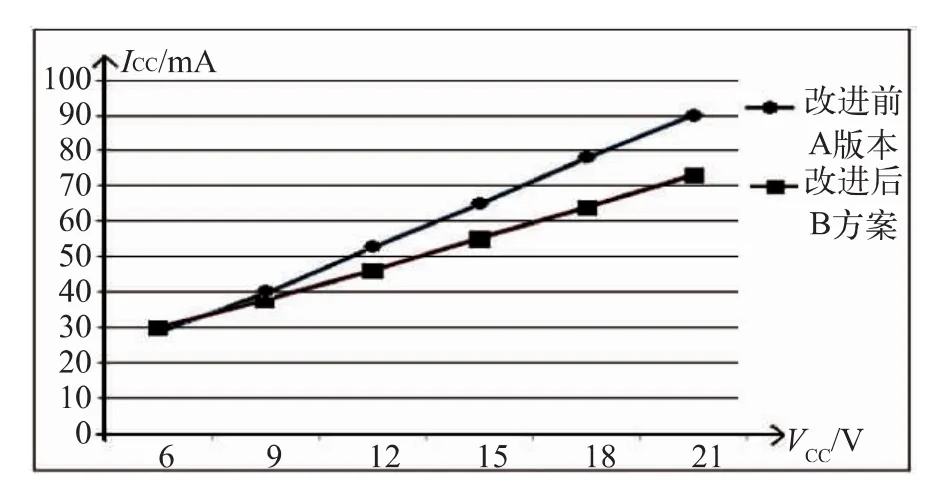

对Icc的测试数据进行分析,该款电路低压下Icc不大,高压下Icc偏大,从分布数据看,A版本Icc随电源电压Vcc的增高增速过快,见图1。

图 1 I cc~V cc曲线

该款功放电路的静态电流由前置电流和功放级电流两部分组成,前置电流较小,功放级电流较大,其整体静态电流的大小基本由功放级电流决定,功放级静态电流跟输出管(N管)的Hfe大小直接相关。

根据仿真结果,该款电路静态电流为:

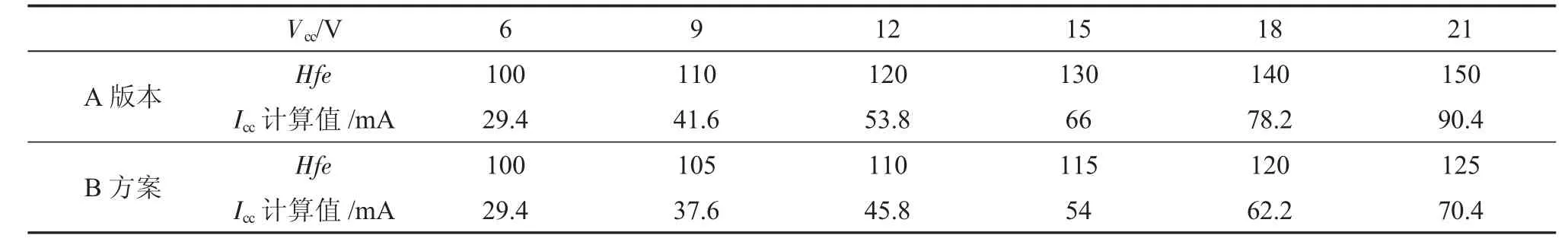

由N管Hfe的测试数据,根据式(1)计算得Icc的数据见表2,跟实际测试数据基本吻合。

由以上分析可以看到,Icc随Vcc的增高增速过快跟N管的Hfe随Vcc的增高而变大的速率较快有关。

2.2 拟进行的设计改进和厄利电压的影响

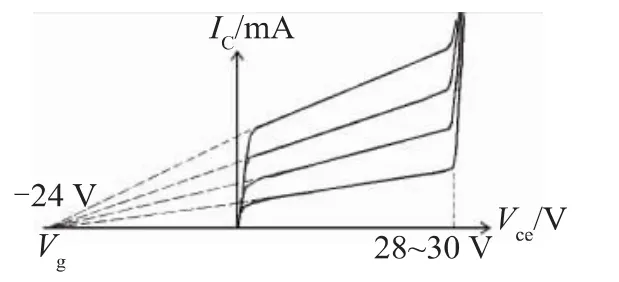

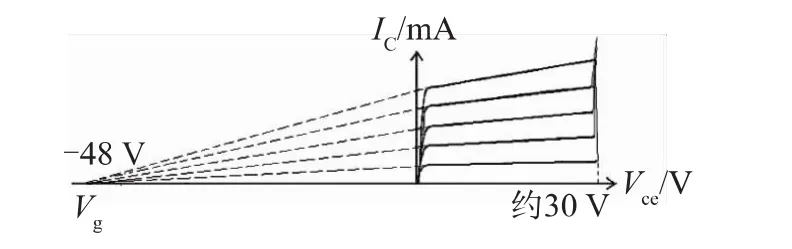

A版本电路N管的Hfe随电源电压的增高而变大,速率较快,厄利电压比较小(Vg≈-24 V),Hfe典型输出曲线示意图见图2。

表2 根据式(1)计算得I cc的数据

图2 A版本(浅结工艺)N管输出曲线

根据客户需求,要求Vcc=12 V时的Icc设计在50 mA以内。根据式(1)计算,要求Icc、Hfe随 Vcc的数据如表3中的B方案,Icc~Vcc关系见图1。

从以上可知,需要改进的B方案要求N管的Hfe输出曲线较平缓,Hfe变化率只有A版本的一半,应该设计将厄利电压Vg增大一倍,Vg=-48 V。B方案改进后要求的Hfe输出曲线示意图见图3。

表3 两种版本下I cc~V cc关系

图3 B版本(深结)N管的Hfe输出曲线示意图

2.3 厄利电压跟基区结深的关系

众所周知,厄利电压(Vg)的定义跟基区宽度调变效应相关,这个效应最大的原因是由于集电结耗尽层宽度随Vce的变化而变化,从而引起基区宽度随Vcc变化。当Vcb=0时,集电结的耗尽层宽度最小;Vcb增加时,集电结的耗尽层增宽,使得有效基区宽度变窄,Hfe增大。

厄利效应主要由集电结耗尽层宽度的变化引起,因此设法减小集电结耗尽层宽度的变化以及减小这个变化对有效基区宽度的影响,都会有利于减小厄利效应。增大基区宽度是提高厄利电压Vg一个非常直接的方法。

就集成电路而言,要详细分析基区宽度调变效应是困难的,因为它需要准确的杂质分布。查阅文献,可以得到均匀掺杂基区的厄利电压近似表达式:

式中,q是电子电荷,NA是杂质浓度,W是基区宽度,ni是本征载流子浓度,Cjc是集电结电容,JB是零偏置下从基区注入到发射区的空穴流,τ是少数载流子的有效渡越时间。从式(2)看到,Vg跟基区宽度近似有比例关系。

2.4 工艺改进方案和改进结果

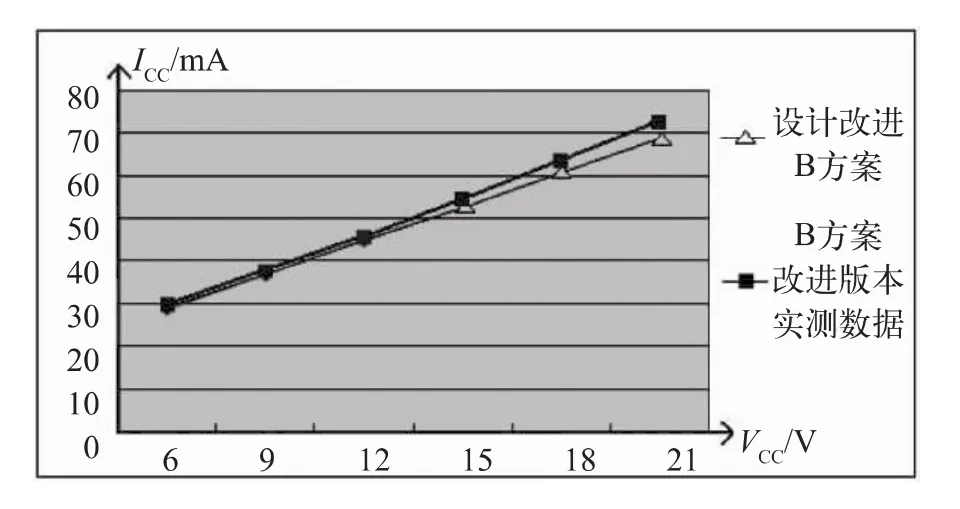

从上面分析中得知,要使Vg提高一倍,近似需要选择基区宽度提高一倍。因此,将上面的B方案通过增加基区结深一倍来实现。B方案设计值和测试结果见表4和图4。

表4 B方案设计值和测试结果

图4 B方案设计值和测试结果比较I cc~V cc曲线

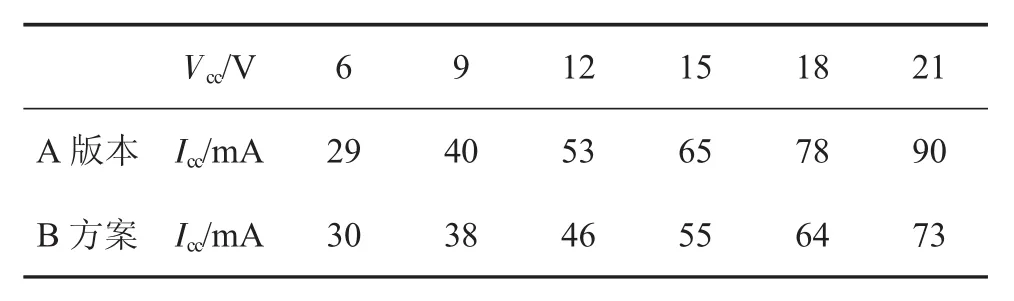

A版本和改进后B方案的测试数据对比见表5和图5。B方案测试结果达到改进目的。

表5 A版本和改进后B方案的测试数据对比

图5 A版本和改进后B方案比较I cc~V cc曲线

3 结束语

通过这个案例,分析了浅结工艺基区宽度调制效应引起的厄利电压小对功放电路静态电流的影响,导致Icc随Vcc的升高增速较快,在高压条件下因为Icc过大而引起电路不能适用。改用相对较深的基区结深可改善此现象,增大电路的电压适用范围。

总结以上,需要指出,对于设计适用于宽电压范围的IC功放电路,应充分考虑浅结工艺厄利电压小对静态电流的影响,注意静态电流随电压变化的斜率。应慎重选择浅结工艺,本次设计改进为此提供了可资借鉴的经验。

[1]D J汉密尔顿,WG霍尔华.集成电路工程基础[M].华南工学院,译.北京:国防工业出版社,1982.

[2]基区复合电流对双极晶体管厄利电压的影响[J].半导体情报,2001,5.

Study of Early Voltage Transistor Effect on Quiescent Current in Power-Amplifier Integrated Circuits

QIU Jingjun

(Wuxi China Resources Semico Co.,Ltd,Wuxi 214000,China)

Based on the case of a given power-amplifier integrated circuit in which quiescent current in creases dramatically with supply voltage,the effect of Early transistor voltage on quiescent current is analyzed.By comparing the test results of the same circuit in different process plat forms,the relativity between Early voltage and changes of quiescent current and the detriments of using shallow junction process in the manufacture of power-amplified circuits are analyzed.Results show that optimization or change of process that increases the Early transistor voltage will perfectly solves the problem.

power-amplifying circuits;quiescent current;power supply voltage;base depth;Early voltage

TN306

A

1681-1070(2017)10-0042-03

1 引言

表1 静态电流Icc测试数据

A版本Vcc/V 6 9 1 2 1 5 1 8 2 1 Icc/m A 2 9 4 0 5 3 6 5 7 8 9 0

2017-6-12

邱静君(1963—),女,浙江台州人,1983年毕业于浙江大学无线电系半导体器件专业,本科学历,从事集成电路设计多年,擅长产品结合工艺分析,曾获国家级、省部级科技进步奖多项。

某款双极功放电路,首次设计时为迎合低电压用户低成本低价格的需求,采用浅结工艺设计(以下简称A版本),利用其较小的设计规则做芯片面积比较小的版本,满足Vcc=6~9 V低电源电压使用的客户需求。电路基本功能良好,静态电流Icc测试数据见表1。随着电路的应用推广,较高电压应用的客户群有使用该电路的需求,但客户希望能把该款电路12 V下大于50 mA的静态电流Icc降低至50 mA以下。针对客户需求,我们对该款电路高压下Icc较大的产生原因进行分析,然后通过改进设计降低了高压下的Icc。