柔性低温多晶硅薄膜晶体管的弯曲稳定性

岳致富,吴 勇,李喜峰,杨 祥,姜 姝,许云龙

柔性低温多晶硅薄膜晶体管的弯曲稳定性

岳致富1,2,吴 勇3,李喜峰2*,杨 祥1,2,姜 姝2,许云龙1,2

(1.上海大学 材料科学与工程学院,上海 200072;2.上海大学 新型显示技术及应用集成教育部重点实验室,上海 200072;3.上海天马微电子有限公司,上海 201201)

研究了以聚酰亚胺为基板的p型低温多晶硅薄膜晶体管在不同弯曲半径下的偏压稳定性。当曲率半径从15 mm变到3 mm时,在拉伸弯曲状态下,阈值电压和平坦时保持一致(Vth=-1.34 V),迁移率μsat从45.65 cm2/(V·s)降到45.17 cm2/(V·s),开关比增大;在压缩弯曲状态下,转移特性曲线和平坦状态保持了非常好的一致性。在最小弯曲半径为3 mm时,进行了正负偏压稳定性测试,结果表明,器件依然具有很好的稳定性。

柔性; 低温多晶硅薄膜晶体管; 低温多晶硅; 弯曲; 稳定性

1 引 言

柔性显示器件因其轻薄、可弯曲、甚至可折叠等特性,得到了广泛的关注[1-2]。非晶硅[3]、多晶硅[4-5]、多元氧化物[6-7]、有机物[8]等有源层材料均可用于柔性薄膜晶体管(TFT)的制备。非晶硅和有机物的迁移率较低,而多晶硅虽然有非常高的迁移率,但需要很高的结晶温度,和柔性基板的低温工艺兼容性不好。低温工艺制备的多晶硅薄膜晶体管可用于柔性TFT,并且具有高迁移率、高集成度等优点,可满足显示面板高分辨率和高帧率的发展要求,具有更好的应用前景。

在实际应用的显示面板的像素电路中,选择管和驱动管会长时间受到栅极偏压作用,所以需要克服栅极偏压引起的阈值电压不稳定性。因为阈值电压的变化会引起源漏电流的变化,从而导致像素点明暗控制不准确。而且,相较于刚性基板上的薄膜晶体管,柔性薄膜晶体管因其可弯曲的特点,会受到机械弯曲应力的影响,因而将面临更加复杂的应用环境,影响器件不稳定的因素更多。Chen等[9]研究了LTPS TFT在栅极负偏压作用下的稳定性,提出导致器件阈值电压漂移的因素不仅包括有源层/绝缘层界面处的陷阱态,还包括有源层沟道中晶界处的陷阱态。Peng[10]和Lee[11]分别研究了以不锈钢和钨箔为柔性衬底的LTPS TFT器件在机械弯曲应力作用下的稳定性,发现阈值电压随弯曲程度的增大而增大,拉伸弯曲使迁移率降低,而压缩弯曲使迁移率增大,认为机械应力使较弱的硅原子之间的键发生断裂,产生悬挂键,增多了多晶硅中的陷阱态。

聚酰亚胺(Polyimide,PI)是成本更低的柔性衬底[12-13],以PI为柔性衬底的LTPS TFT具有重要的应用意义。本文重点研究了柔性PI衬底的p型LTPS-TFT器件在拉伸弯曲和压缩弯曲状态下,不同弯曲曲率下的稳定性,以及极限弯曲状态下的偏压稳定性。

2 实 验

以聚酰亚胺作为柔性衬底制备顶栅结构LTPS-TFT器件。首先,在玻璃基板上旋涂10 μm厚的PI薄膜。然后,通过等离子体增强化学气相沉积法(PECVD)沉积SiO2和SiNx薄膜作为缓冲层,沉积温度为350 ℃,厚度为200 nm。缓冲层不仅可以作为水汽的阻挡层起保护作用,同时其作为无机材料,和多晶硅有源层有更好的兼容性。采用PECVD沉积非晶硅,然后通过快速激光退火,使非晶硅转化成多晶硅,最终得到厚度为80 nm的多晶硅有源层。接着,在室温下通过PECVD沉积200 nm厚的SiO2作为栅绝缘层。沉积并刻蚀钼作为栅电极和源/漏电极。器件的沟道宽/长比为20 μm/10 μm。

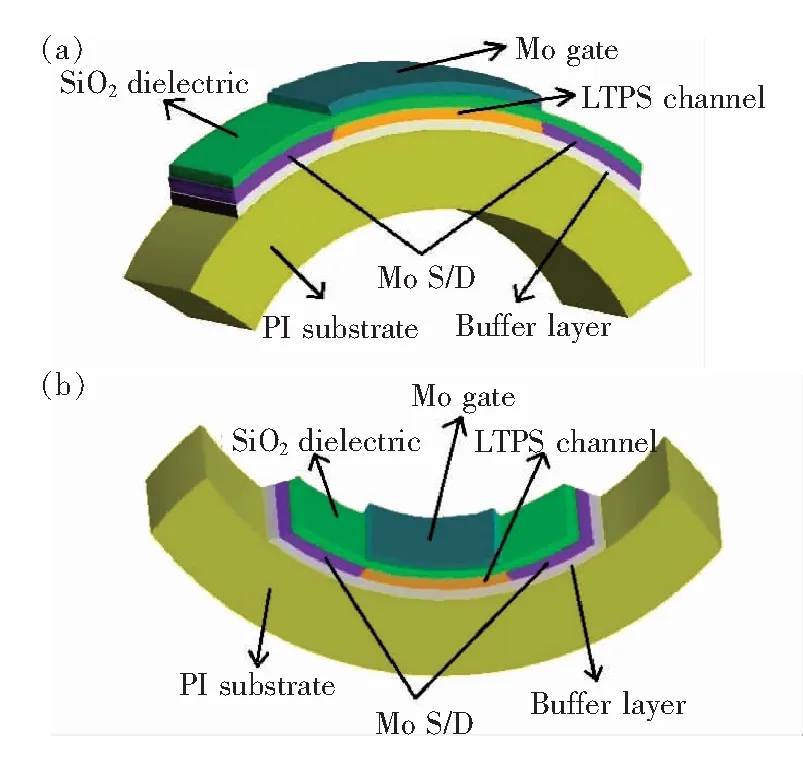

本研究中所有弯曲方向均平行于沟道。选取不同半径的玻璃管,将柔性TFT器件紧贴在玻璃管上,此时器件就发生了相应曲率大小的弯曲,弯曲半径分别为15,10,5,3 mm。拉伸弯曲测试时,器件紧贴玻璃管外壁,以玻璃管外壁半径为准,器件受到拉应力的作用;压缩弯曲测试时,器件紧贴玻璃管内壁,以玻璃管内壁半径为准,器件受到压应力的作用。文中以RS代表拉伸弯曲半径,RC代表压缩弯曲半径。图1为拉伸弯曲和压缩弯曲作用示意图。采用Agilent HP4155C半导体参数分析仪测试LTPS-TFT 器件的输出和转移特性曲线。

图1 (a)拉伸弯曲示意图;(b)压缩弯曲示意图。Fig.1 (a) Stretch bending.(b) Compress bending.

3 结果与讨论

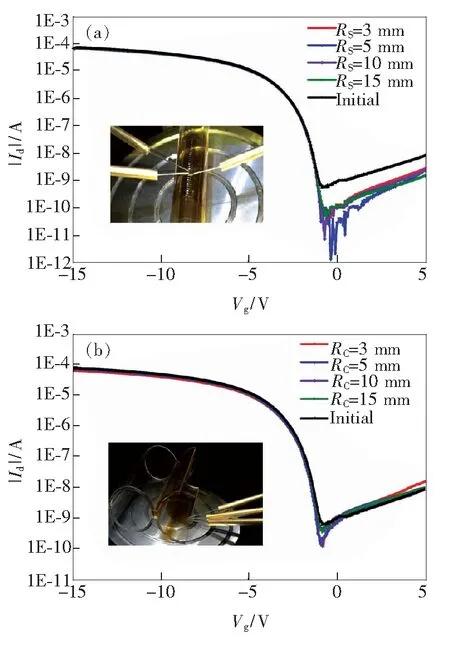

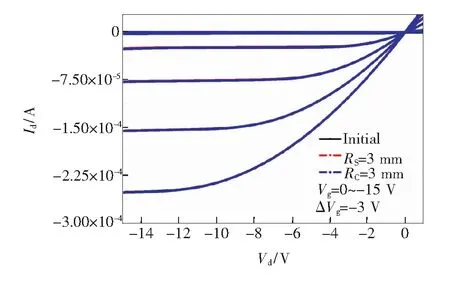

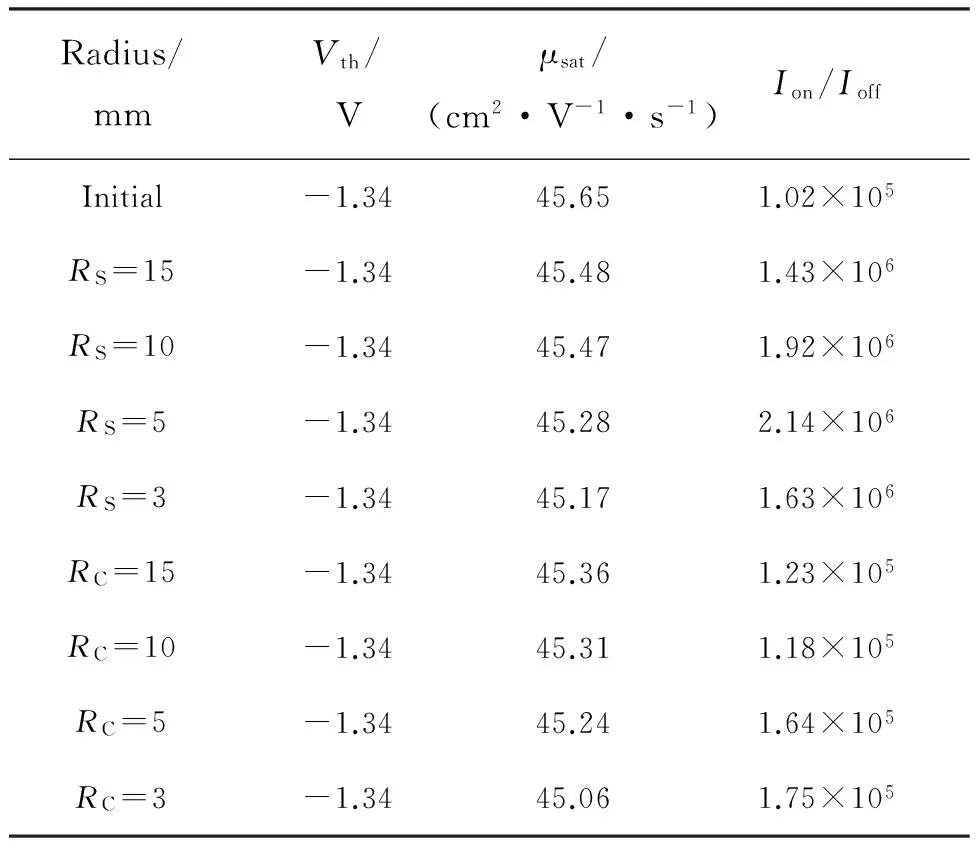

图2给出了在拉伸弯曲和压缩弯曲作用下,不同弯曲半径下的转移特性曲线(Vd=-2 V),图中插图为测试装置照片。从图2(a)中可以看出,在拉伸弯曲状态下,即TFT器件受到拉应力的作用,不同弯曲半径下器件的开态电流基本一致;但弯曲后的关态电流相对于平坦状态时有所降低。这可能是因为受拉应力的影响,沟道形状发生了微小的形变,沟道区被拉长,晶粒间距变大,更易对微小的关态电流产生影响。从图2(b)中可以看出,在压缩弯曲状态下,不同的弯曲曲率下的转移特性曲线和平坦状态时非常重合,说明压应力对器件影响较小。图3所示为平坦状态、拉伸弯曲半径RS=3 mm、压缩弯曲半径RC=3 mm时的器件输出特性曲线。3种状态下的输出特性曲线基本重合,表明弯曲对器件的输出特性没有影响,体现了器件的弯曲稳定性。

图2 不同弯曲半径下,拉伸弯曲(a)和压缩弯曲(b)时的转移特性曲线。插图照片显示了弯曲测试装置。Fig.2 Transfer curves under stretch bending (a) and compress bending (b) with different radii.The inset photographs show the test equipment.

图3 平坦、拉伸弯曲RS=3 mm和压缩弯曲RC=3 mm 下的输出特性曲线。Fig.3 Output curves of initial,stretch bending and compress bending.

将输出电流等于L/W×10 nA时的栅极电压取为阈值电压[9],同时通过公式

(1)

计算饱和迁移率,其中W/L=2,Ci为栅绝缘层的单位电容。

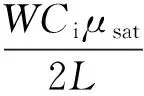

表1给出了不同弯曲半径下的TFT器件性能。平坦时的阈值电压和迁移率分别为Vth=-1.34 V,μsat=45.65 cm2/(V·s)。拉伸弯曲和压缩弯曲时,阈值电压均和平坦时一致,没有出现漂移。饱和迁移率均出现小幅降低:当拉伸弯曲半径RS=3 mm时,降低到45.17 cm2/(V·s);当压缩弯曲半径RC=3 mm时降到45.06 cm2/(V·s)。机械弯曲应力使多晶硅中少量的较弱硅原子间结合键断裂,从而导致悬挂键和缺陷态的产生,降低了迁移率[14]。拉伸弯曲使器件开关比从105增大到106,压缩弯曲时器件开关比依然保持在105。

表1 不同弯曲半径下的器件性能Tab.1 Device performance under various bending radii

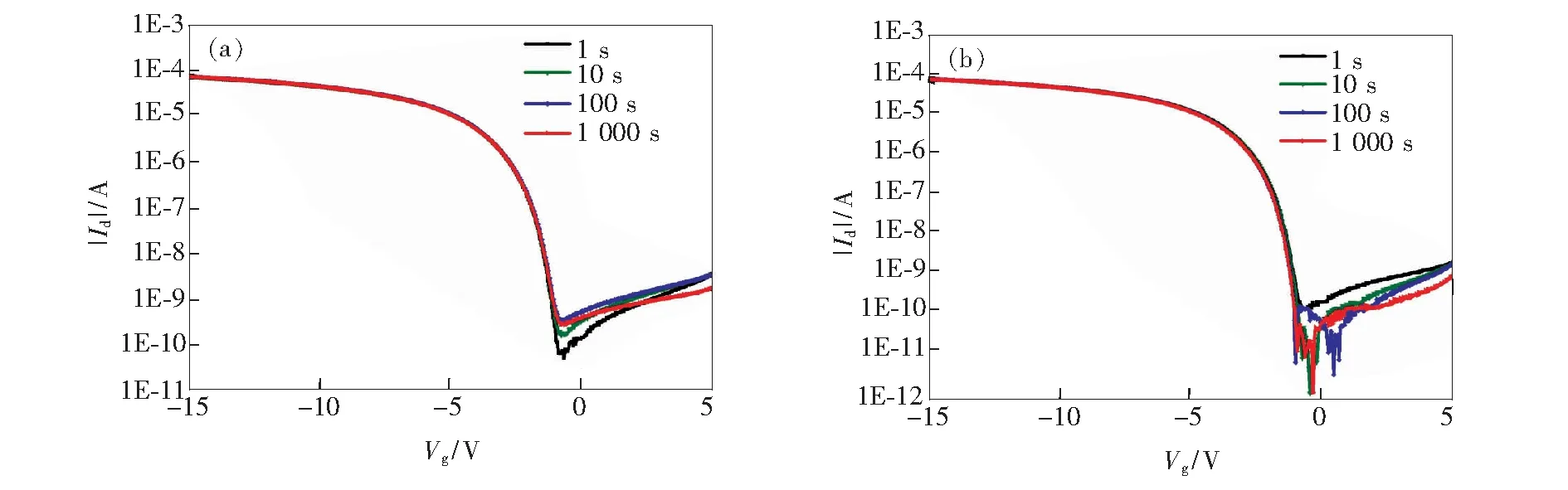

在极限弯曲条件下对器件进行测试是检查器件性能的重要方法。 图4给出了拉伸弯曲半径等于3 mm时,器件在正负偏压作用下的转移特性曲线。由图可见,在负偏压Vg=-10 V和正偏压Vg=10 V作用下,器件性能保持了较好的稳定性,包括阈值电压、开态电流等,只有关态电流在负偏压作用下有轻微的增大,在正偏压作用下有轻微的降低。因为沟道层是p型LTPS材料,靠空穴导电,所以关态下负偏压吸引了微量空穴的存在,导致关态电流轻微增大;相应地,关态下的正偏压减少了沟道中的空穴,从而导致关态电流轻微降低。

图4 拉伸弯曲半径为3 mm时的转移特性曲线。(a)负偏压Vg=-10 V;(b)正偏压Vg=10 V。Fig .4 Transfer curves under stretch bending radius of 3 mm.(a) Negative bias stress Vg=-10 V.(b) Positive bias stress Vg=10 V.

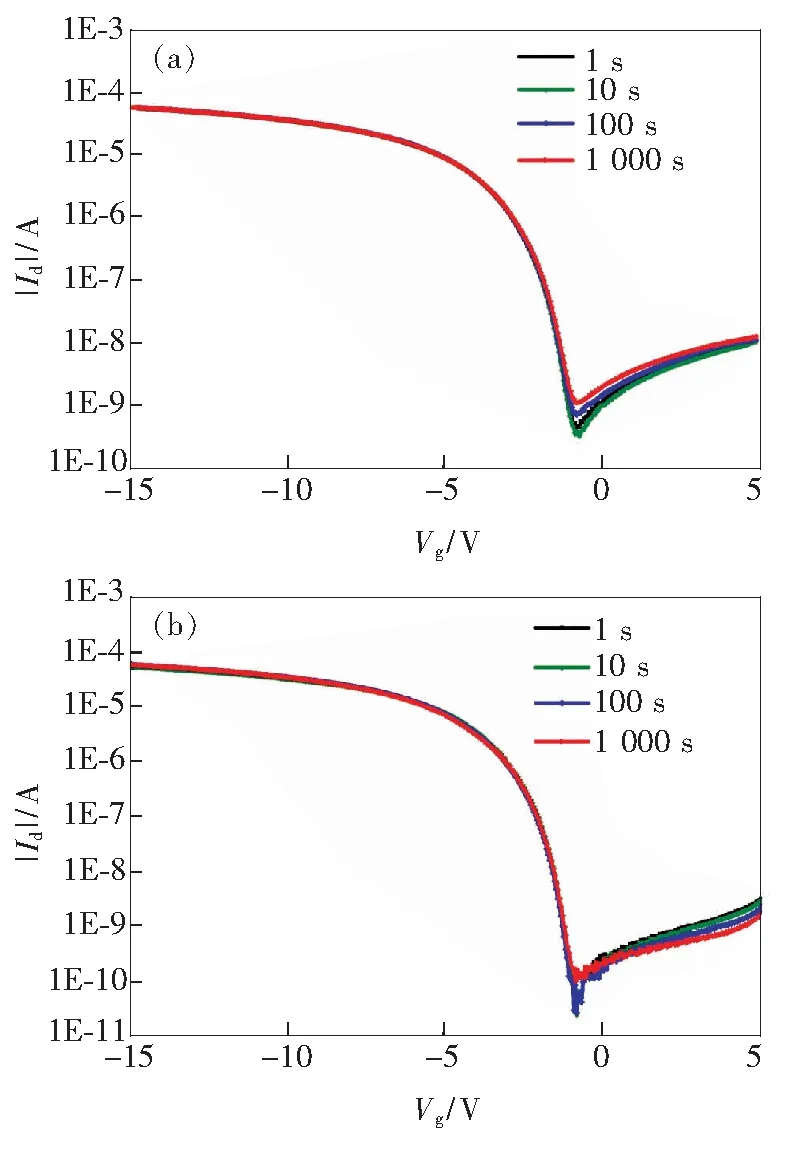

图5 压缩弯曲半径为3 mm时的转移特性曲线。(a)负偏压Vg=-10 V;(b)正偏压Vg=10 V。Fig.5 Transfer curves under compress bending radius of 3 mm.(a) Negative bias stress Vg=-10 V.(b) Positive bias stress Vg=10 V.

图5给出了压缩弯曲半径等于3 mm时,器件在正负偏压作用下的转移特性曲线。由图可见,在负偏压Vg=-10 V和正偏压Vg=10 V作用下,器件性能都保持了较好的稳定性,只有关态电流有轻微的浮动,变化趋势和拉伸弯曲状态下的一致。这说明,即使在半径为3 mm的极限弯曲状态下,拉伸弯曲和压缩弯曲对器件也只有极小的影响,没有严重破坏器件的性能,证明了该柔性TFT器件的抗弯曲稳定性及抗偏压稳定性。

4 结 论

本文研究了不同弯曲曲率下,以及在最小弯曲半径下正负偏压影响时器件性能的稳定性。器件在平坦时的阈值电压和迁移率分别为-1.34 V和 45.65 cm2/(V·s)。在拉应力作用下,阈值电压不变,饱和迁移率小幅降低到45.17 cm2/(V·s),器件的关态降低,从而导致开关比增大。在压应力作用下,器件的转移特性曲线和平坦时比较重合,表现出较好的稳定性。在半径为3 mm的弯曲状态下,器件在正负偏压的影响下只有关态电流有轻微的变化,保持了稳定的电学性能,为LTPS-TFT在柔性显示、柔性传感等领域的应用提供了保障。

[1] CHEN J L,LIU C T.Technology advances in flexible displays and substrates [J].IEEEAccess,2013,1:150-158.

[2] AKINWANDE D,PETRONE N,HONE J.Two-dimensional flexible nanoelectronics[J].Nat.Commun.,2014,5:5678.

[3] LIU K,YAO W H,WANG D Y,etal..A study of intrinsic amorphous silicon thin film deposited on flexible polymer substrates by magnetron sputtering [J].J.Non-Cryst.Solids,2016,449:125-132.

[4] QIN G X,YUAN H C,YANG H J,etal..High-performance flexible thin-film transistors fabricated using print-transferrable polycrystalline silicon membranes on a plastic substrate [J].Semicond.Sci.Technol.,2011,26(2):025005-1-6.

[5] VAN DER WILT P C,KANE M G,LIMANOV A B,etal..Low-temperature polycrystalline silicon thin-film transistors and circuits on flexible substrates [J].MRSBull.,2006,31(6):461-465.

[6] LEE H Y,YE W H,LIN Y H,etal..Performance investigation of amorphous InGaZnO flexible thin-film transistors deposited on PET substrates [J].J.Disp.Technol.,2014,10(9):792-796.

[7] LIU J,BUCHHOLZ D B,CHANG R P H,etal..High-performance flexible transparent thin-film transistors using a hybrid gate dielectric and an amorphous zinc indium tin oxide channel [J].Adv.Mater.,2010,22(21):2333-2337.

[8] ZOCCO A T,YOU H,HAGEN J A,etal..Pentacene organic thin-film transistors on flexible paper and glass substrates[J].Nanotechnology,2014,25(9):094005-1-7.

[9] CHEN C Y,LEE J W,WANG S D,etal..Negative bias temperature instability in low-temperature polycrystalline silicon thin-film transistors [J].IEEETrans.ElectronDev.,2006,53(12):2993-3000.

[10] PENG I H,LIU P T,WU T B.Effect of bias stress on mechanically strained low temperature polycrystalline silicon thin film transistor on stainless steel substrate [J].Appl.Phys.Lett.,2009,95(4):041909-1-3.

[11] LEE W G,LIM T H,JANG J.Flexibility of low temperature polycrystalline silicon thin-film transistor on tungsten foil [J].Jpn.J.Appl.Phys.,2011,50(3S):03CB03.

[12] CHOI M C,KIM Y,HA C S.Polymers for flexible displays: from material selection to device applications [J].Progr.Polym.Sci.,2008,33(6):581-630.

[13] GAO X Y,LIN L,LIU Y C,etal..LTPS TFT process on polyimide substrate for flexible AMOLED [J].J.Disp.Technol.,2015,11(8):666-669.

[14] KUOP C,JAMSHIDI-ROUDBARI A,HATALIS M.Effect of mechanical strain on mobility of polycrystalline silicon thin-film transistors fabricated on stainless steel foil [J].Appl.Phys.Lett.,2007,91(24):243507-1-3.

岳致富(1986-),男,河南信阳人,硕士研究生,2008年于河南大学获得学士学位,主要从事氧化物薄膜晶体管的研究。

E-mail: zhifu@shu.edu.cn

李喜峰(1979-),男,山西大同人,博士,教授,2006年于复旦大学获得博士学位,主要从事薄膜晶体管及印刷电子器件的研究。

E-mail: lixifeng@shu.edu.cn

Bending Stability of Flexible Low Temperature Poly-silicon Thin-film Transistors

YUE Zhi-fu1,2,WU Yong3,LI Xi-feng2*,YANG Xiang1,2,JIANG Shu2,XU Yun-long1,2

(1.SchoolofMaterialsScienceandEngineering,ShanghaiUniversity,Shanghai200072,China; 2.KeyLaboratoryofAdvancedDisplayandSystemApplicationsofMinistryofEducation,ShanghaiUniversity,Shanghai200072,China;3.TianmaMicro-electronicsCo.,Ltd.,Shanghai201201,China)

The bias stability of the flexible thin-film transistors under various bending radii was investigated.The thin-film transistors with p-type low temperature poly-silicon channel layers were fabricated on polyimide substrate.The changing region of the bending radius was from 15 mm to 3 mm.For the stretch bending,the threshold voltage kept the same with the flat(Vth=-1.34 V),the mobility reduced from 45.65 cm2/(V·s) to 45.17 cm2/(V·s),andIon/Ioffincreased.For the compress bending,the transfer curve well kept the same with the flat.When the minimum bending radius was 3 mm,the device was tested under the positive and negative bias stress,and showed good stability.The experiment results indicate that the flexible LTPS-TFTs have fine performance and stability.

flexible; thin-film transistors; LTPS-TFT; bending; stability

1000-7032(2017)09-1205-05

2017-01-24;

2017-03-19

国家高技术研究发展计划(863)(2015AA033406); 上海科学技术委员会项目(16JC1400602)资助

TN321

A

10.3788/fgxb20173809.1205

*CorrespondingAuthor,E-mail:lixifeng@shu.edu.cn

Supported by National High Technology Research and Development Program(863)(2015AA033406);Shanghai Science and Technology Commission Program(16JC1400602)