基于FPGA+DDS的位同步时钟恢复设计与实现

苏淑靖,吴 征

(中北大学 电子测试国家重点实验室,山西 太原 030051)

在数字通信中,位同步是要在接收端确定每一个码元的起止时刻,从而在数据流中区分出独立的码元,它起着为接收信号提供基准的作用[1]。主要体现在产生与接收的数字信号时钟同频同相的恢复时钟,从而准确地解出数据流中携带的数字信息。

常用的位同步时钟恢复电路主要有数字锁相环和1比特位同步器,作为当前的主流技术而广泛使用,但它们的优缺点也是显而易见的。本文在分析了两种位同步时钟恢复方法的原理及其优缺点的基础上,提出了利用DDS高精度分频原理实现快速时钟恢复的设计方案,能够快速稳定地从数据流中恢复出时钟,并且适用于各种频率要求,通用性强。

1 位同步性能分析

数字锁相环是一种闭环结构的位同步电路,1比特位同步器则基于开环结构。下面对这两种电路原理进行介绍,并分析其优缺点。

1.1 数字锁相环法

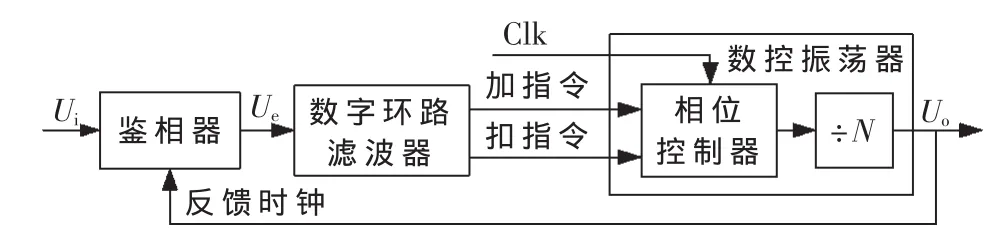

通常数字锁相环主要由鉴相器、数字环路滤波器、数控振荡器三部分组成,其原理图如图1所示。

图1 数字锁相环原理图

首先将输入信号与反馈时钟进行鉴相,得出时钟相位的超前滞后信息;然后在环路滤波器中对超前滞后信息进行计数,当达到模值K时产生加扣指令,数控振荡器根据加扣指令插入或扣除一个时钟脉冲,从而实现时钟相位的调整[2]。

数字锁相环是一个闭环反馈结构,这种结构能够使同步时钟在码元相位出现抖动或者码元消失时不会出现较大变化,仍然可以稳定地输出同步脉冲[3]。也正是因为这种反馈结构,使得数字锁相环法的同步建立时间变得很长,往往需要十几甚至几十个信号周期。

数字锁相环法的原理也决定了它的同步带宽较窄,对于宽范围的不同频率的信号,需要花大量资源去实现脉冲步长的控制以提高同步速度和精度,造成结构复杂。

1.2 比特位同步法

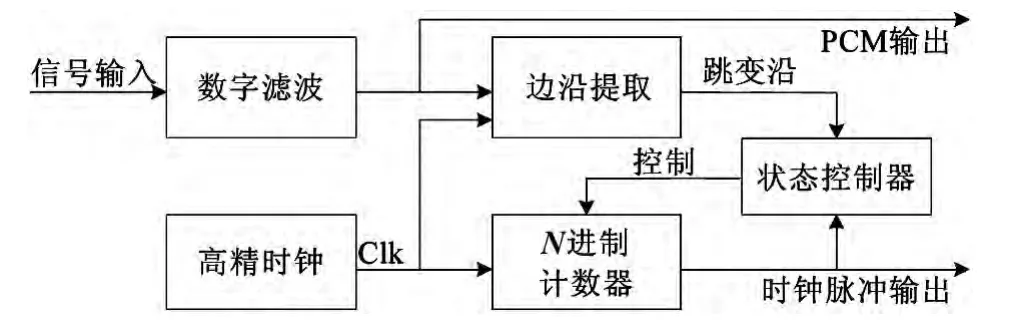

与数字锁相环的闭环结构不同,1比特位同步法是一种开环结构,它主要由双边沿提取电路、状态寄存器和N进制计数器组成,原理图如图2所示。

图2 1比特位同步器原理图

当输入信号发生跳变时,根据边沿脉冲产生一个清零信号,对计数器进行清零,以输出一个反映输入信号相位的时钟短脉冲。状态控制器可以在接收码元出现连“1”或是连“0”时保证仍然会有固定的反映输入信号时钟频率的短脉冲输出[4]。

1比特位同步器的这种开环结构可以在每一个输入信号跳变沿校准码同步时钟的相位。所以,它的同步建立时间很短,可以在出现第一个跳变的码元时就输出正确的码同步信号。同时,这种结构在输入信号由交替变化的“0”和“l”组成时,边沿脉冲可以有效地校正频差。

但是由于跳变沿提取电路的每一个边沿脉冲输出都会对计数器清零,如果跳变沿出现严重抖动,则边沿脉冲信号会与计数器原本的输出产生冲突,造成输出时钟信号占空比大幅度变化,严重时甚至会出现毛刺,对后续电路的功能实现无疑会产生致命的影响。

另外,位同步器输出的是脉冲信号,所以需要添加一个时钟整形电路,将输出时钟脉冲变为占空比50%的时钟周期信号。

2 DDS高精度分频设计

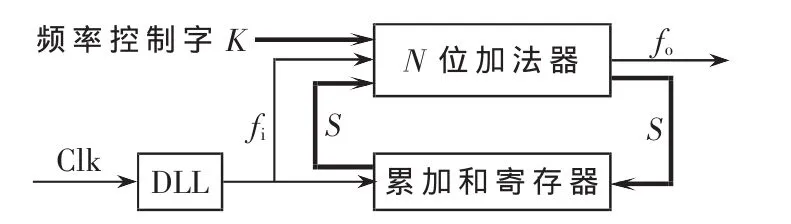

本方案时钟恢复的高精度任意分频利用DDS的相位累加器原理实现,原理框图如图3所示。

图3 高精时钟分频原理图

该时钟分频器由DLL、频率控制字寄存器、N位加法器以及累加和寄存器组成。晶振经过DLL倍频后作为分频器的工作时钟,在每个时钟的上升沿,累加的和与频率控制字进行相加,并将结果保存到累加和寄存器[5]。这个过程中,累加和S会从0开始逐渐增加直到溢出,然后进行下一轮的累加。当频率控制字和加法器位数确定以后,累加溢出的频率就确定了,因为溢出位会按照特定的频率由“0”和“1”交替变化,所以直接将累加和的溢出位作为时钟输出,就可以得到一个占空比为50%的分频时钟输出,而不需要添加时钟整形电路。

设输入时钟频率为 fi,频率控制字为K,时钟输出为fo,N为累加器字长,则有:

在实际应用中,频率控制字K可由式(1)求出。

当分频系数确定时,K不可能取得整数,只是一个逼近值。但是由于N的取值关系,可以达到较高的分辨率。同时分频系数越小,精度越低,反之精度越高。

3 基于DDS的时钟恢复设计

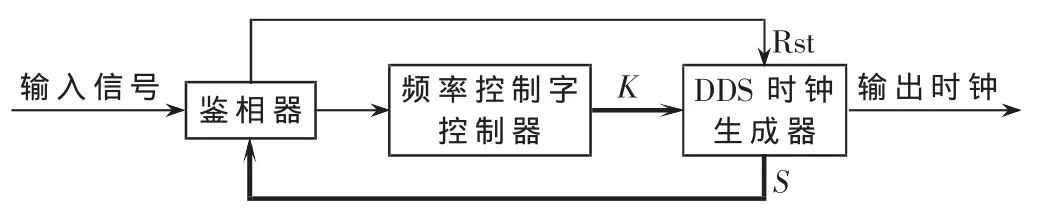

本文设计的位同步时钟提取电路结合了超前滞后锁相环与1比特位同步器的优点,在使用基于DDS原理分频的1比特位同步器时钟恢复方案的基础上添加了一个鉴相器,根据鉴相器的结果调整频率控制字,在一定的周期内,通过控制频率控制字来调节时钟频率和相位,最终实现位同步时钟的生成。基于DDS的时钟恢复设计原理框图如图4所示。

图4 基于DDS的时钟恢复原理图

图4中 K为频率控制字,S为累加和,Rst为复位信号。其工作原理为:首先根据待测信号频率计算出频率控制字K,当有输入信号出现跳变时,鉴相器启动DDS时钟生成器开始生成相应频率的时钟;然后在每个输入信号跳变沿,鉴相器读取相位累加和的值进行判读,频率控制字控制器根据鉴相器判读结果改变DDS分频器的频率控制字来调节相位,从而实现恢复时钟的频率和相位的锁定。

3.1 鉴相器

鉴相器用来提取输入数字信号与时钟信号相位之差。与常用的对两个信号进行比较的原理不同,本文设计的鉴相器是建立在DDS分频基础上的。由于DDS分频原理是通过频率控制字的累加溢出来生成时钟信号,所以可以将其累加和S看作是时钟相位的实时体现,鉴相器只需在输入信号发生跳变时,读取此时相位累加器的累加值并进行判断,就可以得出时钟信号为超前还是滞后,并能同时确定相位误差的值。

信号跳变沿到来时,首先根据此时溢出位的值判断同步时钟处于前半周期还是后半周期。当溢出位为0时为前半周期,为1时则为后半周期。然后根据累加和值S的大小判断相位关系。

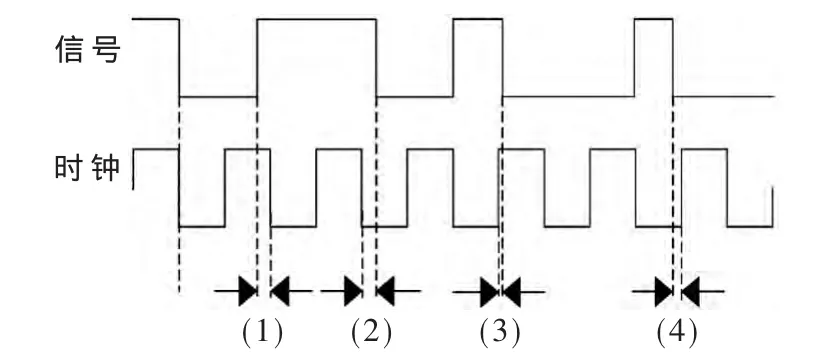

图5所示为两种典型的跳变沿到来时信号与时钟可能的相位关系,其中(1)所示为前向抖动,此时信号的跳变略早于时钟信号;(2)为后向抖动,输入信号的跳变沿略晚于时钟信号。如果以0~M(N位全为1的数)表示完整的时钟相位,则(1)所示相位差为M-S,(2)所示相位差为 S。

图5 时钟相位关系

3.2 频率控制字控制

相位控制以鉴相器输出的鉴相结果作为依据改变频率控制字来实现。首先设置一个抖动容限值L,当相位差小于L时,表示抖动在允许范围以内,不对频率控制字做改变,即不对时钟相位做调整。当相位误差大于L时,如果此时为前向抖动,则将频率控制字左移1位,使相位累加提前溢出,最终使时钟相位前移;如果为后向抖动,则不对频率控制字做改变,而是鉴相器输出复位信号到时钟生成器来快速对齐时钟相位,与1比特位同步法相同。

4 性能分析及仿真测试

与常用的位同步时钟恢复电路相比较,本方案设计的基于DDS分频原理的位同步时钟恢复电路有以下优点:

(1)极大地增加了同步带宽。基于DDS的任意分频方法使得本方案设计的位同步器可以适用于多种频率要求,只需要改变频率控制字就可以得到任意频率的分频时钟,而且可以达到很高的频率分辨率。分频的分辨率同时也是分频的最小值,如式(2)所示:

分频的最大值受限于奈奎斯特定理,理论上为本地高频时钟fi的一半,实际中约为40%。

(2)有效降低了频差的影响。当输入信号出现较长的连续0或者1时,此时没有跳变沿来校正时钟相位,频差会在连续时钟周期内叠加。而基于DDS的分频方法在多个时钟周期的累加过程中,每一次累加溢出时,其余值会进入下一个周期进行累加,而不是清零,这样可以使误差相互抵消,因此即使单个时钟周期误差较大,也不会使误差叠加,将频差的影响降到最低[6]。

(3)可以实现快速、稳定的位同步。当时钟相位误差较大时,能够通过改变频率控制字与复位时钟生成电路,在1~2个周期内快速实现同步,比锁相环法反应更加迅速;与开环结构的1比特位同步方法相比,在大幅相位抖动时不会产生毛刺,时钟更加稳定。

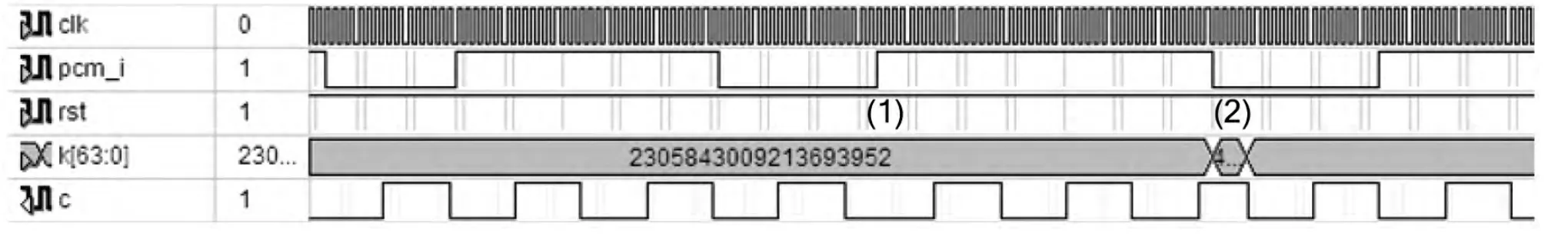

本文在ISE环境下采用VHDL语言设计了位同步提取电路,使用Xilinx公司的Spartan3E系列FPGA芯片XC3S250E予以实现,并进行了仿真实验验证,如图6所示。

图6中 clk为本地时钟,pcm_i为输入信号,K[63:0]为频率控制字,c为恢复时钟输出。可以看出,当输入信号跳变时时钟生成电路开始工作,生成固定频率的时钟信号,时钟上升沿位于码元周期的中间位置,可以更准确地读取码元。在输入信号的跳变沿,会根据时钟信号与输入信号的相差来调整时钟相位,图中(1)所示位置为后向抖动,时钟生成器被复位,以对齐时钟相位;(2)所示为大幅度的前向抖动,此时频率控制字被左移1位,使时钟信号相位前移。

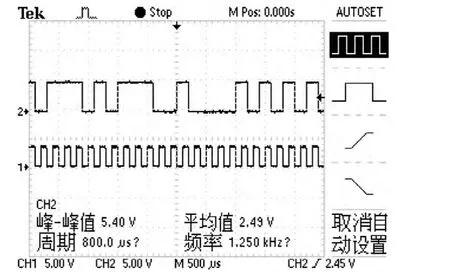

在实际工作时根据需要的频率计算出频率控制字即可,图7所示为实际测试时使用示波器测量的位同步情况,图中上面为输入信号,下面为位同步时钟。结果表明,本方案设计的电路能够实现时钟恢复的功能,其性能稳定。

图7 位同步输出测试

本文提出了一种基于DDS高精度任意分频的时钟恢复方案,与常用的位同步方法相比,具有时钟分频精度高、适用频率范围宽、同步速度快、同步时钟稳定度好以及设计简单等优点。并且该方案经过仿真以及实际测试验证其正确可行,是数字时钟恢复方案的一种很好的选择。

图6 位同步仿真验证

[1]李超,谢雪松,张小玲.一种DDS任意波形发生器的ROM优化方法[J].电子技术应用,2013,39(2):12-21.

[2]陈华君,杨涛.一种基于FPGA的全数字锁相环设计[J].物联网技术,2011,1(10):76-78.

[3]张志文,曾志兵,罗隆福,等.基于新型全数字锁相环的同步倍频技术[J].电力自动化设备,2010,30(2):123-126.

[4]靖文,李斌,屈薇,等.一种快速位同步时钟提取方案及实现[J].电子设计应用,2007(12):84-87.

[5]柳春,甘泉.基于FPGA的雷达信号源设计[J].电子技术应用,2013,39(11):47-49.

[6]黄守麟.基于FPGA的超高精度任意小数分频器的设计[C].第二届全国信号处理与应用学术会议,2008:485-487.