FPGA与通用处理器同步数据传输接口的设计*

胡 强

(中国航天科工信息技术研究院,北京 100070)

在电路与信号系统数据传输领域,现场可编程门阵列FPGA与通用处理器进行数据通信时一般采用通用处理器外部异步总线接口来处理。采用这种接口方式的优点是接口实现简单,易操作;缺点是数据传输速率低。

因此,当系统对数据传输速率要求较高时,这种传统的FPGA与通用处理器之间的异步数据传输方式不能满足应用的基本需求。

一般来说,通用处理器都包含有同步动态随机存取存储器SDRAM(Synchronous Dynamic Random Access Memory)控制器的用途是可以通过接口外部SDRAM存储器[1]扩展外部存储空间。SDRAM因为使用同步逻辑传输数据,因此具备很高的数据传输效率。

如果FPGA与通用处理器进行数据通信时基于SDRAM控制器接口,使用同步逻辑传输数据,数据传输速率将会较异步传输大大提高。采用这种接口方式的优点就是数据传输速率高,缺点是接口实现较复杂。

1 设计思路

为了能够在FPGA与通用处理器之间实现同步数据传输,提高数据传输速率,要求通用处理器应当包含SDRAM控制器,FPGA与通用处理器之间的数据通信则基于SDRAM控制器接口进行。

在满足上述条件的前提下,本文提出的一个设计思路是将FPGA模拟为通用处理器SDRAM控制器的一个外接SDRAM存储器,进而通过SDRAM控制器实现通用处理器与FPGA之间的同步数据传输,以提高数据传输速率。

为了实现上述设计思路,需要在FPGA内部构建双向的同步输入输出接口 STI[2](Synchronous Transmission Interface)与外部通用处理器的SDRAM控制器接口,STI应该严格按照SDRAM控制器接口时序进行工作。

2 实现方法

因为通用处理器的SDRAM控制器专门用来扩展系统外部存储空间,与外部SDRAM存储器进行接口,因此,在FPGA内部构建的双向同步输入输出接口(STI)必须严格按照SDRAM存储器的工作原理来进行设计,通过STI将FPGA模拟为通用处理器SDRAM控制器的一个外接SDRAM存储器。此STI接口一端与外部通用处理器的SDRAM控制器进行接口,另一端与FPGA内部的存储模块或数据处理单元接口。这样,FPGA便可以与外部通用处理器实现同步数据传输,提高数据传输效率。

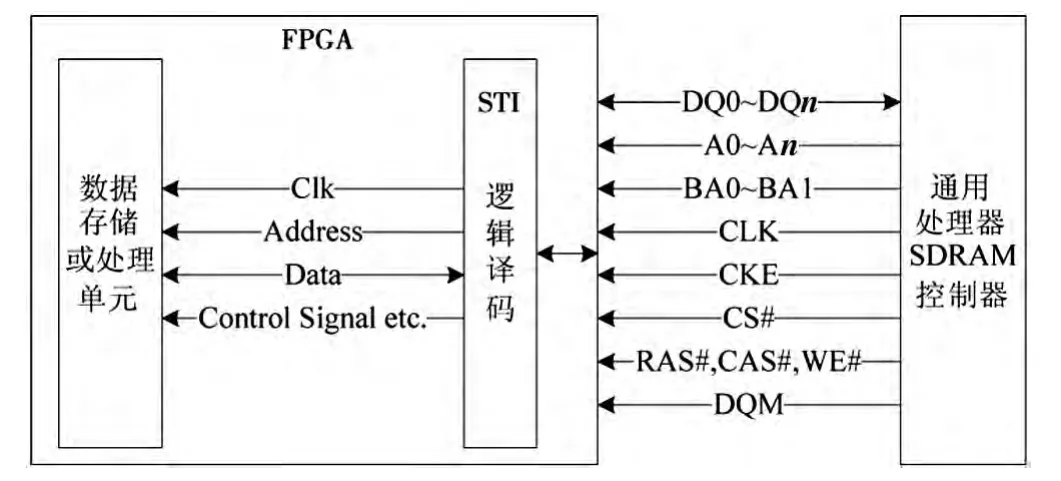

FPGA与通用处理器同步数据传输系统结构框图如图1所示。

图1 FPGA与通用处理器同步数据传输系统结构图

STI做为连接FPGA内部数据存储或处理单元和外部SDRAM控制器的接口,其接口信号输入端为完整的SDRAM信号输入。接口信号输出端为内部数据存储或处理单元的数据、地址及控制等信号。

图1中FPGA与通用处理器之间数据位宽为DQ0~DQ n;寻址空间由地址信号 A0~A n及 BANK信号BA0~BA1来决定;数据传输同步时钟信号为 CLK;时钟使能信号为CKE;片选信号为CS#;命令译码信号为RAS#,CAS#,WE#;数据屏蔽信号为 DQM。

FPGA内部的数据存储或处理单元与STI通过时钟信号 Clk、地址信号 Address、数据信号 Data、控制信号等实现互联。

STI的主要功能就是接收来自SDRAM控制器的同步信号,严格按照SDRAM工作时序对其进行逻辑译码转换,翻译成FPGA内部的数据存储器或处理单元可以正确应用的信号形式,从而确保数据传输的准确无误。

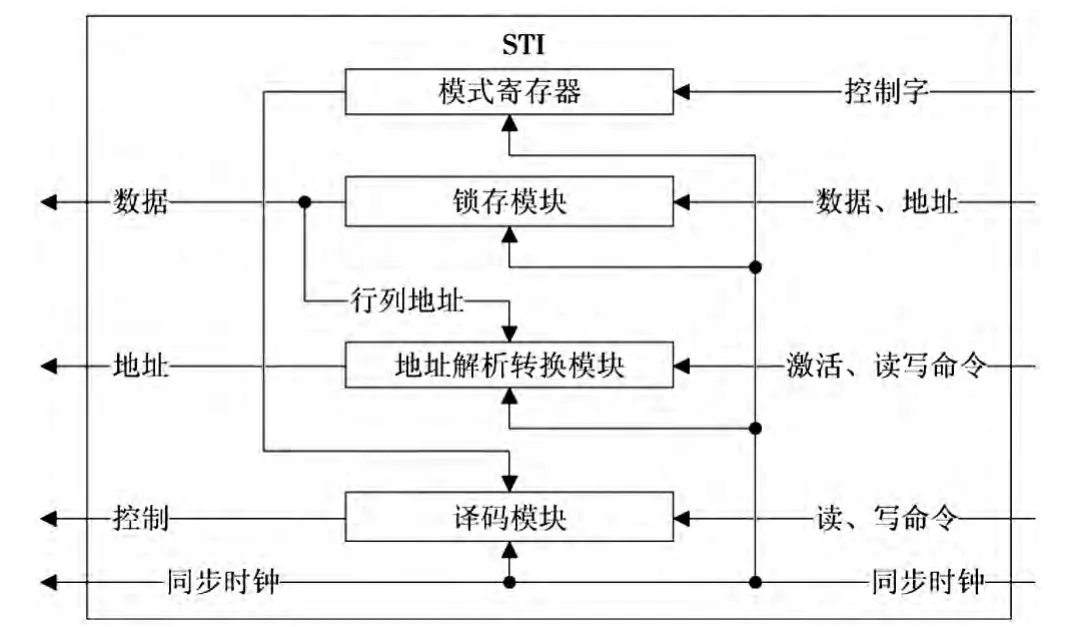

STI包含4个主要的功能模块[3]:模式寄存器、锁存模块、地址解析转换模块、译码模块。STI的功能结构框图如图2所示。

图2 STI的功能结构框图

各功能模块实现的功能分别是:(1)模式寄存器,设定SDRAM控制器的数据突发传输长度和读延时周期;(2)锁存模块,锁存SDRAM控制器发送的数据和地址信号;(3)地址解析转换模块,根据SDRAM控制器的激活、读写等命令,将SDRAM控制器的行列地址进行解析,转换成为FPGA内部数据存储器或处理单元可以直接使用的地址信号;(4)译码模块,结合模式寄存器的配置内容,根据SDRAM控制器的读、写命令,译码出与数据存储器或处理单元接口的读、写、使能等控制信号。

译码模块产生的读、写、使能等控制信号配合地址解析转换模块产生的直接寻址地址信号以及锁存模块产生的数据信号,结合同步时钟信号,共同完成对STI后端数据存储器或处理单元的接口工作。即实现了STI与FPGA内部数据存储器或处理单元的数据实时写入和读取操作,从而完成了FPGA与通用处理器之间数据的实时同步传输。

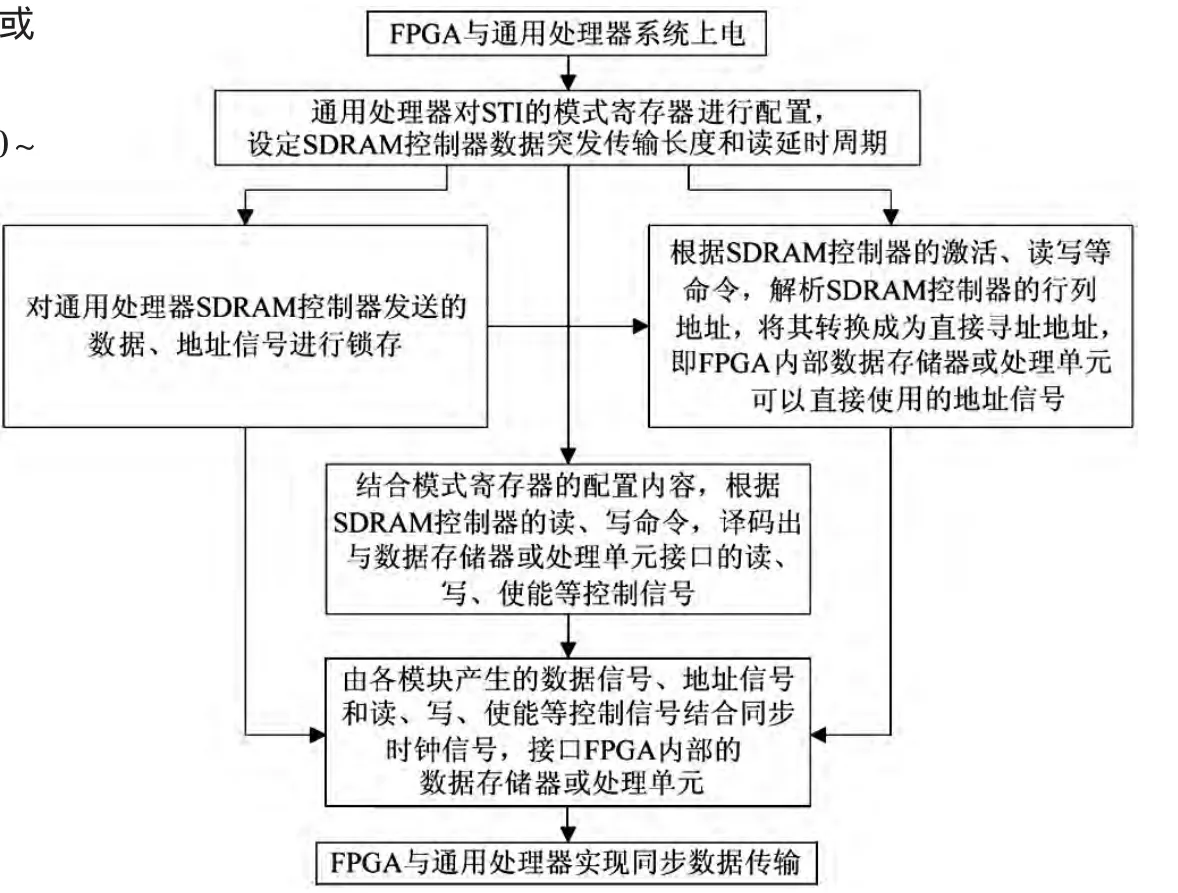

综上可以得到FPGA与通用处理器同步数据传输系统的工作流程如图3所示。

图3 FPGA与通用处理器同步数据传输工作流程图

以上所述功能模块及工作内容的代码实现全部在FPGA内部完成。

3 实测验证

将上述同步数据传输接口设计方法应用于基于数字信号处理器 TS201[4-5]和 EP2S180[6](FPGA)的通用信号处理电路板,已经取得很好的实用效果。经过实际测试,采用该方法后,数据传输正确无误,数据传输速率是传统异步接口传输速率的5倍以上。

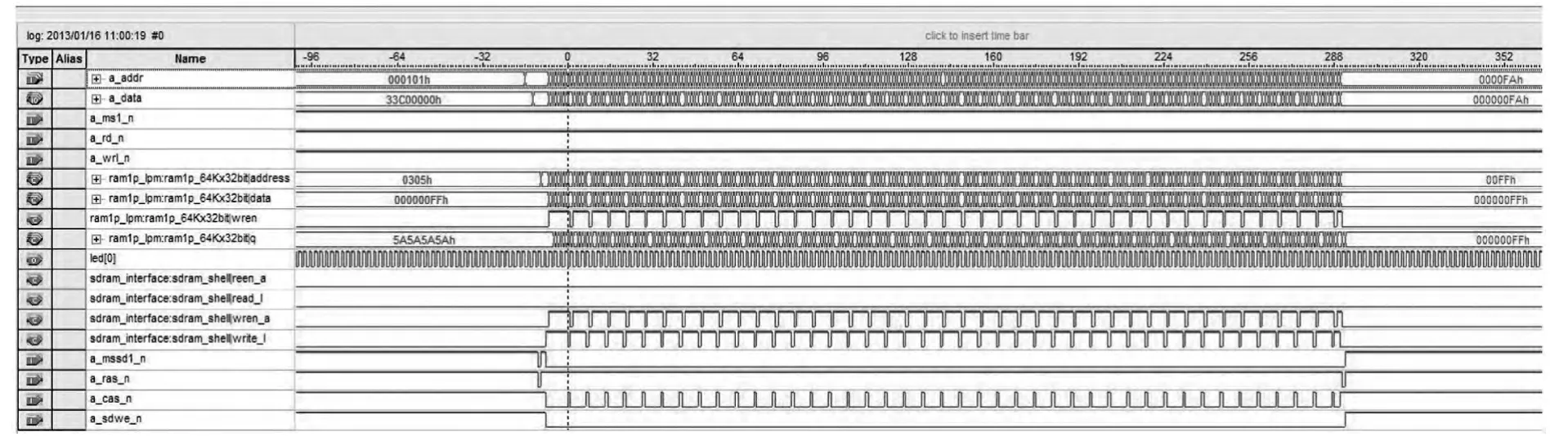

实际测试中,以FPGA内部64 K×32 bit的数据存储单元为例,DSP与FPGA分别进行异步数据传输测试和同步数据传输测试[7],传输一包数据的容量都为64 K×32 bit。通过FPGA开发环境QuartusII自带的 SignalTapII组件对数据传输过程中相关的信号进行实时测试采样。通过测试得到,采用传统异步接口数据传输时序图如图4所示,采用本文所述同步接口数据传输时序图如图5所示。

从图4和图5的时序图可以很直观地看出,FPGA与通用处理器之间采用同步数据传输较传统异步数据传输有明显优势。

本文针对FPGA与通用处理器之间的通信方式,提出了一种通过在FPGA内部构建一个双向同步输入/输出接口(STI)来实现FPGA与通用处理器之间同步数据传输的方法,并详细介绍了该方法的设计思路及实现方法。

本文提供的设计方法具有很高的实用价值,在不增加系统硬件成本的前提下,有效地利用现有资源,将传统的异步总线接口改进为同步总线接口,提高了数据传输的速率,进而极大地提升了系统的工作效率。

最后,给出本文设计方法的应用实例,通过在实际通用信号处理样机上的测试,验证了该方法的实用性和有效性。

图4 采用异步接口数据传输时序图

图5 采用同步接口数据传输时序图

[1]MICRON.256Mb:x4,x8,x16 SDRAM Features[EB/OL].(2012-11-08)[2014-04-01].http://www.micron.com/products/dram/sdram#fullPart&236=2.

[2]夏宇闻.Verilog数字系统设计教程(第 2版)[M].北京:北京航空航天大学出版社,2008.

[3]袁俊泉,孙敏琪,曹瑞.Verilog HDL数字系统设计及其应用[M].西安:西安电子科技大学出版社,2002.

[4]Analog Devices.ADSP-TS201 TigerSHARC®embedded processor,Rev.C[EB/OL].(2012-11-08)[2014-04-01].http://www.analog.com/en/processors-dsp/tigersharc/adspts201s/products/product.html.

[5]Analog Devices.ADSP-TS201 TigerSHARC®processor hardware reference,Revision 1.1[EB/OL].(2012-11-08)[2014-04-01].http://www.analog.com/en/processors-dsp/tigersharc/adsp-ts201s/products/product.html.

[6]Altera.Stratix®II device handbook,Volume 1 and Volume 2[EB/OL].(2012-11-08)[2014-04-01].http://www.altera.com.cn/literature/lit-stx2.jsp.

[7]Analog Devices.ADSP-TS201 TigerSHARC®processor programming reference,Revision 1.1[EB/OL].(2012-11-08)[2014-04-01].http://www.analog.com/en/processors-dsp/tigersharc/adsp-ts201s/products/product.html.