基于FPGA的IRIG-B码解码器设计

顾阳阳,付道文

(西安电子科技大学 电子工程学院,陕西 西安 710071)

基于FPGA的IRIG-B码解码器设计

顾阳阳,付道文

(西安电子科技大学 电子工程学院,陕西 西安 710071)

针对基于单片机的IRIG-B码解码器解码精度低、工作稳定性差等问题,提出了一种基于FPGA的IRIG-B码解码器设计。在实现过程中着重分析了输入IRIG-B码信号的毛刺问题,并采用三级D触发器后接或门的方法,彻底消除毛刺对本系统稳定性的影响。通过仿真验证了本系统具有解码精度高、工作稳定性强、易于实现等优点。

IRIG-B码;解码;毛刺

美国靶场司令委员会(Range Commanders Council,RCC)下属机构靶场间仪器组(Inter-Range Instrumentation Group,IRIG)为保证靶场试验中各参试设备协同工作,制定了一种时间标准IRIG-B码(简称B码),由靶场时统站发送该码,各设备接收此信号后再结合其测量数据,从而达到测量数据的时间同步。我国靶场测量、控制、计算、通信、气象等测试设备,均采用IRIG-B码作为时间同步标准,其特点是可靠性高、接口标准、通用规范及使用灵活方便。

1 B码简介

IRIG-B码为一种串行的时间格式,其中每个脉冲称为码元。IRIG-B码的帧速率为1 fip·s-1,一帧数据由100个码元组成,分为第0、1、2、…、99个码元,每个码元长度为10 ms。时间格式中秒、分、时均用BCD码表示,低位在前,高位在后。第1、2、3、4、6、7、8码元属于“秒”信息,共占用7个码元;第10、11、12、13、15、16、17码元属于“分”信息,共占用7个码元;第20、21、22、23、25、26码元属于“时”信息,共占用6个码元;第30、31、32、33、35、36、37、38、40、41码元属于“天”信息,共占用10个码元。

IRIG-B码由位置识别标志、参考码元、码字和索引标志4种码元组成。

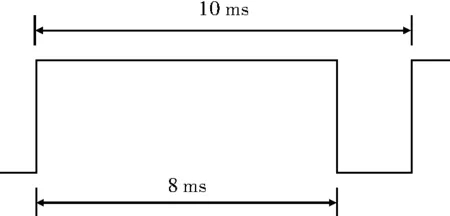

B码的位置识别标志脉宽为8 ms,每帧B码中有10个位置识别标志码元:P1、P2、…、P10。每10个码元有一个位置识别码,位置识别标志的重复率为码元速率的10%。

图1 位置识别标志

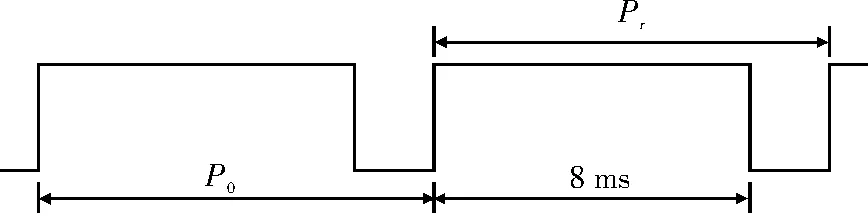

参考码元Pr脉宽也为8 ms,作用是识别帧的起始时刻,“准时”参考点为参考码元的前沿。

图2 参考码元

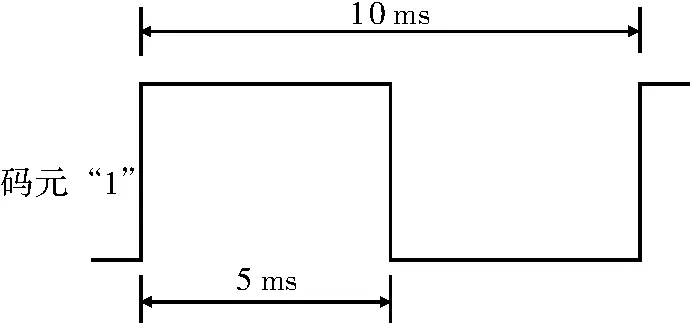

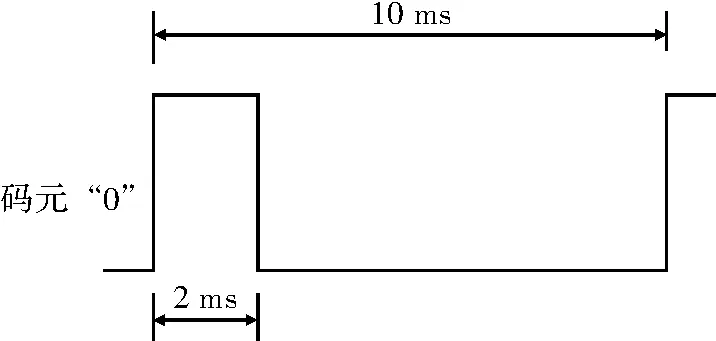

B码的二进制“1”和“0”的脉宽分别为5 ms和2 ms,是用于传递秒、分、时等重要信息的码元。

图3 码元“1”

图4 码元“0”

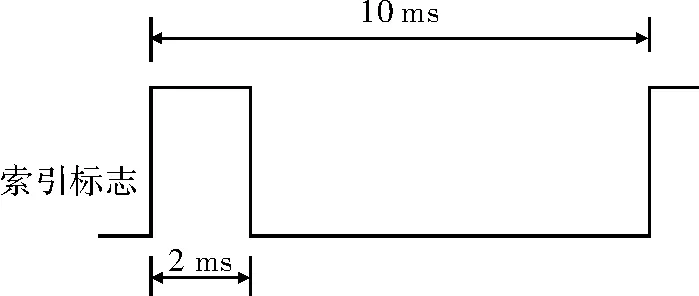

索引标志码元脉宽为2 ms,位于“秒”、“分”、“时”、“天”信息的十位和个位之间。

图5 索引标志

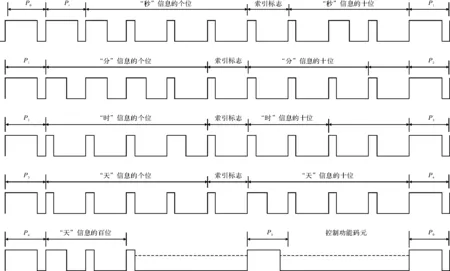

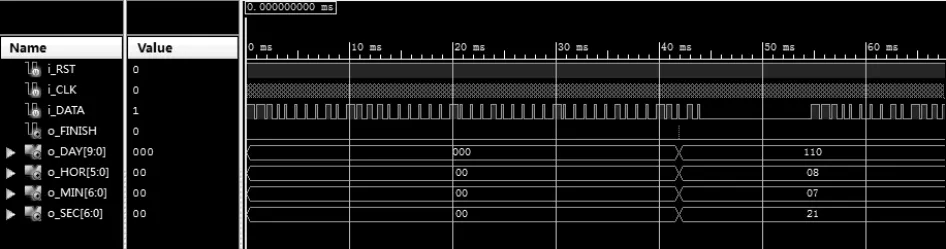

图6为本文B码的一帧数据示意图,后续实验就是对此帧数据进行解码,此帧数据代表的时间信息为:110天8时7分21秒。

图6 B码帧结构示意图

2 FPGA解码

FPGA解码首先需要对码元进行识别,对脉冲计数,以脉冲下降沿作为计数结束。采用有限状态机对第0、1、2、…、99码元进行有序地解码,首先判断出参考码元,再根据5 ms和2 ms码元的位置提取出正确的时间信息。由于不同的系统可能采用不同解码时钟,为使系统有更好的重用性,需要对时钟频率进行归一化。

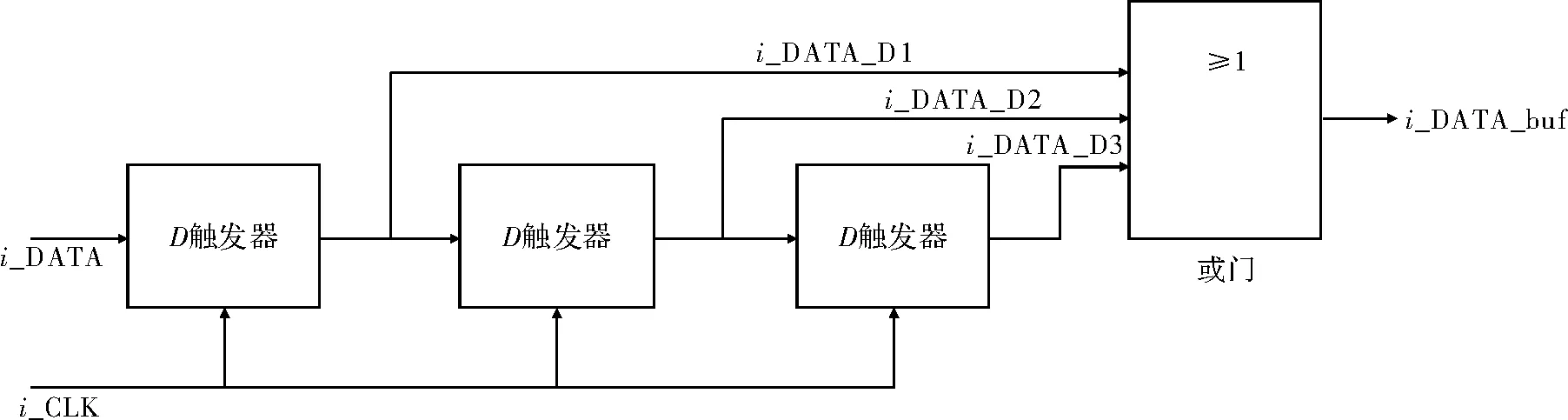

2.1 消除毛刺

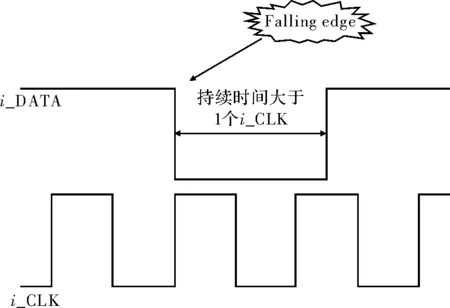

在组合电路、反馈电路和计数器中都可能产生毛刺信号,往往一个毛刺信号会影响整个电子系统的稳定性。由于D触发器对毛刺信号不敏感,通常的处理方法是通过D触发器对输入信号进行“过滤”,但这种方法有效的条件是毛刺不出现在D触发器时钟的上升沿,且持续时间不能维持1个时钟周期,如图7所示,否则,将会放大毛刺信号,对整个电子系统造成更不利影响。

图7 D触发器无法过滤的毛刺

图8 3级D触发器后接或门处理输入信号

若在P码元的5 ms处出现一个毛刺,而不作有效地毛刺处理,将会出现码元误判,甚至会导致整帧数据错误,影响各系统时间同步。输入信号经过图8所示的处理后,不利于系统的毛刺将被“剔除”,从而增强系统的稳定性。

当输入信号处于低电平时出现毛刺,图8的处理方法将会放大毛刺,但对于整个系统是没有影响的,因为本系统采用高电平计数的方式识别码元,当脉宽很窄时,便认为是毛刺干扰,舍去,比上升沿识别码元更简单且更具抗干扰性。这种毛刺处理方法,虽然引入了额外的组合电路,但根据输入信号的特点,是不会产生毛刺的。

2.2 对脉冲宽度进行计数和码元识别

本文采用的归一化时钟为1 MHz,脉宽2 ms、5 ms、8 ms的计数分别为2 000、5 000、8 000,由于脉宽不可能精确到某个值,所以需要放宽计数判别各个码元。计数在1 500~2 500表示2 ms脉宽,计数在4 500~5 500表示5 ms脉宽,计数在7 500~8 500表示8 ms脉宽。输入信号i_DATA处于高电平时,开始计数,当时钟i_CLK采集到i_DATA的下降沿时,即停止计数,并以w_UP_DOWN信号作为脉冲结束标志。

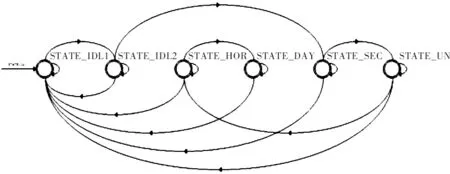

2.3 提取“秒”、“分”等信息的状态机

STATE_IDL1表示处于检测码元,当检测出的码元脉宽为8 ms后,将进入STATE_IDL2。进入状态STATE_IDL2后,当第一个检测出的码元脉宽又是8 ms,则说明此刻检测出的Pr码元,即可以进入“秒”、“分”、“时”等后续检测中;若第一个检测出的码元脉宽不是8 ms,则说明此刻不是帧的起始时间,转入STATE_IDL1状态,继续检测。当进入“秒”检测状态(STATE_SEC),即可依次提取个位和十位信息,为增强系统稳定性,如果发现STATE_SEC状态中的第5个码元不是索引码元,状态便转入STATE_IDL1,否则继续检测“分”、“时”等信息。“分”、“时”、“天”信息的检测过程与“秒”同理。

图9 状态转移图

3 Modelsim验证

根据B码帧结构可知,“秒”、“分”、“时”和“天”信息的第41个,也就是“秒”起始后大约41 ms时刻。从图10中可以清晰地看到大致在仿真时间4 1ms处出现o_FINISH脉冲,o_FINISH作为解码结束标志,即验证了代码的正确性。从图10可知,解码出的时间是110天8时7分21秒。

图10 Modelsim仿真示意图

4 结束语

在FPGA系统中,毛刺是影响整个电子系统稳定性的重要因素。本文中采用的去毛刺方法较好地解决了IRIG-B码解码中存在毛刺的问题,从而提高了系统的稳定性。由于增加了解码结束标志,本文的代码移植性更强。经过Modelsim仿真验证,该解码器功能正确,具有较高的可靠性。

[1] 张斌,张东来,王超,等.基于FPGA的IRIG-B(DC)码同步解码设计[J].测控技术,2008,27(2):45-47.

[2] 郝帅,洪海丽,任宇飞,等.基于FPGA的IRIG-B(DC)码编码与解码器设计[J].国外电子测量技术,2012,31(8):64-67.

[3] 庞吉耀.基于FPGA的IRIG-B编码器实现[J].现代电子技术,2009,32(24):113-117.

[4] 吴炜,周烨,黄子强,等.FPGA实现IRIG-B(DC)码编码和解码的设计[J].电子设计工程,2010,18(12):162-164,169.

[5] 冯娟,史浩山,赵宏伟,等.基于北斗授时信息的B码转换设计[J].信息安全与通信保密,2008(12):92-93.

[6] 魏颖,黄军娜,姬琪,等.基于FPGA的时统设备的IRIG-B时间码设计[J].北华大学学报:自然科学版,2006,7(6):570-572.

[7] 周国平,邢灿华.IRIG-B格式时间编码电路的设计[J].机械制造与自动化,2005,34(2):88-90.

Design of an IRIG-B Decoder Based on FPGA

GU Yangyang,FU Daowen

(School of Electronic Engineering,Xidian University,Xi’an 710071,China)

To solve the problem of low decoding accuracy and poor working stability of an IRIG-B decoder based on the single chip microcomputer,this paper describes an IRIG-B decoding hardware implementation based on FPGA.In the process of implementation,emphasis is put on analyzing and processing burrs introduced by the IRIG-B code signal.The influence on the stability of the system caused by burrs is thoroughly eliminated by the method of three level D flip-flop followed by OR gate.This system has the advantages of higher decoding precision,stability and easy implementation.

IRIG-B;decoding;burr

2014- 10- 17

顾阳阳(1990—),男,硕士研究生。研究方向:电子对抗。E-mail:900224gyy@gmail.com。付道文(1990—),男,硕士研究生。研究方向:电子对抗。

10.16180/j.cnki.issn1007-7820.2015.05.012

TN764

A

1007-7820(2015)05-039-04