基于ZYNQ的IRIG-B(DC)码设计与实现

卢韦明

(西安鼎晟电子科技有限公司,西安 710061)

0 引言

靶场间测量组(Inter-Range Instrumentation Group,IRIG)时间码通常简称IRIG时码[1],是由美国靶场指挥官委员会(Range Commanders Council, RCC)的通信时间组(Telecommunication and Timing Group)制定,用于系统中进行时间信息传输的时间码。 《中华人民共和国电力行业标准》、《中华人民共和国国家军用标准 GJB2991-1997》中明确规定了 B 时间码的格式,其目的是统一不同生产厂家的授时设备的B码输出格式,在时间同步系统与被对时设备互联时可替换。IRIG时间码有A码、B码、C码、D码、E码、G码、H码7种,本文只研究其中的B码。

随着电网的快速发展和电厂自动化设备的大规模应用,在生产和控制中对高精度时间同步设备的需求迅速增加。电力系统中的高精度时间同步是电网操作控制和故障分析的重要保障[2]。

电厂控制系统可从IRIG-B(DC)码获取天、时、分、秒时间信息,然后对系统内的时间进行校准,从而实现全部设备之间的时间同步。为了确保自动化设备接收到精确的时间同步信号,安全、稳定、可靠的时间源非常关键,本文B码时间源采用我国自主研发、独立运行的北斗卫星导航系统作为标准时间源,能够摆脱美国全球定位系统(Global Positioning System,GPS)的限制,向电厂提供安全可靠的授时[3-4]。

通过对现有的IRIG-B (DC)码授时设备的调查研究发现,大多设备采用CPLD+AVR MCU或FPGA+DSP实现[5],该方法各个芯片之间的连线较多,PCB设计复杂,面积较大,加工费用昂贵。

Xilinx ZYNQ-7000系列器件将处理器的软件可编程能力和FPGA(Field Programmable Gate Array)的硬件可编程能力完美结合,通过硬件、软件和I/O的可编程性,实现了扩展式系统级差异、集成和灵活性,并具有低功耗、低成本等优势,凭借其无与伦比的系统性价比,加速了其产品上市进程。在单个芯片上完成以前需要多个芯片相互配合才能实现的功能,使得设计设备的集成度更高、可靠性更高,将是未来电子产品设计发展的必然趋势[6]。

ZYNQ平台在PL(Programmable Logic)和PS(Processing System)端能够实现根据客户要求而定制的逻辑和软件,修改方便且不增加硬件成本[7]。本文主要从以下两个方面进行研究:

1)研究PL和PS之间的DMA(Direct Memory Access)数据传输,代替FPGA+DSP方案中SRIO(Serial RapidIO)芯片之间的数据传输。FPGA中的SRIO IP核需要付费才能使用,增加了开发成本。

2)研究PL和PS之间的AXI(Advanced eX-tensible Interface)数据传输,AXI数据传输是芯片内部数据传输,代替FPGA+DSP方案中芯片间数据传输的片选信号、读写使能信号、数据总线和地址总线,避免了芯片之间的过多连线,降低了PCB设计难度,提高了数据传输的可靠性。

1 硬件组成

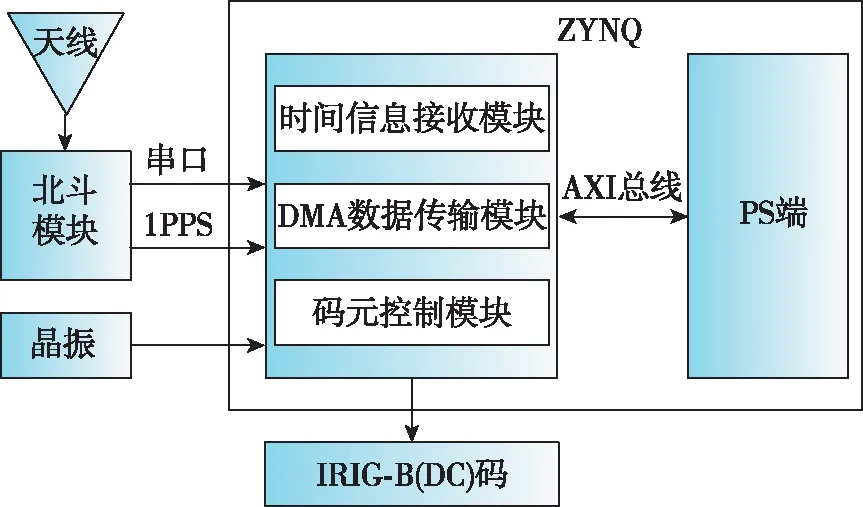

硬件组成框图如图1所示。

图1 硬件组成框图Fig.1 Hardware composition block diagram

图1中,天线:接收北斗B1频点信号;北斗模块:完成北斗B1频点信号的捕获和跟踪,解算出位置和时间信息;晶振:ZYNQ工作时钟;ZYNQ:完成北斗模块输出时间信息的接收、解析和提取,以及B码的生成等功能。

2 软件设计

2.1 IRIG-B(DC)码介绍

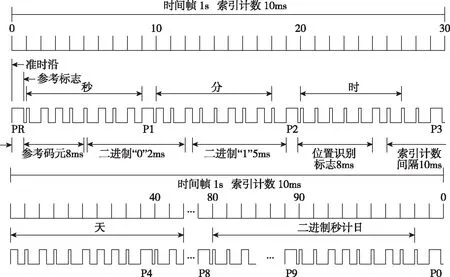

IRIG-B(DC)码格式[8]如图2所示。

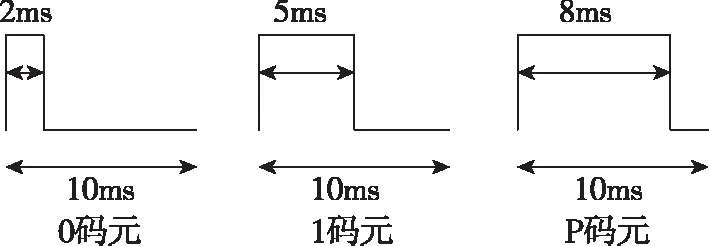

IRIG-B(DC)码码元分为三种,分别为0码元,1码元和P码元,如图3所示。

图2 IRIG-B(DC)标准时间码Fig.2 IRIG-B(DC) time code

图3 IRIG-B(DC)码码元Fig.3 IRIG-B(DC) code element

IRIG-B(DC)码每帧周期1s,共100个码元,每个码元10ms,码元索引计数从0到99。在准时沿时刻码元的索引计数值为0,向后顺次累加,直到该帧结束。

IRIG-B(DC)码共包含10个位置识别标志,记为P0,P1,P2,…,P9,即每10个码元就包含1个位置识别标志。每帧码元中的第0个码元为参考码元PR,每帧码元中第99个码元为位置识别标志P0,参考码元PR和位置识别标志P0 组成了帧参考标志[9]。

IRIG-B(DC)码中的时间表示采用BCD码,共占30个码元,第1,2,3,4码元为秒的个位,表示从0到9计数,第6,7,8码元为秒的十位,表示从0到5计数;第10,11,12,13码元为分的个位,表示从0到9计数,第15,16,17码元为分的十位,表示从0到5计数;第20,21,22,23码元为时的个位,表示从0到9计数,第 25,26码元为时的十位,表示从0到2计数;第30,31,32,33码元为天的个位,表示从0到9计数,第35,36,37,38码元为天的十位,表示从0到9计数,第40,41码元为天的百位,表示从0到3计数。一天中的秒数用二进制表示需17位,从第80码元到第88码元和从第90码元到第97码元,低位在前,高位在后,表示从 0秒到86399秒计数,计数的0秒对应0点0分0秒[10]。IRIG-B(DC)码中其他码元为控制码元,用于控制、识别及多种特殊目的,本次设计预留,默认为0。

2.2 时间信息接收模块

本文设计中将PS端串口用作调试串口,时间信息接收模块串行接收设计在PL端,一方面扩展方便,特别适合多串口接收的硬件设计方案;另一方面减少了PS端中断,使PS端主要处理复杂的运算[11]。

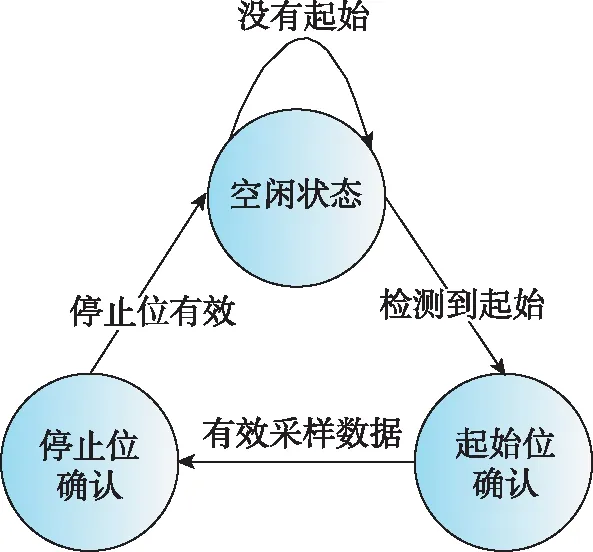

时间信息接收模块串行接收北斗模块输出的“$BDZDA,153256.00,08,07,19,,*ff”协议,其状态图如图4所示。

图4 串行接收状态图Fig.4 Serial receiving status chart

时间信息接收模块串行接收北斗模块输出数据,采用Verilog硬件描述语言实现[12-13],时序图如图5所示。

图5 时间信息接收模块时序图Fig.5 Sequence diagram of time information receiving module

图5中,clk:接收时钟1.8432MHz;rx:接收信号,由高变到低即认为检测到起始位,准备接收数据;cnt:接收位计数器,起始位和数据位采样16次,停止位采样9次,故计数到152即可;flag:计数器标志位,当开始计数时置1,到停止位第9次采样时置0;en:一个字符接收完毕,使能输出;valid:输出接收字符有效标志;data:输出接收字符数据。

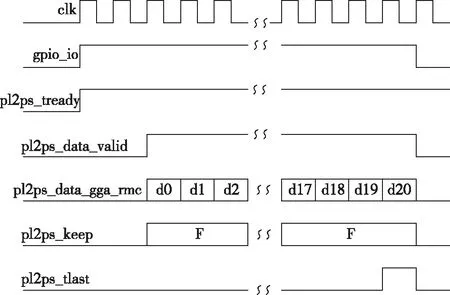

时间信息接收模块接收一帧数据后,再将一帧数据组包传送给FIFO(First Input First Output),时序如图6所示。

图6 时间信息组包时序图Fig.6 Sequence diagram of time information package

图6中,clk:输入时钟,125MHz;gpio_io: 输入信号,PS端初始化完成后,通过AXI总线将gpio_io置1,表示可以向FIFO写入数据;pl2ps_tready:输入信号,每个时钟周期判断FIFO的输入信号ready是否置1,置1则数据写入,准备下一个数据,置0则数据未写入,等待下一个时钟周期写入;pl2ps_data_valid:输出数据有效标志;pl2ps_data_gga_rmc:输出拼位数据,32bit;pl2ps_keep:输出数据字节有效标志,32bit拼位数据共4个字节,1个字节用1bit表示,共需4bit;pl2ps_tlast:输出最后一个数据标志,最后一个数据写入时,pl2ps_tlast信号置1,其他时刻置0。

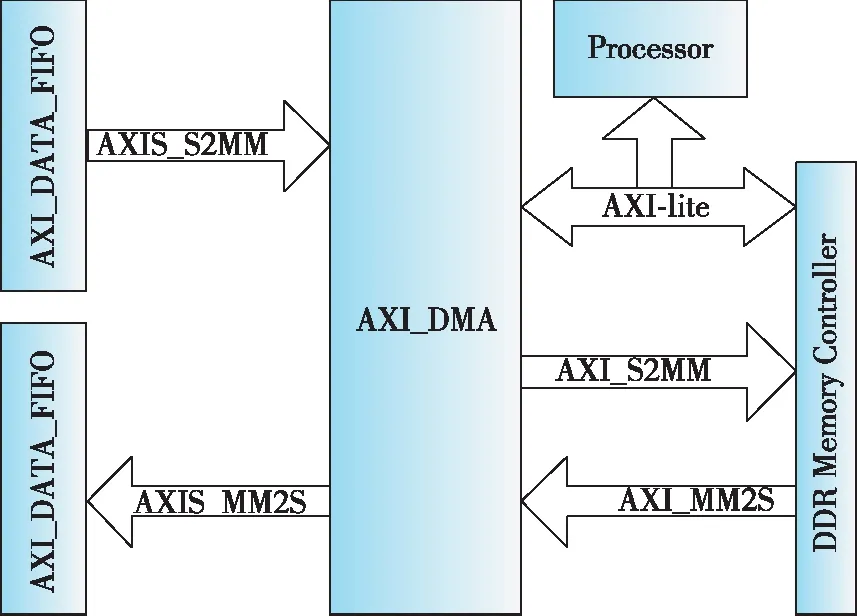

2.3 DMA数据传输模块

DMA在工程中可以将数据从PL端FIFO传递到PS端DDR3,也可以从PS端DDR3传递到PL端FIFO,如图7所示。图7中,AXI_DMA和AXI_DATA_FIFO在ZYNQ PL端,DDR3在ZYNQ PS端。AXI-lite总线实现了处理器配置AXI_DMA模块的建立、初始化和监测数据传递。AXI_MM2S和AXI_S2MM是DMA访问DDR3存储器。AXIS_MM2S和AXIS_S2MM是AXI4-streaming总线,它是传递给DMA的一个没有地址的连续数据流[14]。

图7 DMA数据传输示意图Fig.7 DMA data transmission diagram

本文用到的FIFO模块在从PL端到PS端的数据传送过程中起到异步时钟的跨时钟域处理功能。FIFO接收到一帧数据后,启动DMA传输,DMA模块将时间信息从PL端搬移到PS端DDR3中。

2.4 PS端数据处理

PS端上电初始化后,循环检测接收的北斗时间信息,查询到DMA中断标志位后,PS端从DDR3开始读取数据并存储在数组中,读取结束后按照协议进行计算校验,校验成功后提取定位有效标志和时间信息。北斗模块输出的是UTC时间,需要转换成北京时间,并同时计算当前时刻在一天中的累计秒数,通过AXI总线[15]写入PL端,供码元控制模块使用。在校验错误或无效时则进入守时状态工作,通过AXI总线写入PL端无效标志,其流程如图8所示。

图8 PS端软件流程图Fig.8 PS software flow chart

2.5 码元控制模块

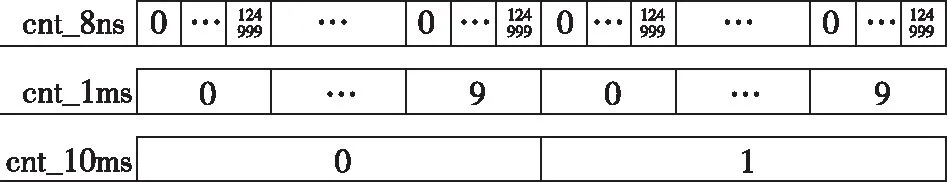

码元控制模块的主要功能是完成接收到PS端有效/无效时间信息时时间变量的赋值/计时和控制码元输出等,需要1ms计数器、10ms计数器、秒计数器、分计数器、时计数器和天计数器来共同完成。

计数器cnt_8ns从0计到124999是1ms,用来控制码元在1ms内的输出值,IRIG-B(DC)码在1ms内输出“1”或者“0”电平。

计数器cnt_1ms从0计到9是10ms,用来控制码元种类,即‘1’、‘0’、‘P’码元,时序图如图9所示。

图9 毫秒计数器时序图Fig.9 Sequence diagram of millisecond counter

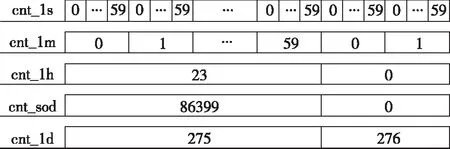

计数器cnt_10ms从0计到99是1s,既用作码元的索引,又用来控制本地时间的守时。如果码元控制模块收到PS端的时间信息有效时,在1PPS信号上升沿时刻将接收到的天、时、分、秒、一天的秒数转换成整型赋给相应时间变量;否则当计数器cnt_10ms从99变到0时刻,时间整型变量做相应进位,秒计数器cnt_1s加1,其他时间计数器也做相应进位,计数器cnt_1s从0计到59是1min,时序图如图10所示。

图10 秒计数器时序图Fig.10 Sequence diagram of second counter

分计数器cnt_1m从0到59是1h,小时计数器cnt_1h从0计到23是1天,1天中的秒数计数器cnt_sod从0计到86399是1天,天计数器cnt_1d从0计到365或366是1年,时序图如图11所示。

图11 分时天计数器时序图Fig.11 Sequence diagram of minute/hour/day counter

码元控制模块在1PPS上升沿下一个时钟周期将整型时间变量个、十、百位分别做BCD码转换。

用计数器cnt_10ms控制码元输出位置,根据秒、分、时、天的BCD码和一天中的秒数(二进制)确定该码元位置输出“0”、“1”、“P”码码元,用计数器cnt_1ms控制1ms内码元的输出值。

3 IRIG-B(DC)码测试

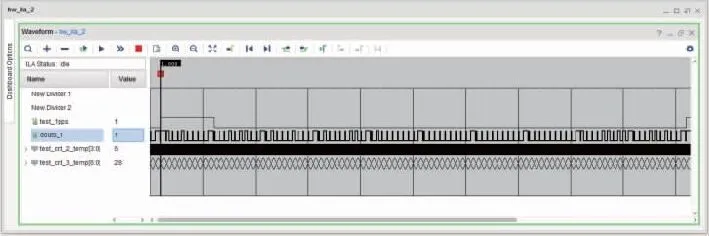

本文在ZC706开发板进行实验,硬件实验环境搭建如图12所示。为了测试验证方便,设置B码模块输入时间固定为275天10时55分56秒,1天中的秒数为39356进行测试。用逻辑分析仪采集输出的b_dc_code信号如图13所示。

图12 硬件开发环境Fig.12 Hardware development environment

图13 b_dc_code信号Fig.13 b_dc_code signal

图13中,doutb_1为IRIG-B(DC)码,从第一个test_1pps上升沿开始,到第二个test_1pps上升沿结束共100个B码码元。

从图13中黑色标志线开始为IRIG-B(DC)码的帧头,开始依次读出码元为P01100101P101001010P000001000P101001110P01,按照图2所示IRIG-B标准时间码格式,对应的秒为56秒,分为55分,时为10时,天为275天;从图13中test_cnt_3_temp计数器为108时为一天中的秒数最低位,125时为一天中的秒数最高位,依次读出码元为001111011P00110010,按照图2所示对应的一天的秒数为39356,表示当天的第39356秒,证明了B码读出时间与设置时间一致。

IRIG-B(DC)码帧头从两个连续P码码元的第二个P码码元上升沿开始,IRIG-B(DC)码(doutb_1)帧头如图14所示,帧头在红色标志线处。

图14 IRIG-B(DC)码帧头Fig.14 IRIG-B(DC) code frame head

4 结束语

本文针对电力设备授时要求,提出了一种IRIG-B(DC)码设计方案并完成了软硬件设计,经过测试IRIG-B(DC)时间码输出正确。采用北斗卫星导航系统为时间源的IRIG-B(DC)码仪器的成功研制,使我国摆脱了依赖国外GPS的现状,对于保障国家安全、促进经济社会的发展都具有重要的意义。