用于频率综合的电荷泵锁相环电路设计

(杭州电子科技大学电子信息学院,浙江 杭州310018)

0 引 言

锁相环(Phase Lock Loop,PLL)具有数据时钟恢复、消除时钟抖动、频率合成等多种用途[1]。自从1965年PLL 集成电路问世以来,PLL 设计技术越来越成熟,从分立器件到集成电路,从双极型工艺到CMOS技术[2]。当今PLL的研究特点集中在低相位噪声、低杂散、高集成度、低电压、低功耗等。在具体设计时,上述这些因素需要相互折衷,以满足特定的应用要求[3]。本文基于CMOS工艺,采用自顶向下的设计方法设计了一款用于频率综合的锁相环,其输出频率范围18.15 23 GHz,相位噪声-90 dBc/Hz,锁定时间小于5 μs。

1 锁相环模型和稳定性分析

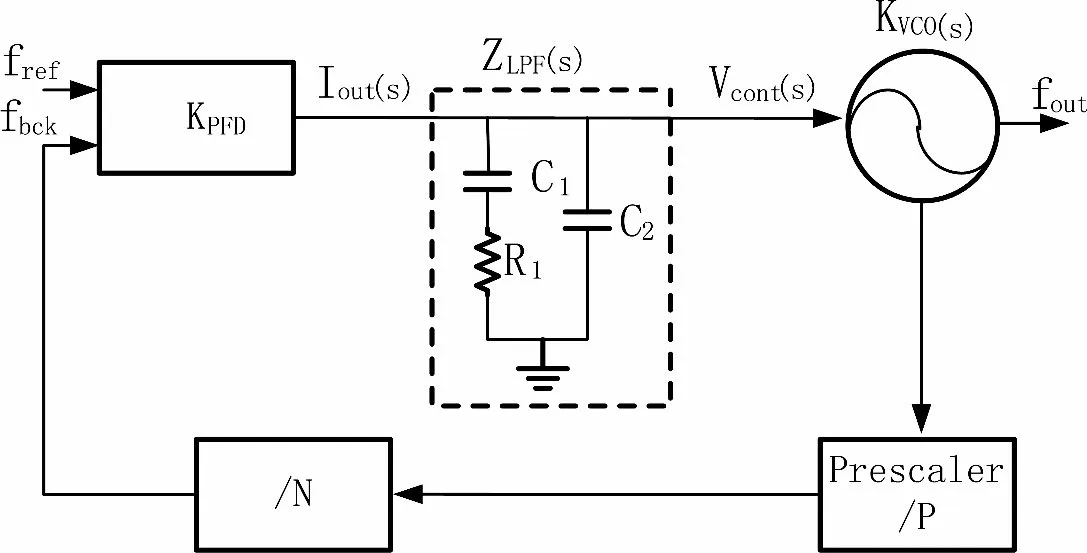

为了能够专业地描述PLL系统,引入PLL的类型和阶数。PLL的阶数是由其传输函数原点处的极点数和总极点数决定的。源于整个PLL系统的特点,PLL系统至少是一阶系统,也就是Ⅰ型锁相环,这是因为VCO的传递函数在原点处有一个极点。为了能够跟踪频率变化,在PLL 环路传递函数原点处引入第二个极点,以便能够将反馈回来信号和输入参考信号的相位差置为零。同时,这个零点是通过在电路中加入电容C1形成的,整个系统则是一个二阶系统,这就是Ⅱ型的锁相环。在原点处两个极点的存在会引起系统稳定性问题,通过在电路中通过电阻R1、电容C1串联引入一个零点来实现系统稳定。引入第二个电容C2用来平坦化VCO的控制电压,这个极点的引入使得PLL系统为Ⅱ型的三阶锁相环。还可以继续引入极点以形成更高阶的PLL,但是一般很少采用,因为环路稳定性问题是一个较大麻烦。S 域简化的PLL系统框图如图1所示,PFD和电荷泵合并到一起,其传递系数为KPFD=ICP/2 。

图1 锁相环模型线性模型框图

二阶滤波器的阻抗为ZLPF,VCO的增益为KVCO,分频器的分频系数为P、N。整个PLL系统的开环传递函数为:

相位裕度和环路带宽是PLL 设计中需要考虑的两个最主要参数,相位裕度越小,锁定速度快;相位裕度越大,幅频特性没有峰值。实际工程中,相位裕度选择范围为40° 50°[4]。

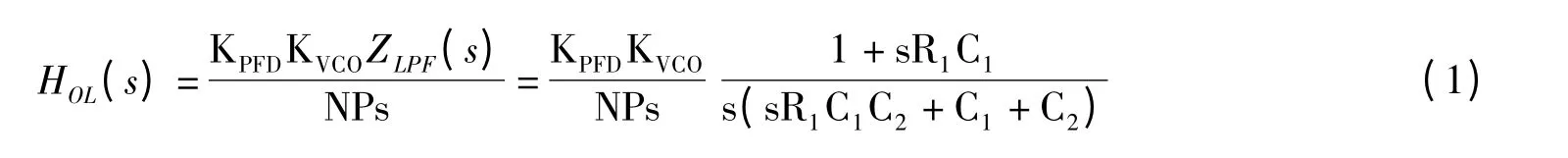

2 锁相环相位噪声分析

相位噪声是PLL系统最重要的考虑因素之一,直接影响信号的调制、解调,并且通过相应的混频会降低信噪比[5]。PLL的噪声分为两大类,第一类是输入参考噪声源,包括PFD、LPF、divider和参考信号噪声;第二类是输出参考噪声源,主要来源于VCO的相位噪声。这两种类型的相位噪声的输出传递函数可以分别表示为[6]:

式(2)具有低通性,即输入参考相位噪声在低频情况下会传输到输出端;式(3)具有高通性,即VCO的相位噪声在环路带宽内会得到很好的抑制。因此,在带内,PLL系统的相位噪声主要来自输入参考信号、PFD、LPF以及dividers;在带外,PLL的相位噪声基本上等于VCO的相位噪声。

3 PLL系统级设计与仿真

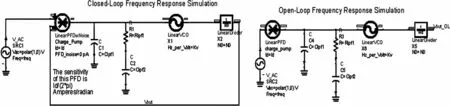

Agilent 公司的ADS 软件集成有大量的设计与仿真工具,这些工具是进行PLL 设计与仿真较好的选择。ADS平台搭建的PLL 设计与仿真环境如图2所示,通过系统级设计与仿真初步确定各个模块的电参数指标和模块之间连接要求。

图2 基于ADS的锁相环系统级电路设计与仿真

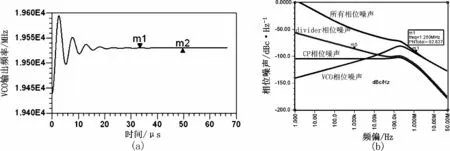

锁相环的环路带宽和相位裕度等系统参数对于整个系统的稳定性和输出噪声影响非常显著,具体设计过程中这些参数的设计确定要综合考虑。环路带宽为100 kHz的PLL 瞬态响应和相位噪声仿真结果如图3所示,图3(a)中,PLL系统瞬态响应在20 μs 后能够实现系统稳定,即锁定;图3(b)中,系统最终相位噪声包括各个模块对系统的贡献,优化系统的相位噪声性能时需要综合考虑各模块相位噪声。

图3 100 kHz的锁相环电路的瞬态仿真和相位噪声曲线

4 PLL 电路设计

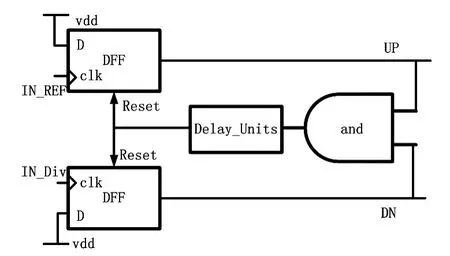

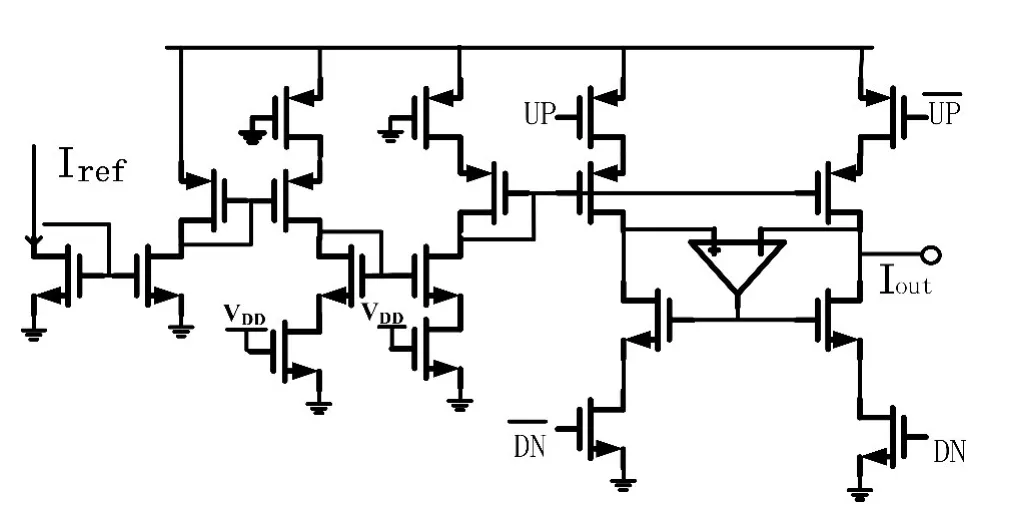

鉴相器通过比较输入信号与反馈信号的相位差,输出一个正比于该相位差的信号。鉴频鉴相器电路结构如图4所示,为了消除死区效应,在与门和复位路径间添加了延时单元电路。电荷泵电路如图5所示,在电荷泵电路实现过程中,采用大尺寸晶体管作为电流源以减小晶体管的阈值电压失配和沟道长度调制效应,同时引入反馈来改善电流源电流的匹配性能。

图4 带有延迟单元的PFD 电路图

图5 电荷泵电路

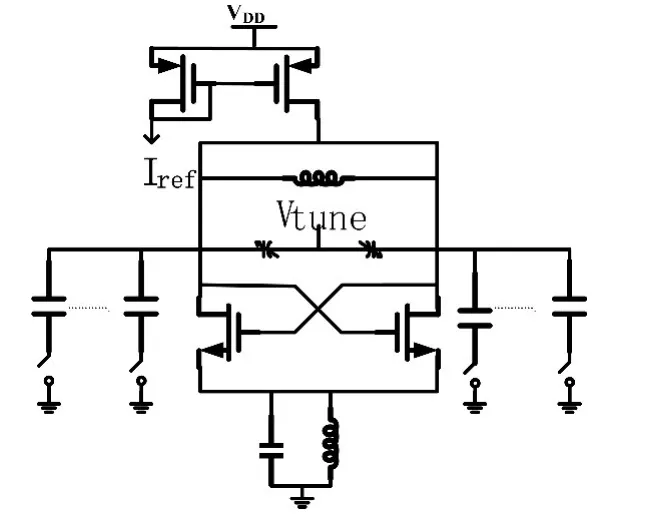

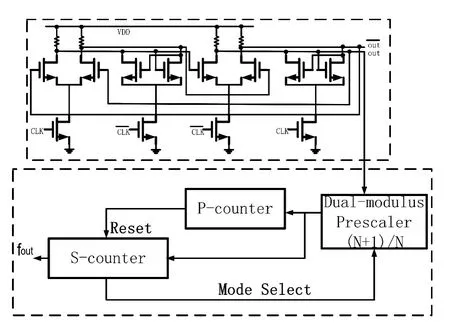

设计VCO时,主要考虑的参数还有功耗、调谐范围、增益、相位噪声等。VCO 电路采用PMOS 管作为VCO的尾电流源管,如图6所示。图6中的LC 谐振网络根据所需要的频率调谐范围和调谐增益来设计的。分频器电路如图7所示。为了满足高频电路的高速、大带宽和低功耗要求,采用电流模逻辑(Current-Mode-Logic,CML)。低频的分频器采用的是基于双模预分频器和计数器的程控分频器。

图6 VCO 电路

图7 分频器电路

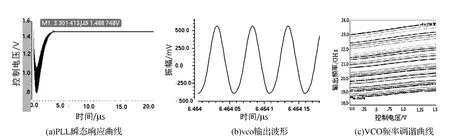

cadence平台搭建的PLL 电路瞬态仿真结果如图8所示,图8(a)中,PLL 在4 μs 左右能够锁定。图8(b)、(c)是VCO的输出波形和频率调谐曲线,它的输出信号的频率范围为18.15 23.43 GHz,输出振幅约为570 mV。

图8 PLL 瞬态仿真

5 结束语

本文基于锁相环理论阐述了锁相环工作原理、设计方法、优化方法等,详细地分析环路稳定性原理和相位噪声性能。并且,从锁相环路稳定性和相位噪声入手,设计了一个用于频率综合器件的锁相环系统,最终基于CMOS工艺给出了具体电路设计并仿真。电路性能满足设计要求,下一步计划进行layout设计和流片测试。

[1]Behzad Razavi.陈贵灿,程军,张瑞智,等译.模拟CMOS 集成电路设计[M].西安:西安交通大学出版社,2002:432-472.

[2]Kosunen M,Vankka J.A CMOS quadrature baseband frequency synthesizer modulator[J].Analog Integrated Circuits and Signal Processing,1999,18(8):55-67.

[3]Floyd B A.A 16-18.8 GHz sub-integer-N frequency synthesizer for 60 GHz transceivers[J].IEEE journal of Solid-State Circuits,2008,43(5):1 030-1 037.

[4]池保勇,余志平,石秉学.CMOS 射频集成电路分析与设计[M].北京:清华大学出版社,2006:500-505.

[5]Hegazi E,Sjoland H,Abid A A.A Filtering Technique to Lower LC Oscillator Phase Noise[J].IEEE Journal of Solid State Circuits,2001,36(12):1 921-1 930.

[6]Rogers John,Plett Calvin.Integrated Circuit Design for High-Speed Frequency Synthesis[M].London:Artech House Publishers,2006:43-83.