高频、低相噪、双模分频器设计

贾岳珉,高晓强,曲晓华

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引 言

随着通信、雷达等电子装备系统的不断发展,其工作频率越来越高,为了降低后级信号处理系统的难度,通常在系统中会利用分频器将高的工作频率分频为低频信号,因此分频器的最高工作频率以及分频器的附加相位噪声成为分频器的关键指标。

1 2/3分频器电路架构

2/3分频器是一种常用的双模分频器,本文主要针对基本的2/3分频器进行分析[1]。

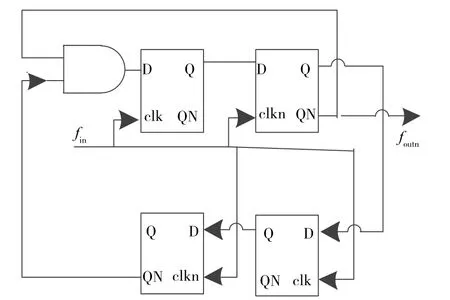

2/3分频器门级的电路拓扑如图1所示。

图1 2/3分频器门级的电路拓扑

从电路拓扑中可以看出,该分频器电路包括4个锁存器和3个逻辑门。其中fin为输入时钟信号,foutn为输出信号,Modin和Pi为分频比控制信号,Modout为模式输出信号。

当Modin=0时,下方的两个锁存器Q端口输出始终为0,/Q信号输出始终为1,此时该分频器的分频比为2,分频器的电路架构可以简化为以下两种形式。

(1)当Modin=1时,如果Pi=0,则左下角锁存器Q端口输出始终为0,/Q信号输出始终为1,此时该分频器的分频比仍为2,分频器的电路架构也可简化图2。

图2 简化后的电路拓扑 (Modin=1,Pi=0)

(2)当Modin=1时,如果Pi=1时,此时电路可简化为图3。

图3 简化后的电路拓扑(Modin=1,Pi=1)

此时,该电路的真值如表1所示。

表1 电路的真值表

表中:D1为左上锁存器的输入;Q1、/Q1为右上锁存器的输出;D2为右下锁存器的输入;Q2、/Q2为左下锁存器的输出。从真值表中可以看出,此时分频器的分频比为3。

因此该电路通过合理的控制可以实现2/3双模工作模式[2]。

2 分频器电路设计

2.1 分频器基本电路结构

高速分频器电路通常采用差分电路,其中基本的锁存器电路结构如图4所示。D、/D为差分数据输入端口;CLK、/CLK为始终差分输入端口;Q、/Q为差分输出端口。

图4 基本锁存器单元

基本的与门电路单元如图5所示。A、/A、B、/B为差分信号输入端口; Q、/Q为与信号差分输出端口[3]。

图5 基本与门单元

2.2 提高分频器工作频率设计

从电路组成中可以看出,分频器的工作频率与锁存器和与门电路工作速度息息相关。锁存器和与门电路工作速度与三极管的增益、电流源电流、电源端电阻等相关,一旦工艺确定,其可以调整的余地有限。本文提高分频器工作频率采取的措施为,在提高锁存器和与门电路工作速度的同时,减少信号在整个电路内的传输时间。具体方法为将门电路嵌入锁存器中减小延迟时间同时考虑电路布局,减弱电路单元间的寄生效应,来提高分频器的最高工作频率。

将门电路嵌入锁存器后的基本电路单元如图6所示[4]。

图6 将门电路嵌入锁存器后的基本电路单元

2.3 分频器低附加相位噪声设计

分频器相位噪声的实质是输出信号过零点不确定,从而造成周期抖动。过零点的变化 ,可以看作是噪声电压对输出信号周期的影响。

如果将时间变化Δt转换为相位可得:

本文设计的分频器电路结构由一对差分三极管、尾电流管、负载电阻构成。三级管的电流噪声只有在其导通时才会叠加在输出电阻上,因此影响输出信号过零点的主要噪声来源为差分输入三极管的电流噪声、尾电流管的电流噪声以及负载电阻的白噪声。

本文主要通过工艺选择、电路设计结构和仿真优化分析3个方面来降低分频器的相位噪声[5]。

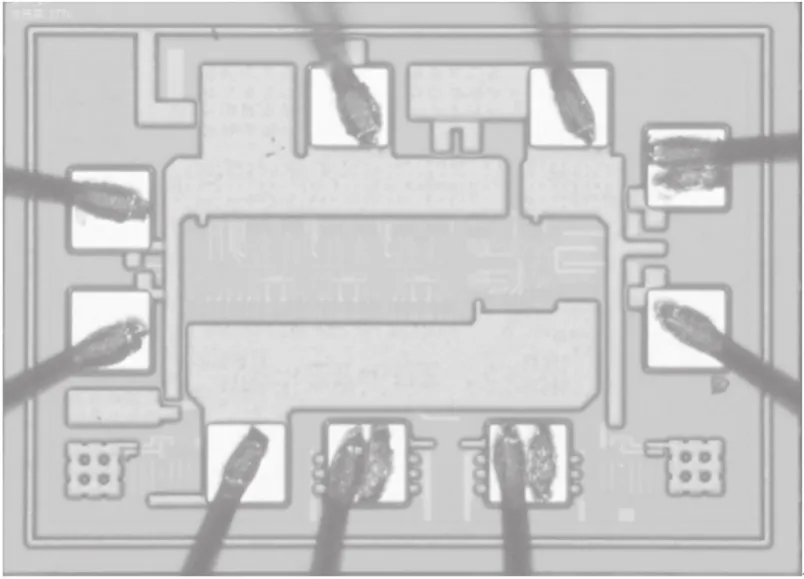

3 产品制作及测试

利用本文提出的改善分频器工作频率和降低附加相位噪声的方法,基于硅基工艺,设计了一款2/3双模分频器,分频器的尺寸为1.1 mm×0.7 mm×0.1 mm,照片如图7所示。

图7 芯片照片

经测试,该分频器的最高工作频率为26 GHz,附加相位噪声为-140 dBc/Hz@1 kHz、-145 dBc/Hz@10 kHz以及-150 dBc/Hz@100 kHz,满足工程应用需求。

4 结 论

本文分析了三阶有源环路滤波器的环路特性。并进行了实际产品制作及测试,测试结果与计算结果完全吻合,验证了环路分析的正确性,对环路参数调整有重要的指导意义。

本文给出了双模分频器的电路架构,并对其工作原理进行了概述,随后提出了一种提高工作频率和改善附加相位噪声的方法,最后基于硅基工艺设计了一款2/3双模分频器,经测试该分频器的最高工作频率为26 GHz,附加相位噪声为-140dBc/Hz@1kHz、-145dBc/Hz@10kHz以及-150dBc/Hz@100kHz,满足工程应用需求,对后续高频、低相噪分频器的设计具有重要的指导意义。