基于0.18 μm CMOS工艺的ZigBee分频器设计

蒋雪琴

(四川信息职业技术学院,四川广元628017)

基于0.18 μm CMOS工艺的ZigBee分频器设计

蒋雪琴

(四川信息职业技术学院,四川广元628017)

为了降低ZigBee分频器的能量消耗,提出一种适用于2.45 GHz频率的超低功率COMS分频器,可以用于2.45 GHz整数分频锁相环频率合成器中,适用于ZigBee标准网络。提出的分频器在吞脉冲分频器的基础上,通过一个简单的数字电路取代吞咽计数器,从而降低了功率消耗和设计复杂性。该分频器的模量可以在481~496之间调整。所有的电路设计都基于0.16 μm的TSMC CMOS技术,使用1.8 V直流电压供电。仿真结果显示,在2.45 GHz ISM频段中4 b分频器的功耗为420 μW,相比之前类似分频器减少了40%。

吞咽分频器;整数分频锁相环;双模量前置分频器;ZigBee

[4-5]中引入了一个新的分频器结构,操作频率高达5 GHz,功率效率为1.79 GHz/MW。在高频整数分频锁相环中实现低功率和高频分频器的常用方法是基于脉冲咽分频器[6]。在传统的脉冲吞咽分频器中,吞咽计数器是一个可加载的计数器,而且有一个相当复杂的结构[7],在双模前置分频器输出时代表实质性的负载,因此浪费了大量的能源,也限制了分频器的工作频率。本文提出一种设计分频器的新方法,通过一个简单的数字电路取代吞咽计数器,与之前相同的作品相比,将分频器的功率消耗降低了40%。在一个整数分频锁相环中,对提出的分频器进行设计和测试,基于2.45 GHz IEEE 802.15.4/ZigBee收发器,参考频率为5 MHz,覆盖了16个可用的信道。

1 整数型吞脉冲分频器

图1显示了基于传统脉冲吞咽分频器的可编程分频器的简单示意图。可以清楚地看到,这种结构有一个双模量(M)前置分频器,一个固定的程序(P)计数器和一个可加载的吞咽(S)计数器。根据模量控制位的逻辑水平,前置分频器有能力用其高频输入除以M+1或者M。程序计数器将前置分频器的输出除以一个固定的程序计数器(P)。最后吞咽分频器也将前置分频器的输出除以吞咽(S)计数器,并且控制前置分频器的模量选择。吞咽计数器由程序计数器重置,每次对程序(P)的输入周期进行计数。

图1 脉冲吞咽分频器

为了解释分频器如何操作,假定前置分频器开始除以M+1,这一过程持续进行直到吞咽计数器达到S的计数,而且前置分频器的模量控制改为除以M。此时,(M+1)×S输入周期已经计数,(P-S)计数被保留在程序计数器中。程序计数器继续计数,直到达到P计数为止,通过M×(P-S)输入周期达到。从上文的解释可以注意到一个完整的周期是通过(M+1)×S+M×(P-S)=M× P+S周期的输入达到。这个方程意味着产品M×P设置需要合成的频带下限和S选择所需的通道[8]。

传统的吞咽分频器有一些不良的特性。其中一个容易注意到的特点是缺乏模块化的概念,除了双模的前置分频器之外,架构还需要两个额外的计数器产生给定的分频率:固定的P计数器和一个单独的可加载的S计数器,它实际上是完全可编程的计数器,由K个可加载的用于K位计数器的位元构成。

在双模前置分频器输出时,S计数器既浪费能源,又增加了电容的负载,因此增加了功耗。图2为提出的分频器。很明显,将P计数器和S计数器合并成整合P&S计数器,它作为一个固定的P计数器运作,并且要检测计数S来控制前置分频器的模数逻辑位。通过使用这种方法消除了吞咽计数器,在双模前置分频器输出时,降低了电容负载,高频分频器的设计也变得更加简单,而且还降低了分频器的功耗。

图2 提出的分频器

由于2 450 MHz频段在ZigBee标准中是普遍未经授权的波段,因此大多数的应用程序都使用这个范围,在2 405~2 480 MHz之间,它由16个频率通道构成,有5 MHz空间。因此分频器需要481~496之间的分频率,以此覆盖所有可用的16个通道。这些数字是通过除以7/8分频双模量前置分频器(M=7),吞咽方程中P=64和33≤S≤48计算得来的。

2 分频器结构设计

2.1 双模前置分频器

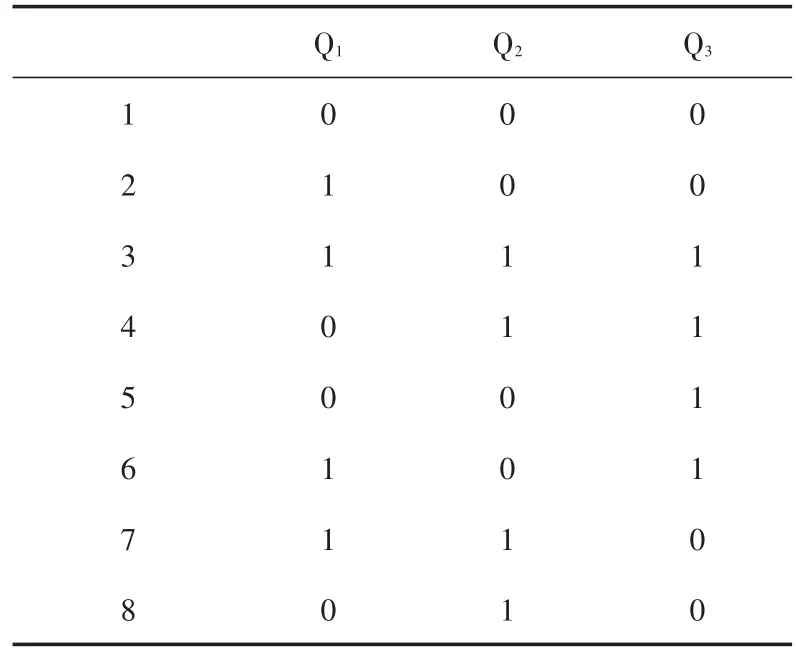

由于这个结构是基于吞咽分频器,因此内部模块的设计类似于吞咽分频器。如前一节中所述,已经使用7/8分频双模量前置分频器,用于这种结构的双模量前置分频器的模块方框图,如图3所示。这个前置分频器由一个除以3/4的双模量前置分频器和一个2分频双模量前置分频器构成。表1给出了双模量前置分频器的操作顺序。当模量位为零时,M1晶体管是关闭的,前置分频器将输入频率除以8。当模量位更改为1时,在状态3下(见表1),Q1的输出由M1~M3重置,Q2Q3=11,而且前置分频器根据表1跳跃到状态4,所以Q1Q2Q3=111的数值被消除了,输入频率除以7。

图3 7/8分频双模量前置分频器

表1 双模量前置分频器的操作顺序

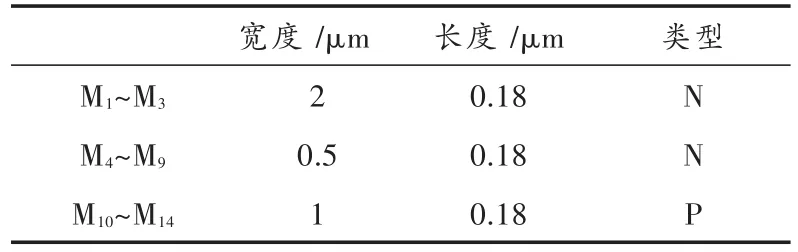

图4显示了传统的TSPC DFF已经应用于双模量前置分频器中。表2列出了用于双模量前置分频器的晶体管大小。

图4 传统的单相计时器(TSPC)D-触发器(DFF)

表2 用于前置分频器的晶体管大小

2.2 集成P&S计数器

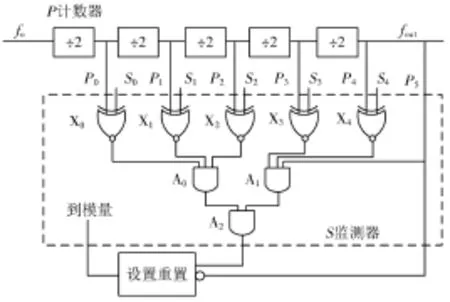

集成P&S计数器的方框图如图5所示。这个方框由一个除以64(P)的计数器和一个数字电路组成,数字电路由XNOR门(X0~X4),AND门(A0~A2)和复位置位触发器(RSFF)构成。数字部分已经取代了在传统计数器中的S计数器,并有责任控制双模量前置分频器的模量位。

图5 提出的集成P&S计数器

表3显示了4个可用输入所用的XNOR块的输出。XNOR门是一个等式块,所以当XNOR的输入相等时(两者都是0或1),XNOR门的输出是逻辑输出。因此,当P计数器的值(P5P4P3P2P1P0)等于预定义的S数值时(1S4S3S2S1S0),RSFF由A2门设置,而当P5改变为0时,RSFF要进行重置(S4~S0位由指定锁相环频率通道的收发机系统定义)。为了获得更多细节,假设P计数器是在初始的状态下{P5P4P3P2P1P0=000000}。当P5=0时,RSFF被重置,双模量前置分频器将输入频率除以8。假设希望锁相环在第6信道工作,就在S4~S0{S4S3S2S1S0= 00110}下载数字6。

导入输入信号,P计数器增加直到P计数器的数值达到预定义的S{P5P4P3P2P1P0=1S4S3S2S1S0}。在P计数器的这个值中,XNOR和P5的输出都是逻辑1,这就导致RSFF将由A2门进行设置。

表3 XNOR门的真值表

在这之后,前置分频器将输入频率除以7,直到P计数器达到它的最大值(111111),下一个数值是{000000}。RSFF由P5重置,前置分频器回到除以8的状态,周期重新开始。在这个周期中,事件的发生类似于传统的脉冲吞咽分频器。因此,对于预定义的S(1S4S3S2S1S0=S)数值,前置分频器将输入频率除以8,而对于剩余的数值(64-S),将输入频率除以7。对于一个完整的周期,得到以下公式:

上文提及到的例子,S=32+6,因此fvco=2 430 MHz,这是ZigBee标准第6个信道的中心频率。

为了提高操作速度,XNOR块已经通过传输门管逻辑实施,TSPC DFF已经执行2分频,类似于前置分频器块所用的DFF。

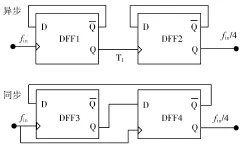

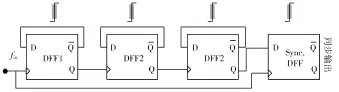

基于DFF的分频器被划分为两组:同步分频器和异步分频器[9]。图6说明了基于DFF的4分频器。在同步分频器中,所有的DFF都是通过主要的输入频率进行工作,而在异步分频器中,下一个DFF的输入频率是前面一个DFF输入频率的一半,信号的频率随着它进入到下一个DFF而减半。低频率导致低功耗,因此,在大分频比率中,异步分频器的功耗要比同步分频器的功耗低得多[10]。

图6 基于DFF的4分频器

异步分频器有个大的缺点,即在DFF中传播定时抖动。在DFF中噪声的存在引起上升边缘(或者下降边缘)的时间随着噪声而变化。

T1是第一个分频器(DFF1)的输出信号时段,T0是振荡器的平均时段,Δt1是噪声存在时第一个分频器的定时抖动。在下一个DFF中,信号的时段延长一倍,第二个DFF(Δt2)的抖动增加了。因此,异步分频器成为一个定时抖动的累加器。对于NDFFs(K=2N)分频的分频器,得到以下公式:

式中:TN是最后一个DFF的时段,K是分频比率,Δttotal是总的定时抖动。图7显示了总的定时抖动(Δttotal)在数字模拟分频器上输出的分布情况。

图7 定时抖动的概率密度分布及累积概率

为了解决这一问题,放置一个同步器DFF作为最后一个DFF[10](图8中的同步器DFF)。这个DFF的存在引起最后一个DFF的上升边缘与主要信号的上升(或者下降)边缘同步。图8显示出在异步分频器中抖动的传播和同步输出。通过使用这个DFF,总的抖动降低到一个DFF的抖动。为了评估同步器DFF的效果,必须考虑振荡器的输出电压:

式中:Vout是振荡器的输出电压,等幅为A;矩形频率为ω0;φ()

t是噪声存在时振荡器的输出相位。如文献[10]计算,分频器的相位误差被系数K转移到输出上。为了分析抖动效果,分频器的相位噪声被认为是一种在环路带宽内的正弦:

其中φdiv是分频器的相位误差振幅。分频器在载体的频率偏移ωm的相位噪声可由如下公式计算得出:

图8 同步器DFF消除的定时抖动

异步分频器有效定时抖动的选择概率为50%。φdiv=(K/4)×Δt×ω0。所以在异步分频器中相位误差的振幅是同步分频器的K/4倍。因此:

3 仿真结果

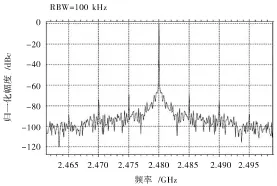

在提出的分频器中,与分频器相关的相位噪声降低了24 dB,因此分频器相关的相位噪声消除了,而且电荷泵的噪声与PLL的相位噪声接近。仿真结果表明-70 dBc(降低了8 dB)接近设计电路中PLL的相位噪声。

提出的分频器已经在适用于2.45 GHz ZigBee标准的锁相环频率合成器中进行过测试。图9显示了压控振荡器的控制电压从第1个到第16个信道的变化,图10描述了在锁定的情况下锁相环在第16个信道的输出频谱。设计分频器的布局如图11所示,大小为36μm× 45μm。

图9 压控振荡器的控制电压从第1个到第16个信道的变化

图10 锁相环在第16个信道的输出频谱

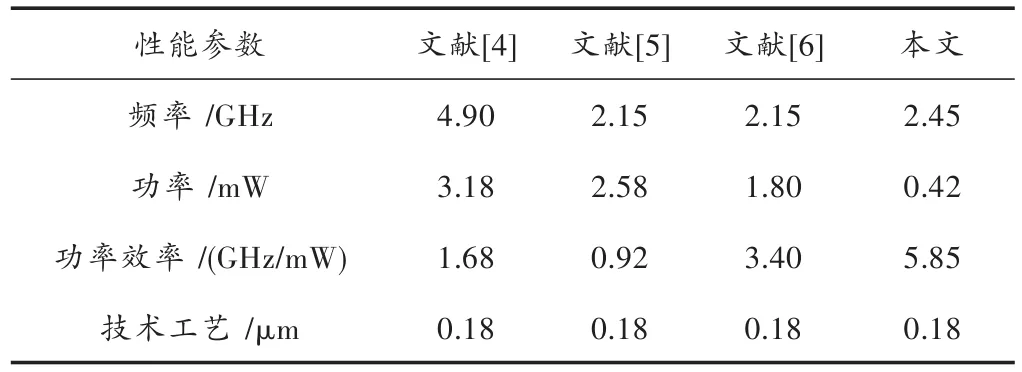

所有的电路都经过Cadence RF Spectre软件的设计和模拟,运用了0.18 μm TSMC CMOS工艺。表4显示了一些实用0.18 μm技术的最新可编程分频器的性能参数以及提出的分频器性能参数的对比。分频器的总功耗是420 μW,由单一的1.8 V直流供电。

图11 提出的分频器布局

表4 提出的方法与以前的方法对比

4 结语

本文提出了一个适用于锁相环频率合成器的超低功率分频器,可在ZigBee 2.45 GHz标准中工作。通过使用一个简单的数字电路,取代在传统的分频器中消耗了大部分能量的吞咽计数器。将一个简单、低功率的7/8分频双模分频器设计为前置分频器,以便降低分频器的总功耗。仿真结果表明,完整的分频器的功耗为420 μW,相比之前类似的分频器减少了40%,提出的分频器面积为36 μm×45 μm。

参考文献

[1]齐骋,王亮,凌朝东,等.基于源耦合逻辑的正交二分频器设计[J].微型机与应用,2012,31(22):26-28.

[2]吉新村.应用于无线传感网射频收发器的CMOS频率综合器研究与实现[D].南京:东南大学,2012.

[3]肖津津,曾昭,黄水龙,等.基于SMIC40nm CMOS工艺的整数分频器[J].电子技术,2013(3):58-61.

[4]CHIEN T H,LIN C S,WEY C L,et al.High-speed and lowpower programmable frequency divider[C]//Proceedings of 2010 IEEE International Symposium on Circuits and Systems. Paris:IEEE,2010:4301-4304.

[5]SHU Haiyong,LI Zhiqun.A 5 GHz programmable frequency divider in 0.18 μm CMOS technology[J].Journal of Semiconductors,2010,31:85-89.

[6]HUANG Shuilong,WANG Zhihua,MA Huainan.A self-tuning,adaptive 1.9 GHz fractional-N/integer frequency synthesizer[J]. Acta Electronica Sinica,2006,34(5):769-773.

[7]刘慧敏.CMOS射频频率合成器的研究及其在ZigBee中的应用[D].天津:南开大学,2011.

[8]杜泽保,杨浩,张海英,等.V波段CMOS注入锁相二分频器设计[J].中国科学院研究生院学报,2012,29(5):681-685.

[9]徐伟,黄乐天,丁召明,等.CMOS全集成低压低功耗锁相环设计概述[J].电子技术应用,2015,41(5):21-24.

[10]郑立博,张长春,郭宇锋,等.0.18 μm CMOS高集成度可编程分频器的设计[J].南京邮电大学学报:自然科学版,2014,34(3):75-79.

Design of ZigBee frequency divider based on 0.18 μm CMOS technology

JIANG Xueqin

(Sichuan Information Technology College,Guangyuan 628017,China)

To reduce the energy consumption of ZigBee frequency divider,an ultra-low power CMOS frequency divider is proposed,which can be used in the frequency synthesizer of 2.45 GHz integer frequency division phase locked loop and ZigBee standard network.Based on the swallow pulse divider,a swallow counter is replaced by a simple digital circuit to reduce the power consumption and design complexity.The modulus of the divider can be adjusted from 481 to 496.All circuits design is based on TSMC CMOS technology of 0.16 μm,in which the circuit is supplied with 1.8 V DC voltage.The simulation results show that the power consumption of the 4 bits divider is 420 μW in 2.45 GHz ISM band,and reduced by 40%in comparison with that of the previous similar frequency divider.

swallow frequency divider;integer frequency division phase locked loop;dual-modulus prescaler;ZigBee

TN926+.23-34

A

1004-373X(2015)23-0071-05

10.16652/j.issn.1004-373x.2015.23.020

0 引言

蒋雪琴(1982—),女,四川简阳人,讲师。研究方向为电子信息技术。

2015-07-29

ZigBee是一项最新研发的无线技术,已经应用于许多商业和研究中。由于其开放的标准(基于IEEE 802.15.4标准)[1],低廉的成本以及低功耗的特点,已经成为一种非常普及的无线连接解决方案[2]。与其他诸如蓝牙和WiFi的无线技术相比,ZigBee适用于低数据率和低功耗的应用程序[3]。应用程序包括家庭和大楼自动化、工业控制、大楼管理系统以及环境监测等。该标准的操作频率[3]为860 MHz,920 MHz和2 450 MHz。

大多数基于ZigBee协议的网络都是由电池供电。减少网络节点的功耗是设计师最突出的挑战之一。在节点中关键的射频功能是频率合成器,尤其是可编程的分频器。分频器由在(或接近)最高射频频率操作的逻辑门构成。由于分频器的复杂性,高操作频率通常会导致高功率损耗。