QuartusⅡ仿真在士官教育电工实验课程中的应用

徐坤玉,王鹏飞

(武警石家庄士官学校 基础部教学实验中心,石家庄 050061)

QuartusⅡ仿真在士官教育电工实验课程中的应用

徐坤玉,王鹏飞

(武警石家庄士官学校 基础部教学实验中心,石家庄 050061)

为进一步探索士官信息化基础教育改革,应用QuartusⅡ软件仿真的方式进行传统实验,通过分析比较应用QuartusⅡ软件仿真实验与目前传统硬件实验的异同,指出了QuartusⅡ软件仿真应用于整个实验过程中的易操作性,从而体现出了将EDA技术应用于基础电工实验课程中的创新性和优越性。

EDA技术;QuartusⅡ软件;软件仿真实验;电工实验课程

0 引言

伴随着集成电路和计算机技术的快速发展,在电子系统设计方面,电子设计自动化(EDA)工具因具有快速、有效、高级的特点,已经成为极其重要的辅助设计工具。EDA工具极大地提升了电子设计的效率以及可操作性,有效地减轻了工作者的劳动强度,并广泛应用于高校电子技术实验教学中[1]。随着信息技术的发展和广泛应用,笔者所在学校非常重视信息化教育,强调实际操作能力,注重发挥士官学员的自主创新能力已经成为基础实验课程最主要的教学目标。对于电子技术课程实验,特别是数字设计课程实验来讲,应用EDA技术是非常有必要的。借助于EDA开发系统,学员只需要一台计算机就可以轻松完成所有的实验任务,并且可以根据自己的设计开展各种实验,充分发挥学员在实操课中的主动性。

1 QuartusⅡ集成开发软件

Quartus II是Altera公司的综合性PLD/FPGA开发软件,该软件包含大量的逻辑功能模块,便于原理图输入时直接引用[2]。基于QuartusⅡ进行EDA设计开发的流程分为三步,分别是:

(1)设计输入。包括原理图输入、文本输入、AHDL输入、模块输入、第三方EDA工具产生的文件以及混合使用以上几种设计输入方法进行设计。本文采用原理图输入方式建立实验电路连接图。

(2)编译。首先,依据设计需求选择合适的编译方式和策略,如元件的选择、逻辑综合方式的选择等。其次,依据选择的方式和策略对项目进行网表提取、逻辑综合、器件适配,并产生报告文件、延时信息文件和编程文件,用来供分析仿真和编程使用[3]。

(3)仿真。包括功能仿真、时序仿真和定时分析,该步骤是应用QuartusⅡ的仿真功能检验设计项目的逻辑功能以及时序关系的正确性。本文运用功能仿真来体现实验的结果。

2 实验仿真及结果分析

本文以基础电工实验课程中的一次实验课——计数器的逻辑功能测试及其应用为例,利用QuartusⅡ软件仿真实验全过程,通过计算机显示屏直观地展示出所有实验步骤和相应实验结果。本实验是电工基础实验数电部分的内容,实验目的是使学员通过掌握74192芯片(同步十进制可逆计数器)的逻辑功能和使用方法。在传统实验中,实验仪器包括:数电模电实验箱一台、74192集成芯片2个、连接导线20根等诸多仪器设备。在QuartusⅡ软件仿真环境下的实验,只需要一台计算机即可。下面是在QuartusⅡ软件仿真环境下进行实验的过程与结果。

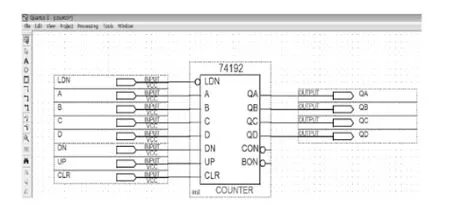

2.1 计数器清零功能验证

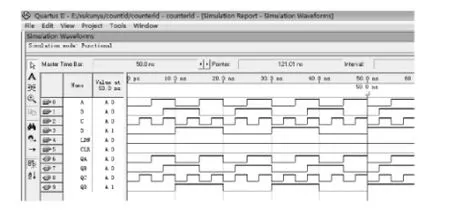

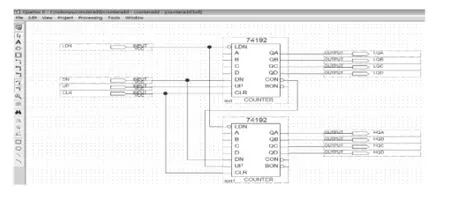

图1为QuartusⅡ软件仿真环境下原理图输入界面,A、B、C、D为计数器的输入端,QA、QB、QC、QD为计数器的输出端,LDN为置数端,UP为加计数端,DN为减计数端,CLR为清零端,CON为进位端,BON为借位端。除进位端CON,借位端BON不需要连接INPUT输入接口外,其他端口均需要与相应的INPUT/OUTPUT接口连接。

图1 74192芯片清零功能电路连接图

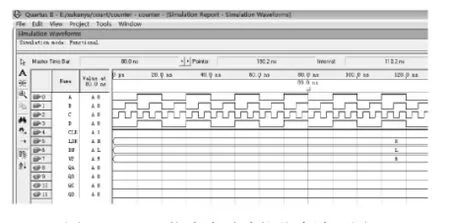

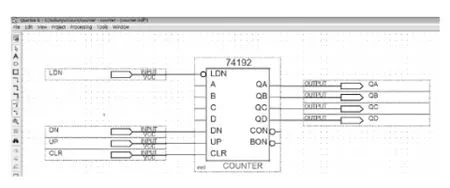

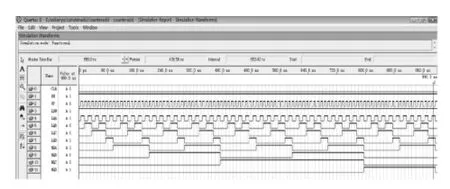

图2 74192芯片清零功能仿真波形图

图2为功能仿真结果。在图2中,将清零端CLR置为1,其他7个输入为任意态,此时输出端QA、QB、QC、QD输出结果均为0,完成清零功能验证。这时输入任意状态不受实验箱内提供的少数高低电平限制,可以任意取值,实验结果也一目了然。

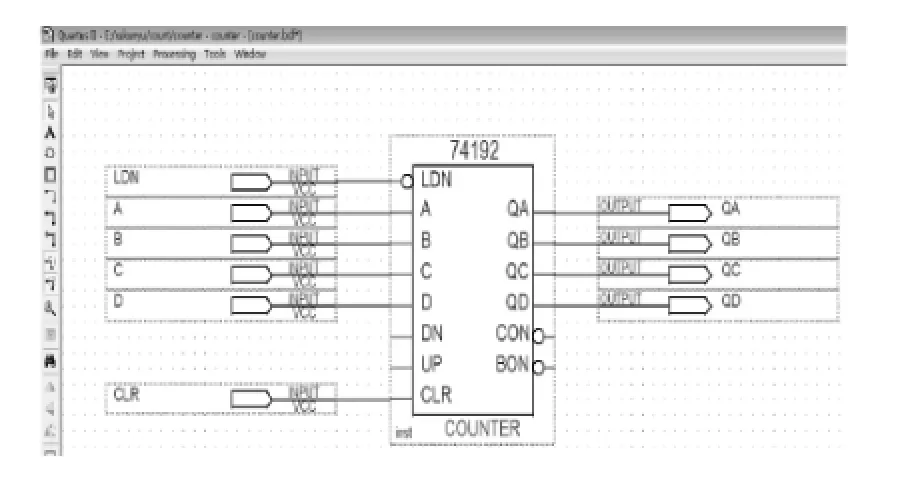

2.2 计数器置数功能验证

与清零功能验证类似,图3为验证74192芯片置数功能的电路连接图。除去加计数端UP、减计数端DN、进位端CON、借位端BON的输入端口不添加INPUT接口外,其他端口都接入相应的INPUT/OUTPUT接口。在传统实验中,需要记住芯片的管脚对应的位置进行电路连线、拆线,操作起来十分复杂,容易出错。

图3 74192芯片置数功能电路连接图

图4为置数功能仿真结果。在图4中,清零端CLR、置数端LDN均置为0,输入端A、B、C、D为任意一组二进制数,此时输出端QA、QB、QC、QD输出结果为相同二进制数。如图4所示,在50ns处,输入端D、C、B、A为0101,输出端QD、QC、QB、QA即为0101。

图4 74192芯片置数功能仿真波形图

2.3 计数器加、减计数功能验证

图5为计数器加、减计数两个功能的电路连接图,除去输入端A、B、C、D和进位端CON、借位端BON不接INPUT输入接口,其他端口均需要接入相应INPUT/OUTPUT接口。在传统实验中,加、减计数两个端口非常容易混淆,但在QuartusⅡ软件仿真实验中却可以有效避免。

图5 74192芯片加、减计数功能电路连接图

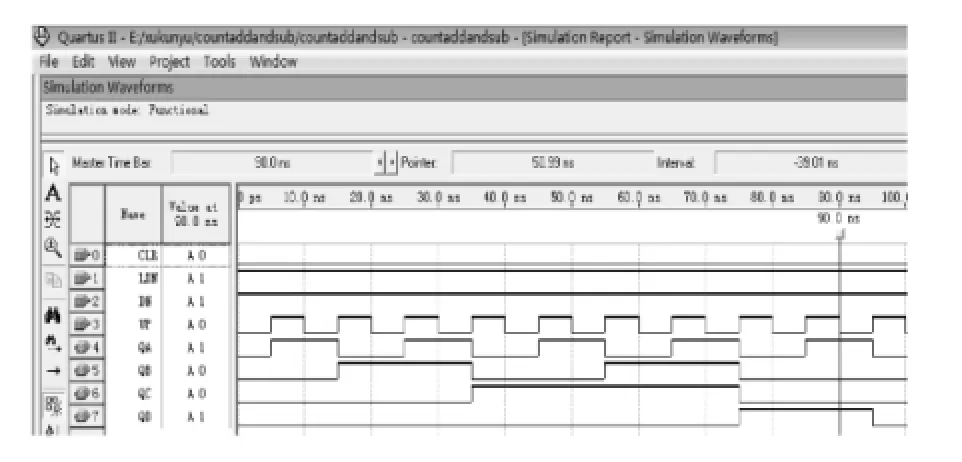

图6为74192芯片加计数功能仿真结果。在图6中,清零端CLR为0,置数端LDN为1,减计数端DN为1,加计数端UP输入连续脉冲信号,脉冲信号的上升沿到来时,输出A、B、C、D就会改变,从0000到1001,也就是十进制的0到9,实现了加计数的功能。

图6 74192芯片加计数功能仿真波形图

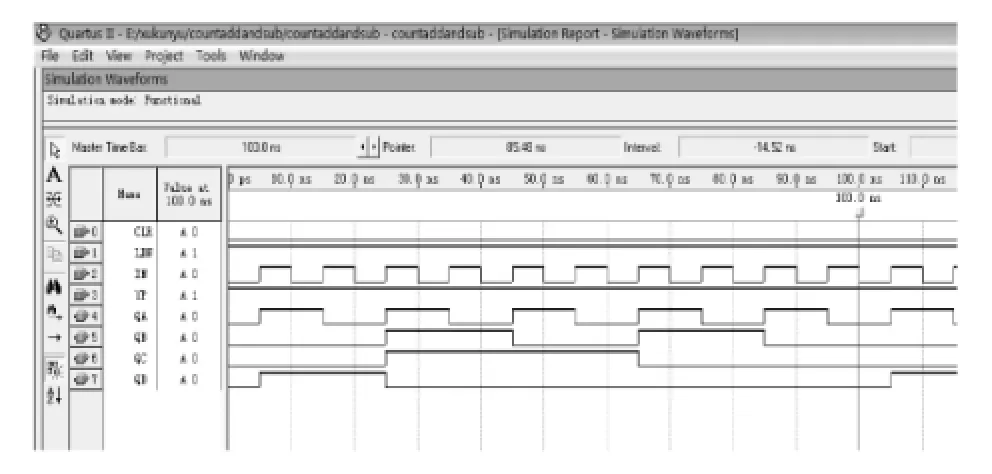

与加计数类似,图7为74192芯片减计数功能仿真结果。在图7中,清零端CLR为0,置数端LDN为1,加计数端UP为1,减计数端DN输入连续脉冲信号,脉冲信号的上升沿到来时,输出D、C、B、A就会改变,从1001到0000,也就是十进制的9到0,实现了减计数的功能。

图7 74192芯片减计数功能仿真波形图

2.4 两个计数器累加功能验证

在图8中,用两片74192芯片组成两位十进制加法计数器,低位74192芯片的进位端CON连接高位74192芯片的加计数端,其他的输入端、输出端与相应INPUT/OUTPUT接口相接即可。在传统实验中,需要在实验箱中准备两个芯片,而且连接导线数量会增加一倍,要记忆更多的芯片管脚数据,正确连接电路需要十分仔细。

图8 74192芯片两级递加功能电路连接图

图9 74192芯片两级递加功能仿真波形图

图9为级联芯片实现两位数递加的功能仿真。从图9中,可以清楚的看出8个输出端HQD、HQC、HQB、HQA、LQD、LQC、LQB、LQA从00000000到10011001的变化,也就是十进制00到99的加计数过程。在传统实验中,要观察整个计数过程,需要拨动99次脉冲源,才可以观察0到99的递加计数,通常我们只拨动几次脉冲源,观察两位数中间递加过程,实验观察不完整,某些过程中的错误数据无法得到。更甚之,在传统实验中,到三位数字加计数乃至多位数字加计数时,需要增加芯片量,连接导线数量会成倍增长,电路连接更是错综复杂。而在QuartusⅡ软件仿真环境下,我们只需要在原理图中加入多个74192芯片模块即可实现。

3 结语

通过以上分析可以看出,在QuartusⅡ软件仿真环境下,实验的操作过程得到简化,实验的可操作性得到增强,实验的灵活性、创新性得到提高。在QuartusⅡ软件仿真实验过程中,学员可以很容易地实现、修改和完善自己对扩展性实验内容的设计,进而提高自身的设计创新能力和计算机应用能力。

[1]张彩珍.EDA技术及实践[M].成都:西南交通大学出版社,2011.

[2]徐志军,王金明,尹廷辉.EDA技术与VHDL设计[M].北京:电子工业出版社,2008.

[3]潘松,黄继业.EDA技术实用教程(第3版)[M].北京:科学出版社,2005.

Quartus Ⅱ Simulation Applications in Electrical Experiments Curriculumof Sergeant Education

XU Kun-yu,WANG Peng-fei

(Basic Experimental Teaching Center,Shijiazhuang Armed Police Sergeant School,Shijiazhuang 050061,China)

Tofurther explorethe basic education reformof sergeant information,traditional experiment is applied bythe way of QuartusⅡsoftware simulation.By analysis and comparison of applications QuartusⅡsoftware simulation experiments and thetraditional hardware experiments,the easy maneuverability of software simulation appliedtothe entire experimental process is pointed out.Andthe innovation and superiority are reflected bythe EDAtechnology inthe curriculumof basic electrical experiments.

EDAtechnology;QuartusⅡSoftware;software simulation;counter

TP391.7

A

1673-2022(2014)04-0058-03

2014-07-16

徐坤玉(1986-),女,河北石家庄人,助教,硕士,研究方向为电子与通信工程;王鹏飞(1987-),男,河北保定人,助教,研究方向为通信指挥。