CQFN封装可靠性研究

蒋长顺,敖国军,张嘉欣,张顺亮

(无锡中微高科电子有限公司,江苏 无锡 214035)

1 引言

近年来,CQFN封装(陶瓷方形扁平无引脚封装)由于具有良好的电特性和热性能、体积小、重量轻等特点,其应用正在快速增长,CQFN封装与CLCC相似,本文将对其可靠性进行探讨。

2 CQFN结构及特点

CQFN是一种无引脚封装,呈正方形或矩形,最大封装尺寸一般不超过9 mm×9 mm,陶瓷体底部中心位置有一个大面积裸露热沉焊盘用来导热或接地,大焊盘的四周为实现电气连接的导电焊盘。因CQFN封装没有传统的引线结构,内部焊盘与外导电焊盘之间的导电路径短,自感系数和布线电阻很低,所以具有卓越的电性能。此外,热沉焊盘直接焊接在电路板上,有利于热量散发。由于体积小、重量轻、杰出的电性能和热性能,该封装特别适用于对尺寸、重量和性能都有要求的应用,所以非常适合应用在军用和高可靠领域中高频、高速LSI芯片封装中。CQFN封装典型结构如图1所示。

图1 CQFN典型结构

3 CQFN外壳制造问题

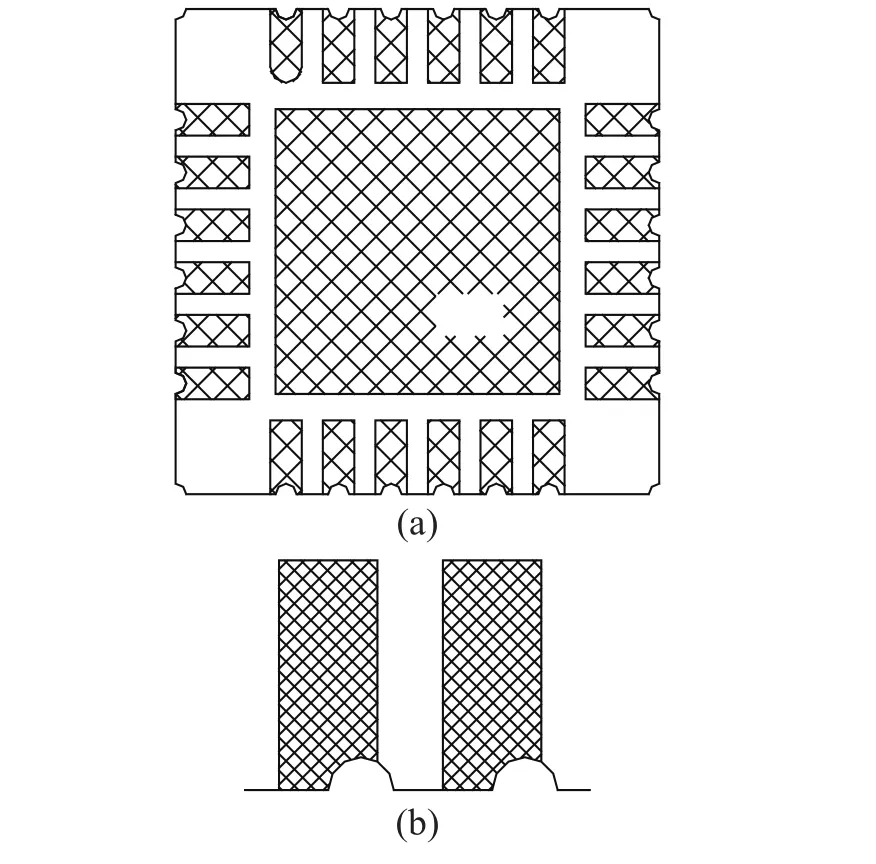

对于细节距的CQFN陶瓷外壳,外焊盘导电连接方式有两种,一种为外焊盘引出方式采用通孔与内焊盘相连,另一种为通过侧面的镀金凹槽相连。图2为通孔连接方式,图3为侧面城堡式镀金凹槽相连方式。

图2 焊盘通孔连接

图3 焊盘侧面城堡式镀金凹槽

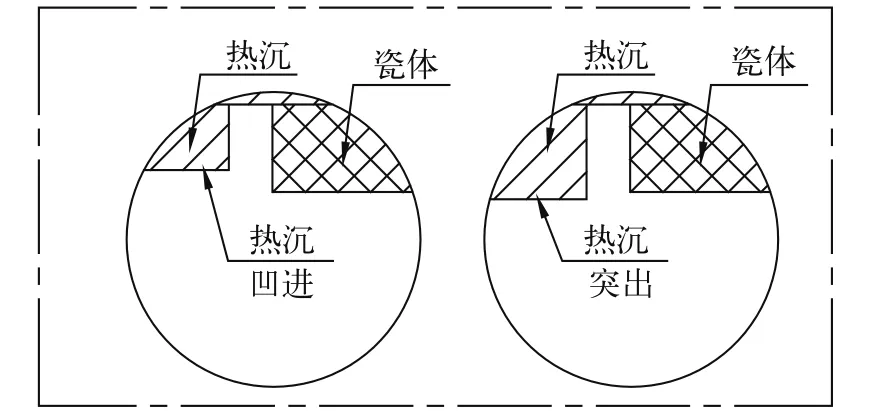

3.1 热沉装配共面度

CQFN中间的热沉焊盘一般为钨铜或钼铜金属材料,镶嵌在陶瓷底部中间位置,并与芯腔相连通,通常起到接地或散热的作用,利于高频器件有效地降低噪声。外壳制造装配热沉后,热沉底面与陶瓷底面共面度较难控制,会出现图4所示的热沉比陶瓷面突出或凹进的情形,不能保证装配后的共面性,会增加组装焊接质量问题。

3.2 焊盘连接问题

CQFN的特点是无引脚,在陶瓷封装体四周的引脚处可采用具有城堡式的镀金凹槽与底部焊盘连接,如图5所示,然后封装体焊盘直接焊接到基板的焊盘上。随着高频和小型化的需求越来越多,要求CQFN的引脚间距越来越小,当节距减小到0.5 mm或更小时,侧面金属化镀金凹槽加工将非常困难,凹槽对准控制难度较大,会出现如图5(b)所示的偏离焊盘、落在焊区外面的情况,会产生连接可靠性问题。

图4 CQFN底部热沉

图5 CQFN焊盘凹槽偏离

对于焊盘与内部连接采用通孔式互连结构,因通孔直接落在焊盘上,若制造时通孔在表面镀金前没有处理好,镀金后焊盘表面易出现十几微米的凸起,如图6所示,包装后运输或封装工艺过程中底部焊盘上镀金层易划伤,外观检验不合格。

4 板级组装中的可靠性

由于CQFN器件封装是无引脚焊盘结构,不像CQFP或CSOP等引脚封装结构,焊接过程中需要中间热沉焊盘和四周I/O焊盘与PCB板实现可靠焊接,焊盘在封装体的底部且不可见,焊接后常常出现各种可靠性问题,主要有热应力失效、引脚间的桥连、焊点开路、焊点空洞等,并会导致焊点检测和返修困难。

图6 焊盘上通孔突起

4.1 热应力失效

CQFN器件组装的PCB板一般是聚合物材料,外壳为陶瓷材料,陶瓷外壳与PCB板材料热膨胀系数(CTE)不匹配及在焊接过程或使用过程存在热循环时的温度变化,使外壳和PCB板及界面承受不同的热应力。热应力的存在会使PCB翘曲,在焊点部位处产生的应力不能得到缓解,导致组装质量可靠性问题或产品失效问题。根据Sun[1]等人的研究:器件尺寸为8 mm×8 mm、芯片尺寸为4 mm×4 mm的QFN组装器件在-40~+125℃升降温、保温分别为15 min的热循环条件下的疲劳寿命为2324次热循环。再根据Tong[2]等人的研究成果折合各种因素对QFN组装器件焊点热疲劳寿命的影响,可换算得在-55~+125 ℃升降温、保温分别为10 min的条件下QFN器件尺寸为8 min×8 min、芯片尺寸为5 mm×5 mm时的热疲劳寿命约为2002次。

4.2 焊点桥连、开路、空洞

CQFN为无引脚焊盘结构,焊盘间距较小,且中间热沉焊盘共面度较差,局部过多的焊料会导致相邻的焊点之间易形成焊接桥连。当热沉焊盘面呈现凹进情形,焊料量不足且印刷不均匀,热沉焊接点会出现焊点空洞,影响器件散热性能。当热沉焊盘比陶瓷底面突出时,四周导电焊盘上焊料偏少时,将会出现部分导电焊盘没有形成焊接、造成焊点开路的问题。

4.3 焊点的检测困难

由于CQFN的焊点在封装体的下方,对CQFN焊点少锡和开路无法检测,只能依靠外部的焊点情况加以判断,而且没有CQFN焊点侧面部分缺陷的断定标准,仅根据生产后的测试来判断焊接的好坏。

4.4 器件返修难度大

对CQFN的返修,因焊点完全处在器件封装的底部,桥接、开路、锡球等任何缺陷都需要将元件移开。CQFN体积小、重量轻、且它们又是被使用在高密度的装配板上,使得返修的难度增加。

5 总结

CQFN封装是一种新型封装,底部中间热沉焊盘装配和四周功能焊盘加工是关键,当节距越来越小时,无论是设计、工艺还是检测返修等方面都还需要做更深入的研究,以满足高可靠、小尺寸和高频封装的要求。

[1]Sun, v’Zhu W H,Danny R,et al. Study on the board—level SMT assembly and solder joint reliability of different QFN packages,thermal,mechanicaland multi—physics simulation experiments in microelectronics andmicro—systems[C]. TMMPSEMMS Eurosime 2007 International Conference, London,UK:IEEE, 2007. l-6.

[2]Tong Y Hun S N. Daniel Comprehensive board level solder joint reliability modeling and testing of QFN and Power QFN packages[J]. M icroelectron Reliab, 2003,143:l329-l338.