MEMS加速计的SOIC封装技术研究

李 辉,廖巨华,须自明

(1.飞思卡尔半导体中国研发中心苏州分部,江苏 苏州 215011;2.江苏物联网研究发展中心教育培训中心,江苏 无锡 214000;3.中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

MEMS(微机电系统)是集微型传感器、微型执行器、信号处理和控制电路等于一体的微型器件或系统。它能够将物理信号转换为电学信号或将电学信号转换为物理信号,实现从信号的取样、处理到执行的整体集成。它是微电子学、材料学、力学、化学、传感器、自动控制等多学科交叉的产物。MEMS传感器有着广泛的应用,其中MEMS加速计作为重力感应传感器长期用于工业控制。近年来,MEMS加速计被进一步应用到了消费电子中,如手机、笔记本电脑、游戏控制器等。MEMS加速计的制造需要经过两种不同的流程——传感器制成和封装流程,虽然MEMS封装的基本技术是从微电子封装发展而来的,但是由于MEMS的特殊性和复杂性,其封装与微电子封装有着很大区别。对于传统芯片来讲,封装的功能是对芯片和引线等内部结构提供支撑并保护,使之不受外部环境的接触和腐蚀破坏;而对于MEMS封装,除了要具备以上功能外,MEMS器件还要与测试环境之间形成一个接触界面并获取非电信号,而外部环境的复杂性对灵敏度很高的MEMS敏感元件来讲都是具有破坏性的,例如机械力(应力、摆动和冲击等) 、化学反应(气体、湿度和腐蚀介质等) 、物理变化(温度、压力和加速度等)都会干扰甚至损坏MEMS内部的微机械或者微电子芯片。严苛而复杂的要求使得封装占到了MEMS制造成本的50%以上[1]。MEMS加速计产生的任何失真,如达到过度的封装压力或振动,都会导致在重力感应算法中得到错误信号。重力感应器必须响应对应的力量,同时隔离设备所在环境的震动反应。因此传感器的力学特征是非常重要的考虑因素。在一些工业应用中,振动信号的频率可以很高,如果封装中的固有频率与高能量输入信号的频率相近,传感器的封装输出信号将会失真,甚至会使传感器受到物理损伤。

为了解决共振导致的封装问题,通常会采用罐封的方式,并使用了硬固晶胶。但由于使用硬固晶材料而造成的芯片断裂,会导致PPM性能大幅降低。本文所研究的SOIC封装的MEMS加速计是通过在硅基片上进行表面微机械加工制作的,它比同等的DIP封装减少约30%~50%的空间,厚度方面减少约70%,其中ASIC(专用集成电路)芯片和感应单元并排放置,经过实验测试,得到了工艺和材料对芯片断裂的影响因子,并提供了对这一问题的更好的解决方案。

2 MEMS加速计的SOIC封装技术研究

2.1 SOIC封装技术及故障分析

2.1.1 SOIC封装

小外形集成电路封装(Small Outline Integrated Circuit Package,SOIC)的外引线数不超过28条,一般有宽体和窄体两种封装形式。其中具有翼形短引线者称为SOL器件,具有J型短引线者称为SOJ器件。SOIC是表面贴装集成电路封装形式中的一种,与其对应的DIP(双列直插式)封装有相同的插脚引线。对这类封装的命名约定是在SOIC或SO后面加引脚数。例如,14pin的4011的封装会被命名为SOIC-14或SO-14。SOIC实际上至少参考了两个不同的封装标准。EIAJ标准中SOIC的宽度大约为5.3 mm,而JEDE标准中SOIC的宽度大约为3.8 mm[2]。相对来说,EIAJ封装尺寸更厚,且稍微更长一点,在其他方面封装尺寸是相同的。SOIC封装比DIP封装更短而且更窄,对于SOIC-14来说,两侧引脚距离大约为6 mm,且封装体宽为3.9 mm。这些尺寸根据不同的SOIC封装会略有不同。这种封装两侧有翼型引脚,并且两个引脚间距为1.27 mm。

图1 SOIC封装图

图1展示了18引线SOIC封装的成品封装俯视图及其加速计的横切面。封装内有一个传感器芯片,传感器芯片与一个外罩粘合在一起,一部分外罩延伸至靠近焊线垫的基片上。ASIC和感应单元并排放置在一起,芯片被连接到铜引线框架上。在进行超模处理前,使用极低模量的有机硅凝胶覆盖在整个感应单元上。

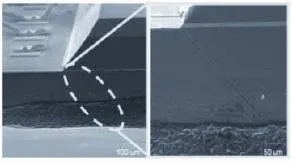

在应用领域,在振动环境中要求封装的固有频率要大于20 kHz,从而避免传感器产生共振的相关问题。为了满足这种要求,采用高模量环氧固晶胶D替换通常的4点软固晶胶A,但是产生了低PPM性能问题,测试发现感应单元的基片芯片出现破裂[3]。如图2所示,裂纹分布于整个有源器件。断面分析显示,裂纹从感应单元基片的顶部开始,沿着基片、玻璃熔块和外罩之间的接触面延伸。裂纹通常是从切割边开始,一些部件只有一个断裂起点,而其他的部件有多个断裂起点。因此需要研究的是引起感应单元芯片断裂的原因,并且是否可以重新设计封装,使其更加坚固可靠。

在故障分析和封装重新设计时本文采用了有限元分析方法。对于暴露于外部环境期间的芯片的应力和断裂风险,采用了两种方法来评估,一种方法是常规的应力分析,另一种是基于断裂力学分析。需要分析的阶段包括外罩晶圆与感应单元基片晶圆间的粘合、感应单元与引线架的连接、引线粘结、超模压、回流焊接和热循环。

图2 感应单元基片上的裂纹图

2.1.2 常规应力分析与断裂力学分析

常规应力分析用于确定不同封装阶段高应力存在的位置。因为外罩晶圆与湿法腐蚀工艺存在一个约54°的角度,因此存在几何不对称性以及一个应力奇异性[4]。这一区域的应力量级对网状敏感,并且会随着网状结构的加密而升高,但是应力分布是有效的。高应力位置区域与观察到的断裂起始位置正好是重叠的。

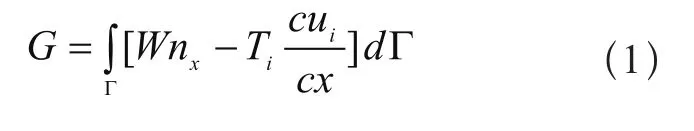

硅片的机械完整性主要取决于它所经历的工艺处理技术。这些工艺处理包括晶片磨薄、表面处理工艺。在进行这些工艺加工时,芯片表面或边缘可能会存在缺陷。如果出现缺陷的位置正好在应力奇异性区域,那么芯片在后续的封装过程和鉴定检测期就容易产生可靠性的问题。在断裂力学分析中,是以假设基片的关键位置已经存在缺陷为前提的。假设裂纹尺寸大约为芯片厚度的1/300,应变能释放率G是指促使裂纹扩展的能量,其计算公式为:

其中,Γ为围绕裂纹尖端的任意路径,W指应变能,Ti是牵引向量;ui是位移向量,nx是Γ上的外向单位法向量的x部分。

图3显示了在进行晶圆粘合期间裂纹扩展的能量。可以看出,对于当前使用的固晶材料D,回流焊接是导致扩展裂纹的最主要工艺。实验使用了固晶胶A设计,没有出现裂纹。从图3可以看出,与使用固晶D相比,使用固晶A时的裂纹扩展的可能性非常低。然而,当封装安装在板卡上时,固晶胶A会引起共振问题。因此,要解决这个问题,在选择合适的固晶胶的同时,必须确保芯片不会出现裂纹且不会引起共振。

图3 每个封装工艺产生的裂纹扩展能量

因为固晶材料会引起芯片的裂纹,因此需要对不同材料进行评估。最初使用的固晶A在7 kHz的频率下会引起感应单元出现共振,这会导致信号失真故障。之后用固晶胶D代替了固晶胶A,固晶胶D的共振频率为400 kHz,就不会引起信号失真。然而,固晶胶D会对已经存在裂纹的芯片产生影响。因此,需要根据共振频率和刚性寻找一种适用的固晶材料。

2.2 固晶材料的研究

本文的MEMS加速计采用了活动基板和固定基板并存的结构。一旦感应单元的频率达到其阈值,MEMS中板就会以机械方式碰撞制动装置,防止碰到感应板的顶部和底部,从而避免引起静摩擦和短路。加速计活动过程会使MEMS器件出现位移,对顶板和底板的制动装置产生不对称的作用力,这会使高加速输入信号出现输出失真。在固晶共振频率下,信号失真会数倍增加[5]。

表1列出了各种固晶材料的属性,并针对给定固晶胶和产生的封装共振频率进行了分析。这些材料分属两种特殊类别。硬固晶胶如固晶胶D满足封装共振条件,但是会引起芯片裂纹。软固晶胶如固晶胶A不会引起芯片裂纹,但是封装不符合共振要求。

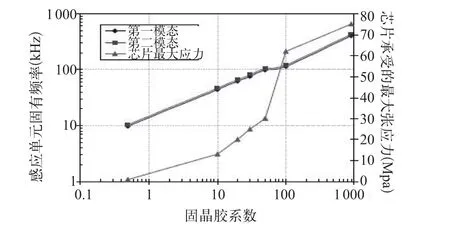

针对以上材料的不足,需要研究理想的固晶材料的属性的范围,以及对封装共振频率和芯片应力的影响。图4给出了根据固晶模量计算的感应单元的固有频率,以及感应单元基片承受的相应的最大张应力。

从图4可以看出,模量接近10的固晶材料具有较低的芯片应力,并且满足了共振频率要求。为了确保采用新固晶胶的芯片的共振性能足够满足上述要求,我们对材料模量随温度的变化进行了测量,同时进行了动态力学分析(DMA),对测试样本进行了一定处理,将材料放到一个扁平的预成型的腔中进行固化处理,然后测试样本随温度的变化数据。图5显示了材料的模量。

表1 材料特性和各种固晶的固有频率

图4 根据固晶模量计算得出的感应单元基片的最大张应力和封装共振频率

图5 固晶胶E的存储模量

固晶E的固有频率是大于20 kHz的,此外,图3显示了固晶E的裂纹扩展能量与固晶A相似,因此产生芯片断裂问题的概率较小。因此,固晶胶E可以替换固晶胶D,因为它非常柔韧,不会使芯片断裂,同时也具有足够的硬度,容易满足共振的要求。对这种新的固晶材料进行鉴定检测和试封装后发现,整个测试样本中没有出现任何芯片断裂。

3 总结

经过以上实验分析,针对MEMS加速计的SOIC封装的完整工艺流程进行了评估以了解造成低ppm水平芯片断裂的裂纹扩展和倾向,找出了具有危害性的关键工序。引起芯片断裂的主要参数是感应单元固晶胶的硬度。目前使用的固晶胶D非常容易使感应单元基片芯片出现断裂。通过反向工程确定了可以同时满足感应单元固有频率和封装可靠性要求的固晶材料。采用固晶胶E后,MEMS加速计的SOIC封装呈现出更加强韧的特性。这对于MEMS传感器特殊封装技术的研究有着借鉴意义,对降低MEMS传感器制造成本、扩大应用领域、推进传感器的快速发展有着现实意义。

[1]蔡梅妮,林友玲,车录锋. 用于器件级真空封装的MEMS加速度传感器的设计与制作[J]. 传感器与微系统,2012,12.

[2]Hsu, T R. MEMS Packaging[M]. T R. Hsu, Institute of Electrical Engineers, United Kingdom, 2004.

[3]Hsu, T R. MEMS and Microsystems Design and Manufacture[M]. McGraw-Hill, 2002.

[4]Tai-Ran Hsu. RELIABILITY IN MEMS PACKAGING[C].44th International Reliability Physics Symposium, San Jose, CA, March 2006. 26-30.

[5]MEMS Reliability Newsletter on MEMS Fatigue[EB/OL].Exponent, 2001,1(1). www.exponent.com/practices/MEMS/MEMS v1 1.pdf.