基于SOI工艺下600V LDNMOS的设计与分析

黄世震,翁坤

(福州大学福建省微电子集成电路重点实验室,福建福州 350002)

随着超大规模集成电路特征尺寸逐步缩小到亚100 nm范围,在材料技术、器件理论、器件结构技术以及制作工艺等方面出现了一系列新的问题,使得亚100 nm硅集成电路的功耗、可靠性以及电路的性价比受到很大的影响[1].一种新型的能够用于纳米级半导体器件技术——绝缘层上硅技术(SOI)因其独特的介质隔离结构[2]使得SOI材料比体硅技术更具优势,其寄生电容小、集成密度高、速度快、工艺简单、沟道效应小[3],特别适合亚微米、深亚微米器件[4].针对体硅高压器件,2010年华润上华在国内推出第二代硅基700 V BCD工艺生产出700 V耐压LDMOS器件.由于纵向耐压的限制,目前600 V以上实用化SOI高压器件在国内几乎为空白.本研究基于0.5 μm 600 V SOI工艺对LDNMOS器件进行设计与分析.

1 基本理论

为了增大器件的工作电压,设计器件结构时在漂移区加入一个矩形槽氧,这种结构对提高SOI-LDNMOS的击穿电压有显著效果.矩形槽氧的引入能增大载流子输运的路径,相当于增大了漂移区长度,从而在不改变其他参数的情况下而使器件更易于耗尽[5-6],同时缩小了版图尺寸.另外,槽氧层能够减弱场板边缘下面硅层中的电场强度,使器件不易在此处提前被击穿,从而提高器件整体的击穿电压.

传统LDMOS漂移区采用均匀掺杂技术来实现,薄的硅膜可以实现高的纵向耐压,但是随着硅薄膜厚度的减小,漂移区均匀掺杂的常规SOI结构,其击穿电压很快出现在器件横向.所以,对于高压LDMOS,就需要对漂移区进行改进.本文中所涉及的LDNMOS,在工艺上通过渐变掺杂技术(VLD)来获得掺杂浓度逐步变化的横向漂移区.理论和实验均已证明,这种结构使得漂移区表面的横向电场分布相对于普通器件趋于平坦,使得器件的击穿电压达到最大值.同时有效消除了kink效应并增大饱和电流,降低了导通电阻[7].

2 器件结构设计

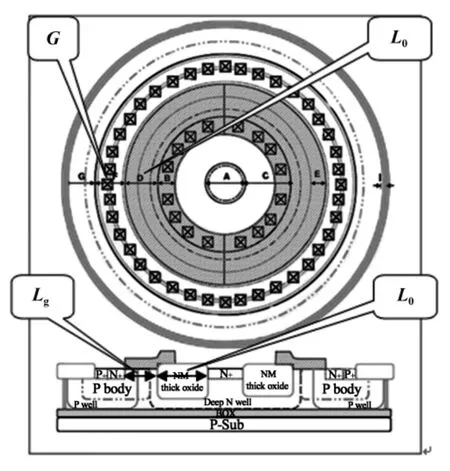

DMOS从结构上分为LDMOS(横向)和VDMOS(纵向)两种[8],VDMOS是竖直方向从外延层的背面将漏端引出,同时厚的外延层承受漏端的高电压.LDMOS则是一种非对称结构,在沟道与漏端之间增加一个横向掺杂漂移区,使高电压集中在这一区域.图1为SOI 600V LDNMOS的结构示意图.图中BOX,Deep N WELL,NM thick oxide分别表示埋氧层、横向漂移区和槽氧层.在漏端通过线性渐变掺杂技术[9]引入漂移区,即掺杂浓度沿漂移区长度方向由沟道区向漏区方向线性变化并逐渐增大.这种方法能够调节器件表面横向电场分布,以同时获得较高的纵向击穿电压和横向击穿电压.引入槽氧层的结构能够使器件更易耗尽从而提高整个器件的耐压.

在所设计的器件结构中(图1,上图为平面图,下图为横截图),整体结构呈环形,中间为漏端,两边为源端,每一层Layer的含义如表1所示.其中:沟道长度Lg为4.5 μm,氧化槽长度L为50 μm,氧化槽厚度为500 nm,栅长G为8 μm.中间的N+区域(A)作为器件的漏端,两边的N+区域作为器件的源端,漂移区处于槽氧层与埋氧层之间,在栅极下方的P-body处形成沟道,当栅极gate加正向电压达到一定值后,器件开始工作.

图1 SOI 600 V LDNMOS的结构示意图Fig.1 Structure diagram of SOI 600 V LDNMOS

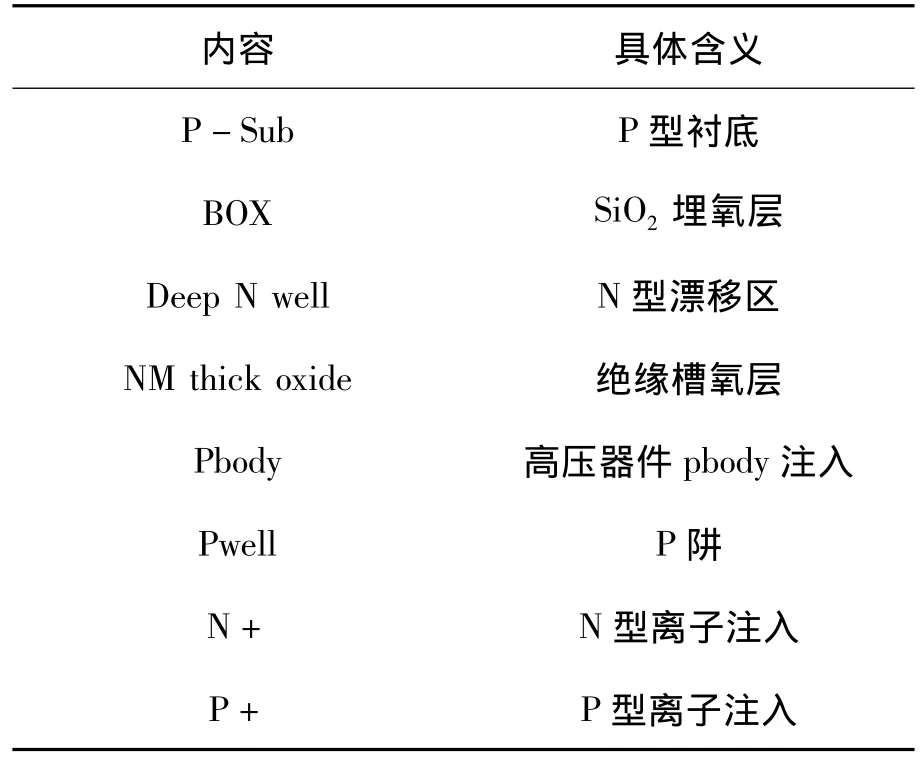

表1 Layer具体含义Tab.1 Specific meaning of Layer

3 仿真与分析

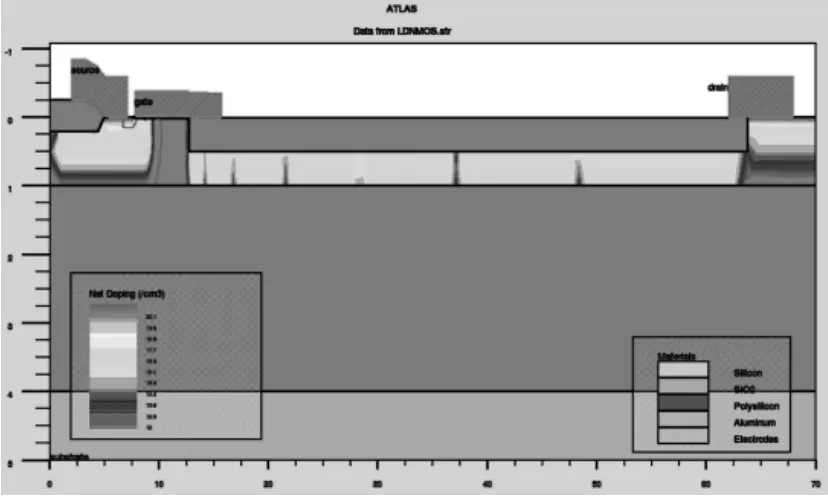

3.1 工艺仿真

SOI工艺中高压器件考虑的主要性能参数有源漏击穿电压BV和线性区域导通电阻Ron.漂移区的长度和浓度会直接影响BV和Ron.一般来讲,漂移区长度越长,BV越大,Ron越小;漂移区浓度越大,BV越小,Ron越大[8].槽氧层的厚度和长度也直接影响BV和器件尺寸的大小.为了使参数最优化,并尽量缩小器件的尺寸,利用SILVACO公司的Athena工具,对器件工艺步骤和结构进行仿真,初步确定出器件的关键尺寸和工艺参数.图2为SOI 600V LDNMOS仿真结构图.

3.2 器件特性仿真

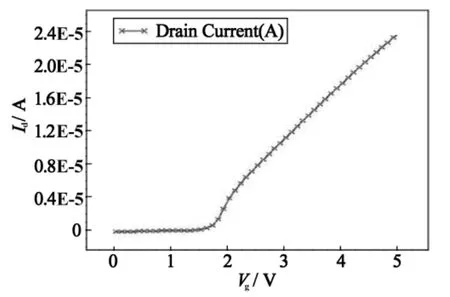

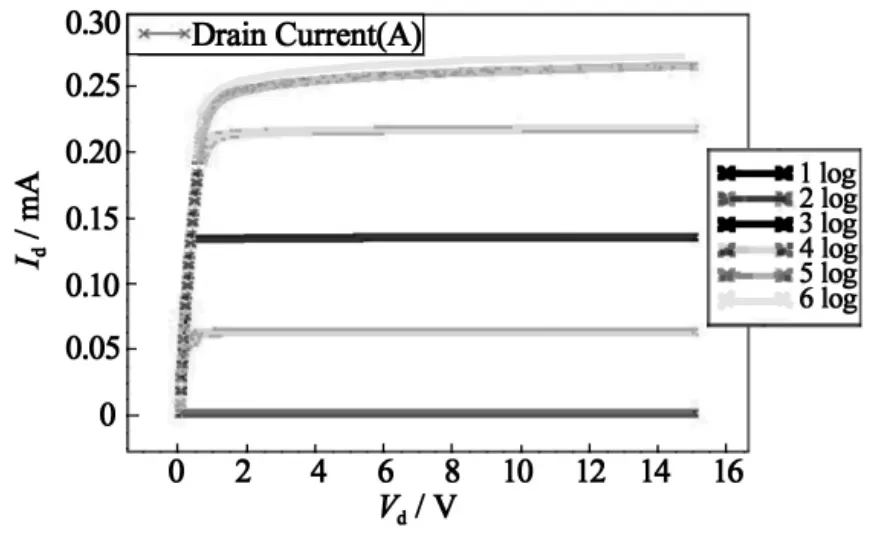

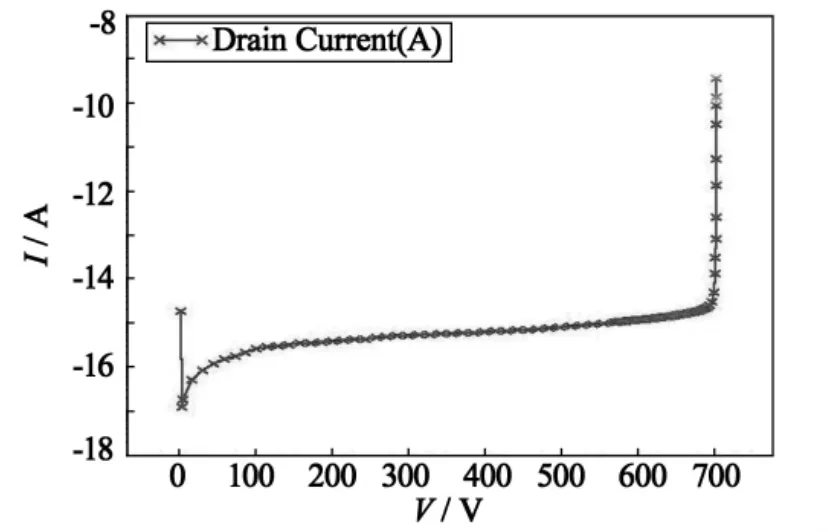

利用SILVACO公司的Atlas工具对器件结构进行电学特性模拟.Gate端加电压0~5 V,Drain端加电压1 V,扫描Drain端电流值得到LDNMOS仿真Id-Vd曲线图(如图3).由图3知,其开启电压Vth为1.7 V;Drain端加电压0~15 V,扫描Drain端电流值得到LDNMOS仿真Id-Vd曲线图(如图4).由图4知,其饱和电流Id为0.30 mA;Drain端加电压0~750 V,扫描Drain端电流值得到LDNMOS仿真BV曲线图(如图5),由图5分析其击穿电压BV为700 V.模拟仿真结果与设计所预期结果非常吻合,说明各掺杂区的杂质掺杂浓度、温度、时间等条件得到了优化,Foundry工艺得到了验证.

图2 SOI 600V LDNMOS仿真结构图Fig.2 Simulation structure of SOI 600V LDNMOS

图3 LDNMOS仿真Id-Vg曲线图Fig.3 Id- Vgsimulation diagram of LDNMOS

图4 LDNMOS仿真Id-Vd曲线图Fig.4 Id- Vdsimulation diagram of LDNMOS

图5 LDNMOS仿真BV曲线图Fig.5 BV simulation diagram of LDNMOS

4 流片测试结果分析

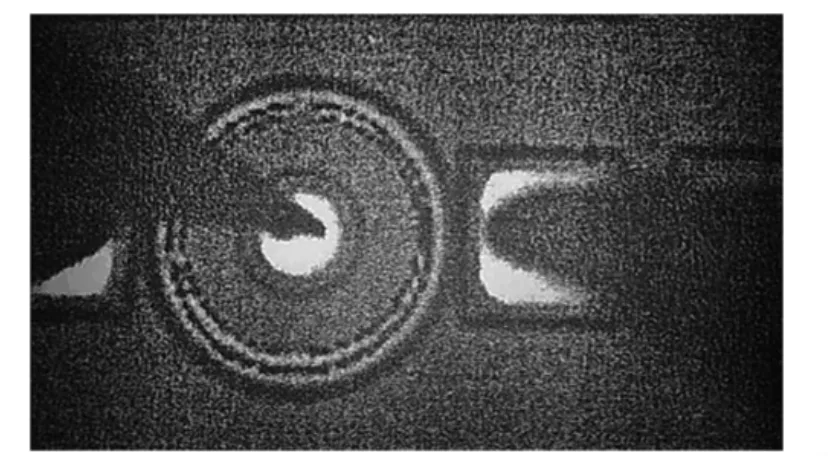

采用0.5 μm 600 V SOI标准工艺,选定新傲公司3 μm埋氧层和1.5 μm顶层硅的SinBond SOI材料,通过模拟仿真确定器件的测试结构并进行on-wafer测试(图6),测试曲线如图7~图9所示.

图6 on-wafer测试图Fig.6 Test chart based on wafer

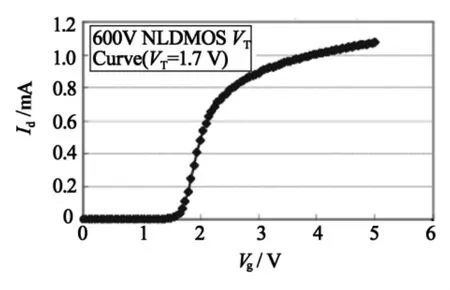

图7 流片测试的Id-Vg曲线Fig.7 Id-Vgcurve of tape- out test

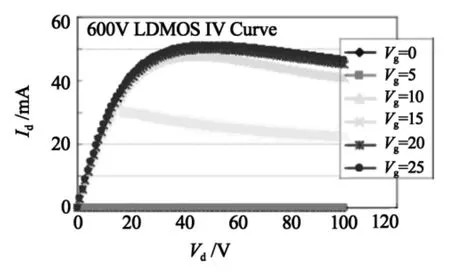

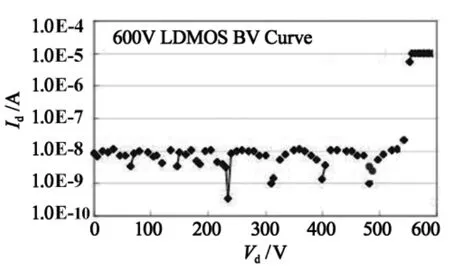

图7中栅极电压加载0~5 V,扫描漏端电流,得到在Vth=1.7 V时,电流开始增大,当Vg=5 V时,Id达到1 mA.图8中,栅极电压分别为0、5、10、15、20和25 V,漏端电压加载0~100 V,扫描漏端电流.当Vg=25 V时,漏端饱和电流Id基本稳定在50 mA.图9中,加载漏端电压0~600 V,发现Vd=550 V时,漏端电流急剧增大,LDNMOS管被击穿.经过数据处理之后,得到了LDNMOS器件的主要性能参数:Vth=1.7 V,Id=48 mA,BV=550 V,与仿真结果相比,BV接近600 V,其他性能参数已达到了设计要求.

图8 流片测试的Id-Vd曲线Fig.8 Id-Vdcurve of tape-out test

图9 流片测试的BV曲线Fig.9 BV curve of tape - out test

5 结语

采用标准的0.5 μm SOI工艺对其中的高压600V LDNMOS进行设计与分析.采用SILVACO软件对器件进行模拟仿真,初步确定器件的设计规则和关键尺寸,再进行流片测试并对所设计器件进行验证.实验结果表明,器件的主要参数基本达到设计目的,并有进一步提升的空间,为下一次设计和流片提供很好的基础.SOI 600 V LDNMOS设计在高压功率器件领域的实际应用中具有重要意义.

[1]施敏.半导体器件物理与工艺[M].苏州:苏州大学出版社,2004.

[2]黄如,张国艳,李映雪,等.SOI CMOS技术及其应用[M].北京:科学出版社,2005.

[3]Yeo K S,Rofail S S,Goh W L.低压低功耗CMOS/BICMOS超大规模集成电路[M].周元兴,张志龙,等译.北京:电子工业出版社,2003:140-150.

[4]Apostolidou M,Heijden V D,Leenaerts M P,et al.A 65 nm CMOS 30 dBm class-E RF power amplifier with 60%power added efficiency[C]//Radio Frequency Integrated Circuits Symposium.[s.l.]:IEEE RFIC,2008:141 -144.

[5]Carroll M,Mckay J J,Ivanov T,et al.A silicon RFCMOS SOI technology for integrated cellular/WLAN RF TX modules[C]//Microwave Symposium.[s.l.]:IEEE/MTT - S International,2007:445 -448.

[6]Park J M,Klima R,Selberheer S.High-voltage lateral trench gate SOI-LDNMOSFETs[J].Microelectronics Joutnal,2004,35(3):299-304.

[7]Pornpromlikit S,Presti J J,Scuderi C D,et al.A 25-dBm high-efficiency digitally-modulated SOI CMOS power amplifier for multi- standard RF polar transmitters[C]//Radio Frequency Integrated Circuits Symposium.Boston:IEEE RFIC,2009:157-160.

[8]Gianesello F,Durand C,Pilard R,et al.High voltage devices added to a 0.13 μm high(symbols)resistivity thin SOI CMOS process for mixed analog-RF circuits[C]//Microwave Symposium.Hawaï:IEEE/MTT -S International,2007:171 -173.

[9]Bon O,Gonnard O,Gianesello F,et al.First 15 V complementary LDMOS transistors in thin SOI 65 nm low power technology[C]//Power Semiconductor Devices and IC’s,2007 ISPSD ’07 19th International Symposium on.Crolles:IEEE Power Semiconductor Devices and IC’s,2007:209-212