光谱仪CCD数据采集中SoPC系统设计及USB2.0 IP核的实现*

席忠红,李海翼

(甘肃民族师范学院物理与水电工程系,甘肃合作747000)

XI Zhonghong,LI Haiyi*

(Department of Physics and Hydranlic Engineering,Gansu Normal University for Nationalities,Hezuo Gansu 747000,China)

近年来,CCD(Charge Coupled Device)以其光谱响应宽、动态范围大、灵敏度高、噪声低、体积小、像素多等优点[1-2],在光谱仪器中,常使用它作为光电转换元件。特别是在出现了背照式CCD后[3],它的光谱范围可以延伸到深紫外区,可以成为全谱式光谱仪的检测器件。FPGA作为可编程门阵列,可以产生时钟严格同步的多路信号,是驱动CCD数据采集的首选器件之一,特别是基于FPGA[4]的SoPC技术的应用[5-6],使数据采集控制、数据同步处理和转换传输融合为一体,同时通过调用IP核(Intellectual Property),使设计过程变得更为简捷和可靠。通用串行总线USB2.0接口具有最高480Mb/s的传输速度,可以把高速采集到的光谱数据及时送给上位机软件,本文将调用SLS公司的USB20HR IP软核实现USB2.0接口,从而代替了专用USB芯片,不但节约了成本,而且使整个系统更紧凑。

1 系统组成及功能

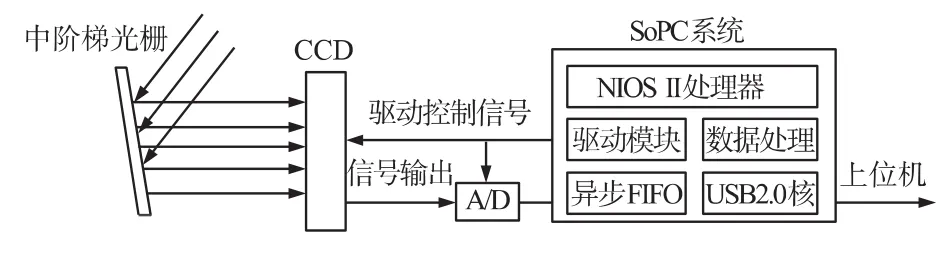

本文要实现的系统的结构及功能如图1所示。基于FPGA的SoPC系统通过可编程硬件来实现。

图1 系统功能及结构框图

1.1 驱动模块

驱动模块用Verilog HDL语言编写,为了保证时序的同步性,所有控制信号都在同一个基准脉冲下产生,这个基准脉冲是片上锁相环PLL输出的12 MHz时钟脉冲。考虑成本和满足使用的要求,CCD器件选择线阵CCDILX554B;A/D转换器件选择并行12位输出的 ADS803E,最高并行转换时钟2 MHz。

所实现驱动模块的逻辑功能时序仿真如图2所示。为了顶层设计的方便,在验证此模块后,把此逻辑功能生成一个具有输入输出的独立模块,以供调用。

图2 驱动模块逻辑功能时序仿真图

1.2 异步 FIFO

为了提高采集效率和降低误码率,采用异步时钟FIFO(First In First Out)缓冲数据,调用片上FIFO IP核,入口端设为Avalon-ST Sink接口,时钟和控制信号也由驱动模块按一定的时序提供,这个接口的优点是把A/D转换完的数据源源不断地送给FIFO,不需要CPU的参与,提高了效率;出口端设为Avalon-MM slave,时钟取自系统时钟,当FIFO达到半满标志时,FIFO核向片上CPU发出中断请求,CPU响应中断后,控制DMA,把FIFO里的数据高速取走,经过处理后,通过USB接口送给上位机。另外,为了把A/D转换完的数据送给Avalon-ST Sink入口的FIFO,必须在SoPC builder设计时例化一个新Avalon Streaming Source接口部件,部件的输出直接接到FIFO,输入接外部数据端。同时,这个新部件为FIFO补齐32位数据位宽,方便对接。

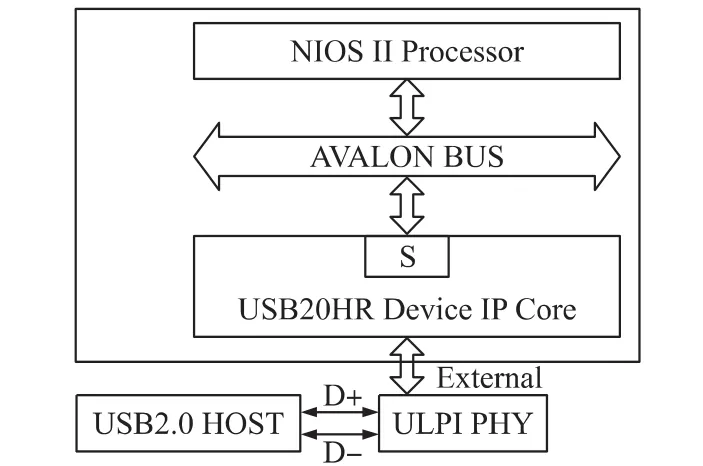

1.3 USB2.0 接口

为了把采集到的大量数据即时地传送给上位机,采用USB2.0通用串行总线协议接口。它具有高传输速度、即插即用、可以总线供电、与主流上位机兼容等优点。本文采用SLS公司USB20HR软核,把 USB2.0接口集成到 SoPC系统。USB20HR是基于片上RAM的USB从设备软核,支持32位Avalon总线接口,可以设置批量传输、中断传输和同步传输,最多可支持15个 USB输入输出端点[7]。该IP核代替了传统USB芯片的功能,可以节约成本,也使图3 USB20HR与Avalon总线及外部连接整个系统融合为一体,更大程度上体现了SoPC技术的优势。USB20HR IP核与SoPC系统Avalon总线的连接及外部接口,通过外部串行解码芯片ISP1504,就可以实现和上位机通信的功能。

图3 USB20HR与Avalon总线及外部连接

2 SoPC系统实现

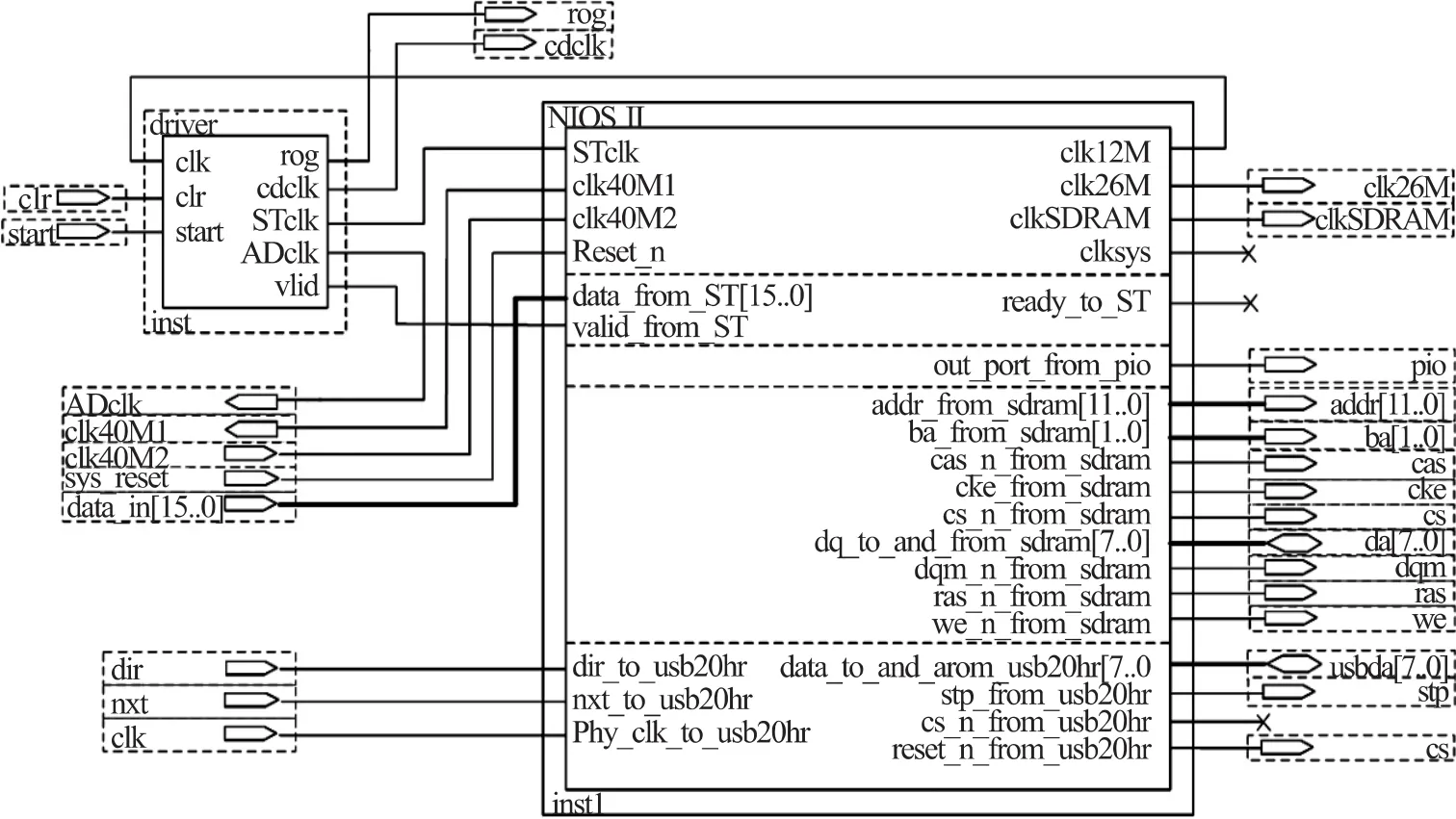

在例化NIOSⅡ处理器的基础上,调用相应模块和IP核,构建整个SoPC系统,其顶层逻辑连接和结构设计如图4所示。

图4 SoPC系统顶层逻辑连接和结构框图

图4中,driver模块即为CCD、A/D控制驱动模块,转换后的数据由data_in引脚端口送给Avalon-ST source接口部件,经位宽调整后送入FIFO;图中NIOSⅡ模块是由SOPC Builder而自定义生成的包含NIOSⅡ处理器、片上RAM、DMA控制器、异步FIFO、USB20HR、FIR、SDRAM 控制器、EPCS控制器、锁相环PLL等单元的综合模块,每个单元拥有独立的基地址和IRQ优先级值,NIOSⅡ处理器作为Avalon Master,可以通过Avalon总线访问任何一个Avalon Slave单元。系统时钟的布置,以40MHz外部时钟,作为两个锁相环PLL的时钟输入。PLL0的输出CO设为12MHz,给驱动模块提供基准时钟,C1为50MHz,给NIOSⅡ处理器和其它模块提供时钟,C2为50MHz,从PLL的专用管脚输出,提供给外部SDRAM;PLL1的C2设为26MHz,从专用管脚输出为ISP1504提供时钟,以进一步产生60MHz脉冲,为ULPI提供同步时钟信号。其次,虽然硬件配置文件和软件程序可以下载在配置芯片EPCS等上,但程序运行时在RAM中运行,为了满足后续一定容量的程序运行的需要,在片外扩展一片8MB SDRAM MT48LC8M8A2,设置PLL1 C2时钟相移-60°,接到SDRAM时钟输入端。在顶层框图中为各模块分配输入输出引脚,执行分析综合,利用Time-Quest

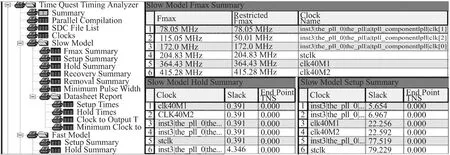

Analyzer对各时序进行约束,以满足Fmax、tco、tsu等要求,编写SDC约束文件,用create_clock命令对输入时钟约束,定义它的周期、上下沿;用derive_pll_clocks命令为锁相环定义输入时钟,用set_clock_groups约束时钟组是否同时有效。约束后的全编译结果如图5所示。时序分析和仿真后,编译结果满足设计要求。执行全编译,生成SOF和POF硬件配置文件。

图5 TimeQuest Analyzer时序分析报告

3 SoPC系统软件设计

基于FPGA的SoPC系统既要实现可编程硬件描述的目的,也要有软件来控制片上NIOSⅡ处理器实现相应功能。软件开发是在集成开发环境NIOSⅡIDE下编写C程序及调用HAL系统库,以及编译和调试程序。产生基于前述硬件的System.h文件,它提供了所有SoPC硬件系统完整的描述,包括每个调用硬件的名称、基地址、中断优先级等,为NIOSHAL系统库及其驱动提供了基础。NIOS系统库定义了各数据类型,输入输出函数,设备分类等。调用NIOSⅡHAL,会在驱动的配合下,映射到硬件,实现相应功能[8]。

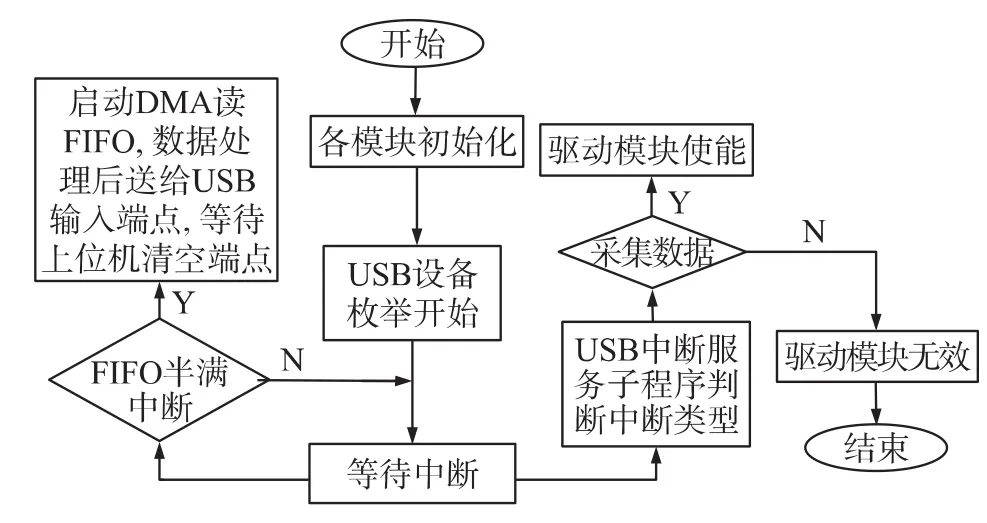

本文主程序流程如图6所示。上位机发送CCD数据采集的开始、停止等命令,通过USB中断通知NIOSⅡ系统,控制驱动模块输出有效驱动信号或停止输出有效信号,来实现数据采集的开始、停止等过程。

图6 NIOSⅡ主程序流程图

系统上电并自动完成硬件配置后,NIOSⅡ系统从EPCS4中开始BOOT,并完成各模块的初始化及USB设备的枚举,然后用while()命令开始轮询各中断源。当要开始采集时,由上位机通过USB接口发送中断指令,使接有上拉电阻的I/O变为低电平,也即把接在一起的start信号拉低,驱动模块开始工作。CCD输出信号不断送入FIFO,FIFO半满时向NIOSⅡ产生中断,中断服务程序立即启动DMA,高速读取FIFO半满深度字节数的数据,做数据处理后,送入USB20HR的输入端点RAM,等待上位机及时取走数据。为了采集的完整性,在设计中,设置FIFO中断优先级高于USB中断。

4 应用测试和结果

4.1 PCB 设计

设计在自制PCB板上完成,考虑成本和满足使用的因素,采用Altera EP2C8 FPGA芯片。板上采用JTAG+AS联合配置模式,方便调试及调试成功后的上电自动配置,串行配置芯片选择EPCS4。

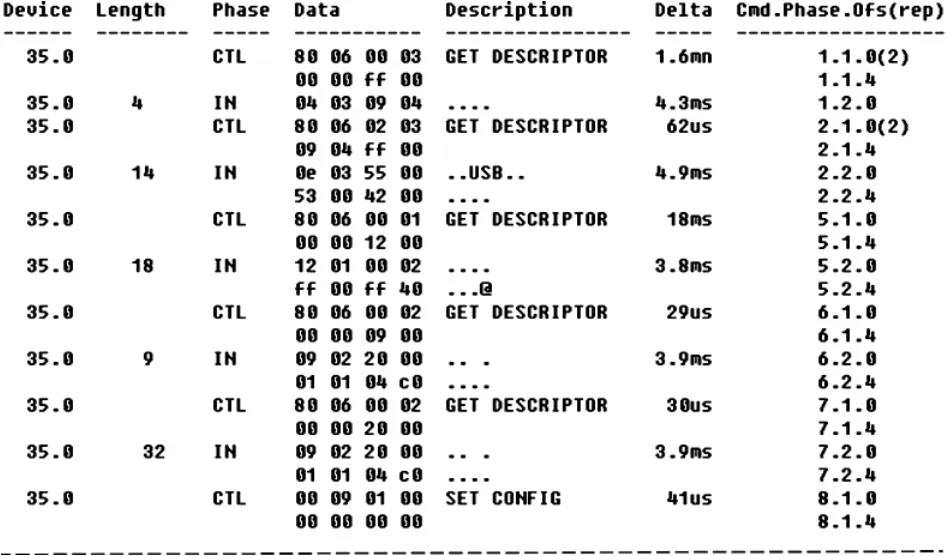

4.2 USB枚举及数据读写

USB通信是主-从式的通信方式,由主机发起通信,设备做出响应。USB上位机枚举是USB设备连接到上位机系统,由系统指定唯一地址码,获取设备相关信息和描述符,并为设备加载驱动程序的过程。在此过程中,默认在设备的端点0用控制传输方式通信。枚举是每个USB设备能够正常通信的必须过程。本文在主程序中调用NIOSⅡ HAL,控制USB20HR核开始枚举。用USB调试工具捕捉到枚举过程如图7所示。

图7 USB20HR枚举过程数据捕捉

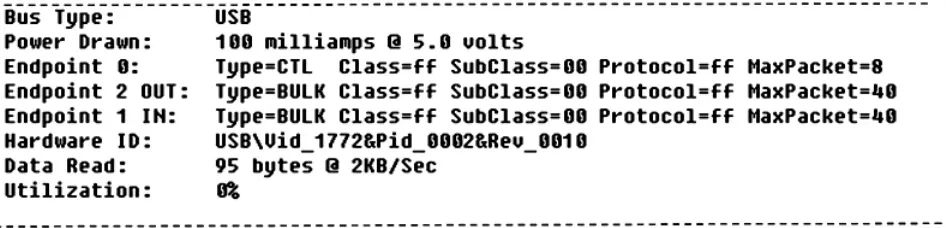

枚举过程中系统为USB20HR分配唯一设备号,枚举完成后,USB20HR在NIOSⅡ软件中设置的端点信息为上位机掌握,如图8所示。端点0为控制端点,端点1和2分别为输入和输出端点,所能传输的数据包的最大值为40字节。

图8 系统读取到的USB20HR设备端点信息

枚举完成后,手动为USB设备加载相应驱动程序,之后,USB就可以和上位机实现通信。编写简单上位机程序,验证USB读写批量数据成功,平均速度超过90 Mbit/s,能很好满足CCD数据采集任务。

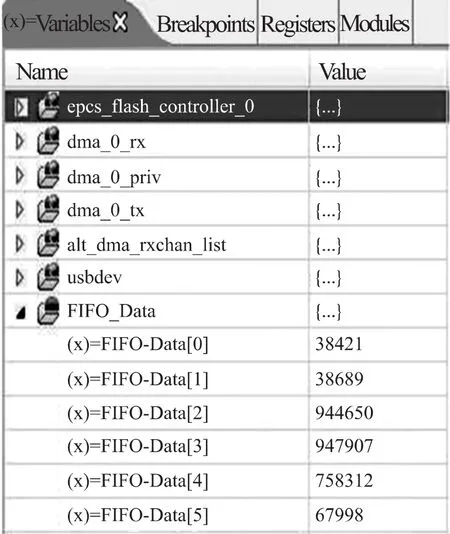

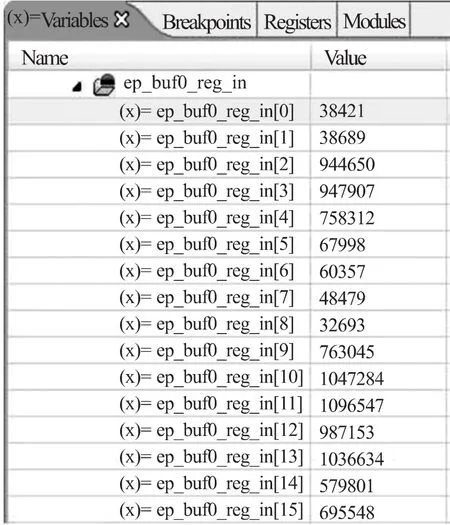

4.3 CCD数据采集程序Debug

为了验证采集系统的功能,在NIOSⅡIDE环境下,利用NIOSⅡHardware Debug进行在线测试,在Debug之前,设置 NIOSⅡ处理器支持 Level 3级Debug。连接CCD及各电路模块,下载.sof硬件配置文件到FPGA,手动控制CCD模块使能,在程序中设置断点,读出FIFO的几个字节数据,Debug结果如图9所示。图中显示的是32位数据的十进制值。送给USB输入端点的数据如图10所示,USB20HR输出时默认最小输出4个字节,即32位无符号数据。在在线硬件测试时,从FIFO读出的数据,经过一定处理后,以每次4个字节的写操作,送到USB20HR的输入端点,等待上位机及时取走这些数据。从图10中可以看出,处理完的FIFO数据经过中间的读写操作送到USB输入端点缓存后,数据顺序操作前一致。因此,上位机可以读到正确的数据行。

图9 FIFO读出数据

图10 USB20HR输入端点数据

5 结论及展望

本文提出了可应用在光谱仪器中的CCD数据采集系统,提供了完整的下位机方案。通过仿真和实际测试,本文所设计的CCD数据采集驱动模块能满足驱动CCD信号积分及数据输出及使能控制的目的,能为A/D转换及Avalon-ST接口提供正确时序的驱动信号;调用USB20HR软核实现了USB2.0接口,通过加载驱动程序和实验验证,实现了USB2.0接口的全部功能;通过在线硬件Debug测试,FPGA硬件工程和NIOSⅡ软件实现了预期功能。本文设计的CCD数据采集系统方案结构简单有效,集成度高,系统紧凑可靠。在光谱仪器中具有很好的实用价值和应用前景。本文下一步将研究基于本文系统的应用于光谱仪器的上位机应用软件。

[1] 米本和也,陈榕庭,彭美桂.CCD/CMOS图像传感器基础与应用[M].北京:北京科学出版社,2006.

[2] 宋敏,郐新凯,郑亚茹.CCD与CMOS图像传感器探测性能比较[J].半导体光电,2005,26(1):5-9.

[3] 戴丽英,刘德林.背照式电荷耦合器件的研制[J].光电子技术,2005,9:25-30.

[4] 范铁道,田雁,曹剑中,等.基于FPGA的CMOS图像感器IA_G3 驱动电路的研究[J].电子器件,2009,32(2):269-276.

[5] 陈东明,叶玉堂,蒲亮,等.基于SOPC可重构的图像采集与处理系统设计[J].电子器件,2011,34(2):232-236.

[6] 高文韬,李伟明,丁晓明.基于SOPC技术的图像采集模块设计[J].信息科技,2007,6:126-127.

[7] SLS,USB2.0(USB20HR)document.2009,(2.2)6.

[8] 俞一鸣.Altera可编程逻辑器件的应用与设计[M].北京:北京机械工业出版社,2007.