基于FPGA 的频率特性测试仪的设计

郭伟然,刘 耀,汤勇明

(东南大学电子科学与工程学院,南京 210096)

早期的频率特性测试是通过手动改变频率的方法逐点测量完成的(称点频测量法),后来随着仪器科学技术的进步,输入信号频率在一定范围内可自动改变,成为目前的扫频仪,专门用于电路系统频率特性的测量[1-3]。下文提出了一种新的扫频仪设计,可以较精确地测量被测网络的幅频特性和相频特性,并能以显示其函数图像的方式表达测试结果。

1 工作原理

在线性时不变(LTI)系统中,系统对激励的响应可表示成[1]:

由定义:若系统对一个信号的输出响应仅是一个常数乘以输入,则称该信号为系统的特征函数。因为:

所以复指数是LTI 系统的特征函数。再由正弦波与复指数信号间关系可知:LTI 系统对正弦波的响应仍是正弦波,只是幅值和相位有差别。通过对激励与响应的幅值和相位差别的测量,可以得到待测系统的频率特性。

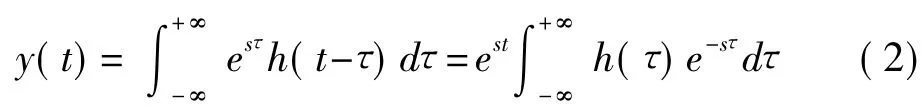

2 系统组成及功能

扫频仪的整体功能框图如图1所示。系统利用扫频信号源产生作为基准信号的正弦波,其频率变化范围覆盖500 Hz至125 kHz。将该正弦波通过被测网络后可获得其失真后的波形。使用幅频测量与相频测量两个模块对基准信号及其失真后的波形进行对比分析,即可求得被测网络的幅频特性与相频特性。最后将数据分析处理后形成图像输出就完成了系统的设计目标。其中虚线框内的设计均由FPGA 实现。

图1 扫频仪的整体功能框图

2.1 扫频信号源

本系统的信号发生电路采用DDS 技术(即直接数字频率合成技术)实现[4],用于产生频率、持续时间等均可控的扫频信号,并能够满足一般用户对较宽频率范围的要求[5]。实现方法是:由单片机动态对专用DDS 芯片(AD9850)写入控制字,以产生所需的扫频信号。该方案相较于直接频率合成、锁相频率合成以及数字锁相法有很大优势。AD9850 的输出频率与控制字及参考时钟频率关系由下式决定:

2.2 增益与相位检测原理

这一部分是扫频仪系统的核心,检测被测网络两端的幅度比和相位差所使用的技术有较大差别。幅度比检测的解决方案:从被测网络两端引出基准扫频信号与通过网络后发生失真的扫频信号。将这两路信号通过真有效值检测电路求得其有效值,之后将信号输入A/D 转换器转化为数字量,再送入FPGA 进行乘除法等一系列的运算,得到被测网络的幅频特性。注意适当增大输入A/D 转换器的信号幅度可以充分利用A/D 转换器的字长,利于减小量化误差。

相位差检测的解决方案:同样从被测网络两端引出基准扫频信号及通过网络后发生失真的扫频信号。将这两路信号输入过零比较器,使得正弦扫频信号转化为同频率的扫频方波,该方波的电平与FPGA 相兼容,即两路可以被当作数字信号的方波。这两路数字信号输入FPGA 内部,利用脉冲填充计数法,求得它们的相位差。经过数据运算及处理就得到被测网络的相频特性。该方案检测精度有赖于FPGA模块的时钟频率(50 MHz)远大于输入方波频率这一假设。该假设是限制本仪器测量带宽的主要因素。使用PLL 锁相环可使时钟信号加倍,但不利于系统稳定。本方案中带宽设置为500 Hz至125 kHz。

2.3 频率特性显示原理

将幅度比和相位差以及相对应的频率数据存储在双口RAM 中,VGA 扫描信号HSYNC和VSYNC以地址映射的形式读取双口RAM 内的相应数据,输出到屏幕上形成幅频特性和相频特性函数图像。屏幕上的内容还包括坐标轴的文字标注等。在设计显存时,比较可行的方案有两种:一是把频率对应的数据直接存储在双口RAM 中,需要开辟相应数量的RAM 存储空间。二是把频率数据和相应的幅度,相位数据整合成“频率+幅度比”和“频率+相位差”的等效数据形式,把等效数据以地址的形式存储在双口RAM 中,这需要开辟2×65 536个位的RAM 存储空间。第1种方案节约空间,但方案可移植性不好,对于后期扩展不便。第2种方案解决了上述问题。尽管资源占用较大,但在M4K 足够多的前提下,扫频的范围易于增加。

2.4 增益与相位检测以及频率特性显示

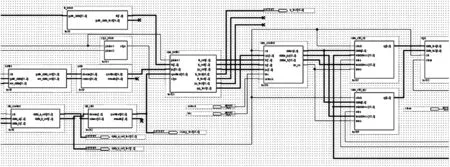

如前文所述,FPGA 用于实现增益与相位检测,以及控制VGA 显示幅频特性曲线和相频特性曲线。为实现上述功能,首先设置Start模块和div_500k模块分别给经A/D 转换输入FPGA 的数字信号提供启动信号和500 kHz 的工作频率。再设置名为Counter32(inst20)的模块用于全局时钟50 MHz 的脉冲计数,得到的数据经过fx_block 转换成外界输入信号(未经过衰减的标准输入信号)的实际频率,从而确定了频率特性曲线上的各个频点的频率横坐标。利用Xor和Counter32(inst16)模块得到了两路相位差的脉冲计数值,通过x180,buffer,piv模块转换,得到两路相位差的实际度数值。其中sign_block用于判断第二路相位信号(经过网络衰减的待测输入信号)较之第一路相位信号的超前或滞后情况:sign为0 表示滞后,sign为1 表示超前。另外Div_control和div_ctrl模块采集两路信号的幅度信息,转换成幅值比的形式,供后续处理。

Ram_buffer和Ram_control模块用作信号缓冲,并将三个8 位的频率,相位,幅度比信息整合成16位的“频率+相位”和“频率+幅度比”信息,完成各个频点对应,并在wr_en 时序控制作用下同步输出。Ram_ctrl_xfy和ram_ctrl_xpy模块分别用于存储16位的“频率+相位”信息和“频率+幅度比”信息。Vga模块用于控制VGA 端口实现幅频特性曲线和相频特性曲线的显示,在读信号rd_out1和rd_out2有效时,从Ram_ctrl_xfy和ram_ctrl_xpy 读取信息。

为了避免出现冒险竞争甚至逻辑错误,在两级级联模块间加入缓冲模块Ram_buffer和Ram_control,在全局分频时钟下同步输出,供后级模块使用,保障系统稳定工作。

以上工作模块的顶层设计如图2所示,在ALTERA 公司FPGA 芯片EP2C8 中编译实现,其资源利用情况如下:使用LE为4174/8256(51%),其中Total Combinational Functions为3803/8256(46%),Delicated Logic Registers为1011/8256(12%)。共用有效引脚为33/138(24%)。共用内存位单元为134656/165888(81%)。

图2 FPGA 的顶层设计

2.5 同步控制

本仪器的扫频信号源和显示部分的工作是协调一致的,利用最少的资源达到良好的显示效果。当扫频信号处于某一频率时,显示部分也与之对应。另外,整个系统的各功能模块的处理速度也都控制在同等量级上,使得系统工作更加协调。

2.6 被测网络

本仪器设计目标可以测量包括高通、低通、带通、带阻及其它复杂组合的无源或有源网络。为尽量适应不同被测网络对仪器驱动负载能力的要求,被测网络的前一级信号源具有较强的电流输出能力,可确保驱动低输入阻抗的被测网络,并且被测网络的后一级具有较高的输入阻抗,使得在被测网络输出阻抗较大时能尽量减小测量误差[6]。为了验证本扫频仪的性能,使用了具有典型意义的双T 带阻网络,具体验证方法见本文第3 部分。

2.7 扫频仪操作步骤

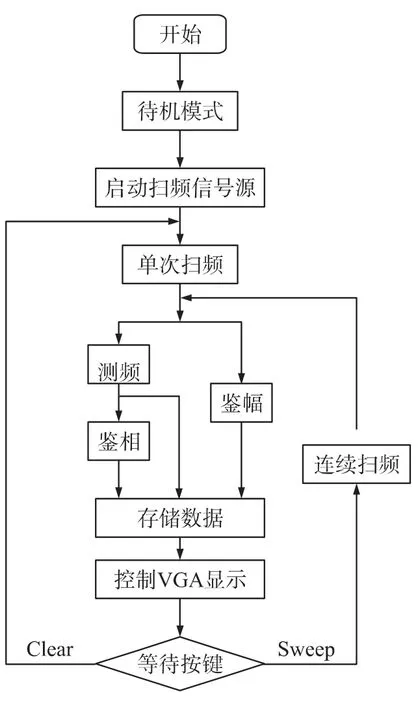

首先将待测网络接入扫频仪。打开单片机模块的开关,即开始扫频(默认情况下只扫频一次);按下FPGA模块的Clear 按键,可以清除屏幕上的图像,以实现重新测量;按下Sweep 键,可以实现任意时间范围内的扫频功能。根据坐标显示和网格精度就可以读取相应频率处的幅度比和相位差数据。具体过程如图3所示。

图3 程序流图

3 功能测试与误差分析

3.1 利用仿真进行定性分析

制作一个中心频率约为50 kHz 的双T 带阻网络,以便对扫频仪的实际功能进行检验。将带阻网络元件参数代入网络传递函数:

其中:ω0=1/RC,Q=1/4。

使用MATLAB 仿真[7],结果如图4所示。图4表明系统的幅频特性是:随着信号频率的提高,系统对信号的通过能力迅速下降,至50 kHz 附近降至最小值,而后随着信号频率的提高,系统对信号的通过能力缓缓上升。相频特性是:随着信号频率的提高,系统对信号的相位产生影响,相位开始逐渐落后,至50 kHz 附近对应-90°,而后随着信号频率的提高,信号相位突变至+90°,之后相位超前的程度缓缓下降。其中50 kHz 对应的正是双T 带阻网络的中心频率。采用本扫频仪实际测试所得图像与仿真结果高度吻合,证明了本扫频仪测试处理的正确性。

图4 MATLAB 仿真结果

3.2 利用对照实验进行定量分析

仿真只能定性反映理想状态下的结果,而实际网络特性与传递函数之间必然有所偏差。为了定量检测仪器性能,使用传统的点频测量法与本扫频仪测量值相比较。点频测量法利用函数发生器(F05A型)作为信号源输出单音信号,双踪示波器(Tektronix TDS 1012)通道1 接在信号输入端,通道2 接在信号输出端,通过对两个通道测得信号的比较,可以得出被测网络在当前频率下的幅度响应与相位响应。表1所列为分别采用本扫频仪和点频测量法测得的数据以及相对误差。

分析表1 中数据可知:扫频仪测得数据相较点频测量法所得数据在变化趋势上完全吻合。就单一频率对应数据而言,绝对误差与信源输入信号比值基本在5%以内。误差较大的数据一般出现在系统频率响应变化较为剧烈的频段。如何减小这些误差有待于进一步的实验研究。

表1 扫频仪和点频测量法测得数据及其对比

4 结语

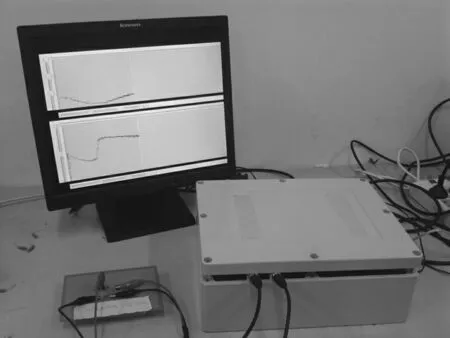

最终成品如图5所示。图中测试对象为带负载的带阻网络。使用同轴线可以有效减少信号在引出机箱后受到的外界干扰[8],并且有一定的机械强度便于使用。当然,该仪器仍有较多改进空间,例如以人性化为目的的界面程序设计,减轻对仪器使用者的要求;整机仍有进一步小型化的空间。

图5 扫频仪成品及实测结果

[1]李文杰.频率特性测试仪系统的设计[D].南京航空航天大学,2005年1 月.

[2]胡泽民,姚晓亮,杨林杰.基于MCU和FPGA 的波特仪的设计[J].电子测试,2008(7):55-60.

[3]张春水,张佳培.基于单片机和FPGA 的频率特性测试仪[J].电子设计工程,2009(1):63-65.

[4]刘兰坤,潘明海.DDS 的杂散分析及降低杂散的方法[J].电子器件,2007,30(2):572-578.

[5]朱磊.DDS 芯片AD9852 的应用问题分析[J].电子器件,2008,31(4):1141-1143.

[6]王小利.宽带直流放大器系统设计[J].电子器件,2010,33(3):392-394.

[7]孟桥,董志芳,王琼.信号与系统MATLAB 实践[M].北京:高等教育出版社,2008.

[8]雷威,张晓兵,王保平.电磁场理论及其应用[M].南京:东南大学出版社,2005.