应用于频率综合器的多模分频器设计

詹海挺,孙玲玲,高海军

(杭州电子科技大学射频与电路系统教育部重点实验室,浙江杭州310018)

0 引言

随着当今消费电子业类技术的发展和市场的需求,采用低成本的CMOS工艺实现无线收发系统的单芯片集成已成为学术界和工业界研究的热点。作为射频前端部分关键模块之一的频率综合器,其性能直接影响到接收机的灵敏度,相位噪声等指标。分频器是频率综合器的重要组成部分,基于吞脉冲计数器的结构是目前广泛使用的分频器结构[1]。分频器的实现方式主要有真单相钟控电路和源耦合结构两种。真单相钟控电路技术采用动态CMOS技术,具有管子少、电路结构简单和功耗低等优点,但在低电源电压下这种结构无法操作在较高频率[2]。源耦合技术具有低摆幅,高速度,低噪声,抗干扰能力强等优点,是一种基于差分结构的逻辑电路[3]。本文采用源耦合结构和标准数字逻辑单元等设计了一种可应用于整数或分数频率综合器的多模分频器。

1 总体结构

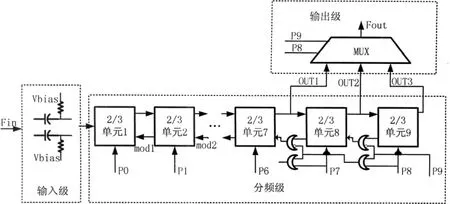

该电路由输入级、分频级和输出级3部分组成,其总体架构如图1所示:

图1 多模分频器总体架构

在频率综合器里,压控振荡器的输出差分信号经过输入级的隔直偏置电路,使差分信号偏置在分频级要求的直流偏置点。分频级实现分频功能,由9个2/3单元和逻辑门组成,其分频模数由P0、P1、…、P9控制。输出级电路完成输出信号的选择。

2/3单元采用吞脉冲技术,能实现2分频或则3分频功能,其分频数由mod和P共同控制。当mod和P都为1时,2/3单元为一个3分频器,否则为2分频器。图1中的分频级,根据文献4的算法,OUT1的分频数为,OUT2 的分频数为,OUT3 的分频数为,通过输出级的选择,Fout的分频数为

2 模块电路

2.1 隔直偏置电路

输入级是一个隔直偏置电路,由电容和电阻组成。电容C的作用是滤除VCO输出差分信号的直流成分,电阻R和偏置电压Vbias的作用是给差分信号提供直流偏置,以满足分频级对差分输入信号的直流要求,此处Vbias为950mV。这里电阻电容组成一个高通滤波器,频率小于1/2 RC被滤掉而达不到分频级。此电路由于版图的布局考虑,选择了电阻R为679Ω,电容C为1.066pF,可得频率大于221M的信号都将通过,远满足最低频率600M的要求。

2.2 2/3 分频单元

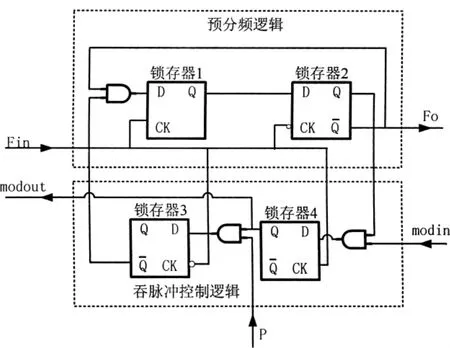

2/3分频单元由预分频逻辑和吞控制逻辑组成,如图2所示:

图2 2/3单元结构图

预分频逻辑实现电路分频,吞脉冲控制逻辑实现电路控制。当modin为低时,吞脉冲控制逻辑反馈给预分频逻辑的电平为高电平;当modin为高,若吞控制逻辑检测到P为高,则吞控制逻辑会强制预分频逻辑吞掉Fin的额外一个周期,即为3分频;否则,则预分频逻辑仍保持在2分频状态。

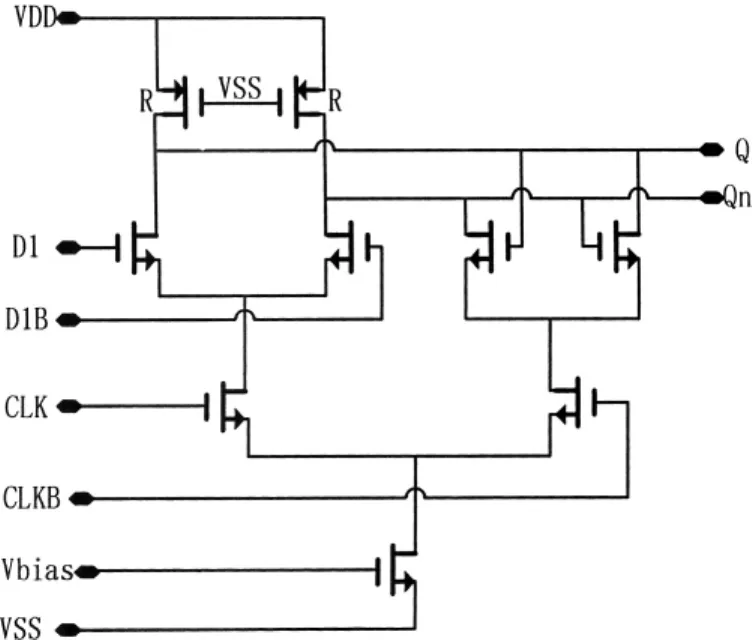

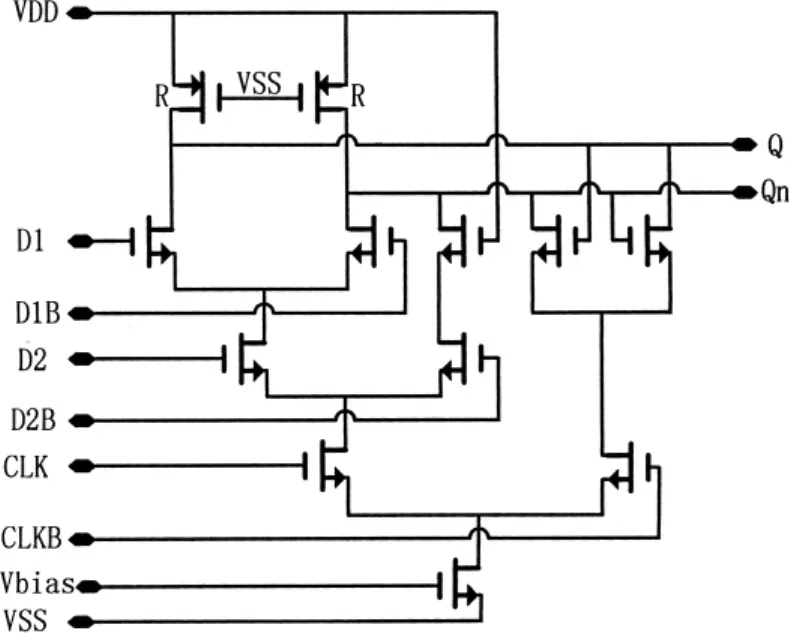

文献5提出了一种SCL结构锁存器的实现,该文进行了改进,用工作在线性区的PMOS管作为负载,一个单输入D锁存器和一个与门组成一个双输入的D锁存器如图3、4所示。

图3 单输入锁存器

图4 双输入锁存器

2.3 输出级电路

输出级电路如图5所示,当P9为高电平,Fout选择OUT3;当P9为低电平,P8为高电平时,Fout选择OUT2;其它情况选Fout选择OUT1。从而Fout的分频数达为。放大级电路是放大3路传输门线与后的信号,以满足反相级的驱动电平要求。

图5 输出级电路

3 电路仿真结果及版图

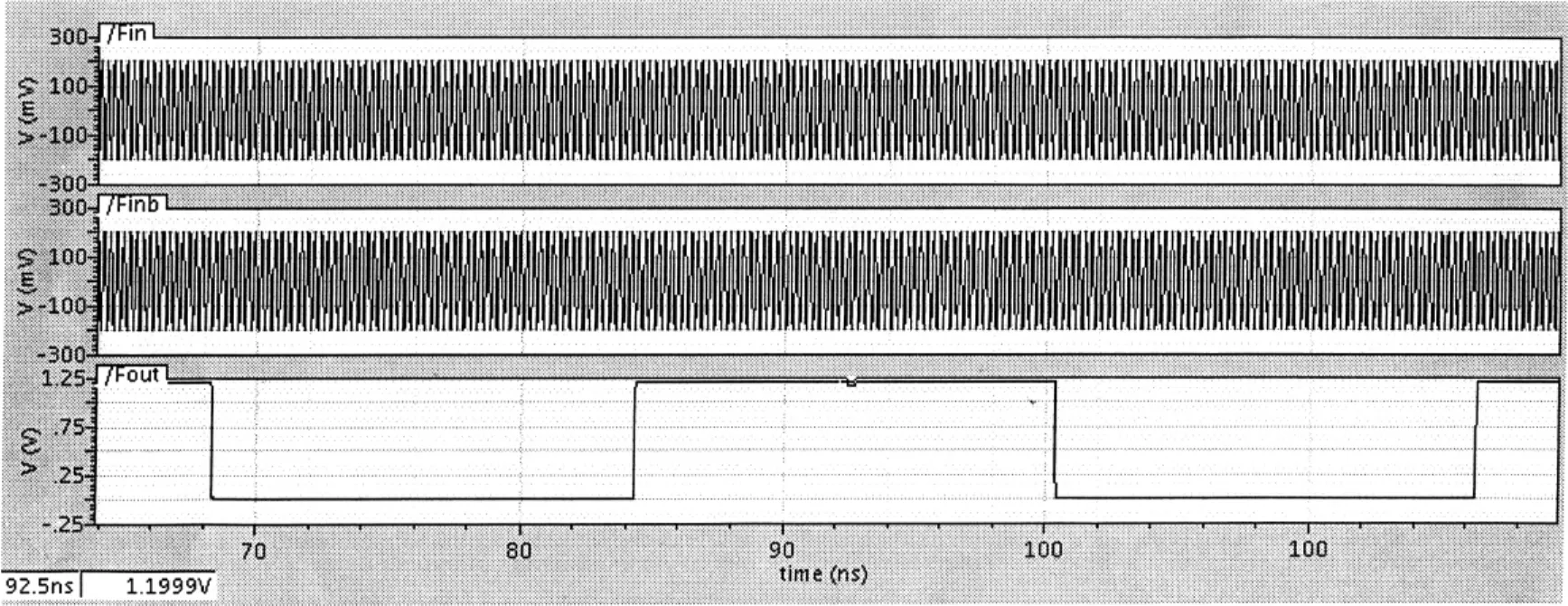

整个分频器电路采用smic 65nm工艺实现,除去PAD,分频器版图面积为160μm×73μm。加上PAD后的版图面积为709μm×559μm,功耗5mW。在输入差分正弦信号频率为600MHz-4GHz、输入峰峰值为400-500mV、工艺角为tt、ss、ff、sf、fs情况下,后仿真满足128-1 023分频数的要求。如图6所示为分频器在压控振荡器输入频率为4G,输入电压峰峰值为400mV,工艺角为tt情况下225分频的后仿真波形。

4 结束语

本文采用了smic 65nm工艺实现了一个应用于频率综合器的多模分频器。通过模式控制,能实现输入频率范围为600M-4G、峰峰值为400mV以上的差分信号进行128-1 023范围内的任何模数分频。经过版图寄生参数的提取及认真地后仿真结果表明,所实现的电路在各种工艺角下均能达到要求。

图6 多模分频器仿真波形

[1] Lam C,Razavi B.A 2.6 - GHz/5.2 - GHz frequency synthesizer in 0.4 - um CMOS technology[J].IEEE Journal of Solid-State Circuits,2000,35(5):788-794.

[2] Yuan J,Svensson C.High -speed CMOS circuit technique[J].IEEE Journal of Solid -State Circuits,1989,24(1):62-70.

[3] Huang C M,Floyed A,park N,et al.Full Integrated 5.35 GHz CMOS VCOs and Prescalers[J].IEEE Trans Microwave Theory and Tech,2004,49(1):17-22.

[4] Vaucher C S,Ferencic I.A family of low -power truly modular programmable dividers in standard 0.35-um CMOS technology[J].IEEE Journal of Solid -State Circuits,2000,35(7):1 039 -1 045.

[5] 池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2007:517-518.