700V nLDMOS击穿电压参数设计

文 燕,张 枫,李天贺,李 娜

(深圳方正微电子有限公司,广东 深圳,518116)

1 引言

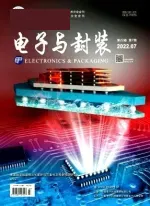

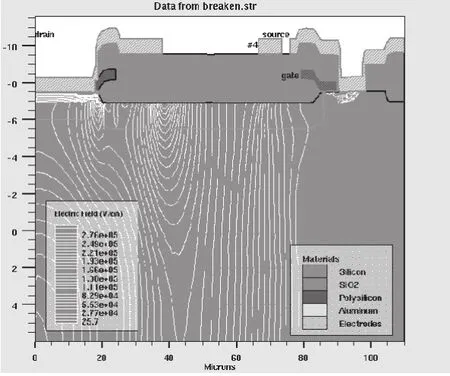

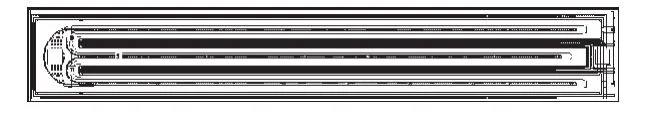

高压集成电路(HVIC)目前已被广泛应用于开关电源、电机驱动、工业控制、汽车电子、日常照明、家用电器等领域。HVIC一般由高压和低压器件组成,所以高压器件需与低压工艺兼容,和低压器件集成到一起时可以实现自主隔离,采用基于SOI材料的工艺技术,生产成本往往很高[1~3],因而迫切需要解决既能兼容普通半导体材料工艺又能达到相应技术性能要求的芯片设计及工艺问题。本文采用一种如图1的结构,这种结构中NWELL而非N-外延层作为RESURF LDMOS的漂移区,为了更好地提高击穿电压,在漏、源区增加了场极板。对于RESURF LDMOS器件,漂移区的结构及场极板的设计是控制源漏击穿电压的关键。漂移区的长度、浓度、结深以及场极板的长度是影响LDMOS器件源漏击穿特性的主要参数。所以在这里利用半导体工艺模拟软件Athena和Atlas主要详细研究了漂移区的长度、浓度、结深对器件击穿的影响以及场极板对器件击穿的影响,从而得到了700V nLDMOS主要的击穿电压参数。

图1 700V LDMOS剖面图

2 漂移区长度对器件击穿电压的影响

从图1可看出,高压部分主要由NWELL漂移区来承担。漂移区的长度是决定器件击穿电压的关键参数之一,漂移区的长度越长,器件的击穿电压越高,但漂移区的长度太长,导通电阻增大,会使器件的驱动能力下降,所以需设计适当的漂移区长度,而当漂移区浓度适当时,漂移区全部耗尽,大部分漏电压分布在整个漂移区,电场分布较均匀,所以漂移区各处的电场近似相等,根据公式:

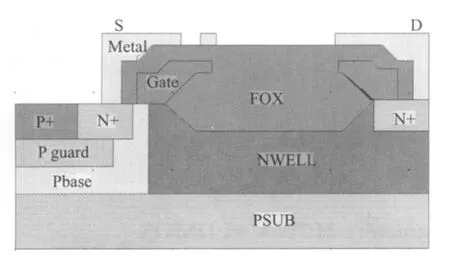

式中Ldrift为漂移区长度, Elat为横向结的平均电场,假设Pbase与NWELL横向结的平均电场Elat为15V/μm[4],根据(1)式,实现700V的击穿电压,初步确定器件的漂移区长度为45μm。在45μm附近进行拉窗口,漂移区的注入剂量为1×1012cm-2,得出长度与击穿电压的关系如图2。从图2可以看出,当漂移区长度较小时,击穿电压随着漂移区长度的增加而变大,最后趋于一定值。产生的原因是:当漂移区浓度适当时,漂移区全部耗尽,大部分漏电压分布在整个漂移区。当漂移区越长时,击穿点由Si-SiO2界面处转移到体内漂移区与衬底界面,因此漂移区与衬底界面平行,缓变结击穿电压将是管子击穿电压的上限[5]。但图2中击穿电压曲线的趋向值却远小于这个上限,这是因为此处模拟的管子的栅比较长,管子处于关态时,栅电压为0,而离其较近的漏端电压却为700V,两者之间的电场强度很高,使得漏区表面在体内达到击穿电压之前已经击穿。所以无限增大漂移区的长度对击穿电压的提升没有意义,只会使漂移区电阻增大。实际芯片中的管子都是采用跑道型结构,因此管子所占用的面积平方倍增加。考虑到模拟的误差,取漂移区的长度为50μm。

图2 击穿电压随漂移区长度变化的曲线

3 漂移区浓度对器件击穿电压的影响

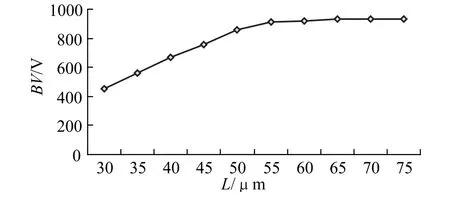

漂移区与衬底之间不再是突变结,而是缓变结,这使得问题的分析更加困难。模拟中,假设沟道注入剂量为1×1012cm-2,漂移区长度为50μm,采用P注入,随着注入剂量的变化,得到击穿电压随漂移区注入剂量的变化曲线,如图3所示。

图3 击穿电压随漂移区注入剂量变化曲线

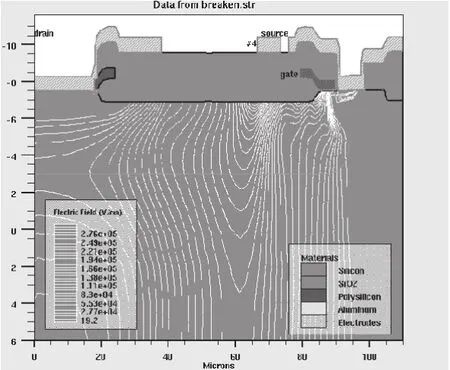

由图3可以看出,随着注入剂量的增加,击穿电压先逐渐上升,在达到一个最优值以后逐渐下降。从图1的剖面图可以看出,此器件的击穿既有可能是Pbase与NWELL形成的结击穿,也有可能是NWELL与衬底形成的结击穿,由二者较低者决定。产生的原因是:当注入剂量很低、漂移区浓度很低时,漏端加的很高的反向电压不但使漂移区全部耗尽,且向漏端延伸,使浓度很高的漏区也耗尽了一部分,此处较高的空间电荷浓度导致了较高的电场强度,很容易发生雪崩击穿,因而降低了击穿电压。注入剂量较低时,漂移区的等压线分布如图4所示,靠近漏区的等压线密度特别高,因而电场强度也非常高,因有场极板的作用,再加上有很厚的场氧,平行板的耐压比扩散结的耐压高很多,击穿点在场极板末端下方的位置,击穿点没向源极移动。

图4 注入剂量较低时漂移区等压线分布

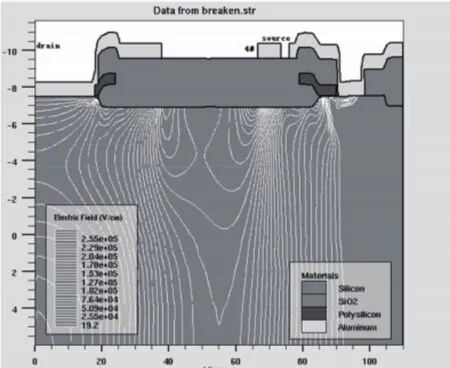

当注入剂量较高时,漂移区浓度很高,漂移区不能完全耗尽,漏端所加的反向电压分布在很短的空间电荷区,耗尽区没延伸至漏端处,在源端处等压线密集,如图5所示,电场的峰值因源极场极板的作用,在场极板下方处,因而击穿点在源极场极板的下方。当注入剂量适当时,漂移区浓度正好使其本身耗尽到漏区边缘,而没耗尽到漏端。电压均匀分布在整个漂移区,如图6所示,此时的击穿电压最高,也就是图3中的实线的峰值。考虑了模拟的误差,所以取漂移区的注入剂量为1×1012cm-2。

图5 注入剂量较高时漂移区等压线分布

图6 注入剂量合适时漂移区等压线分布

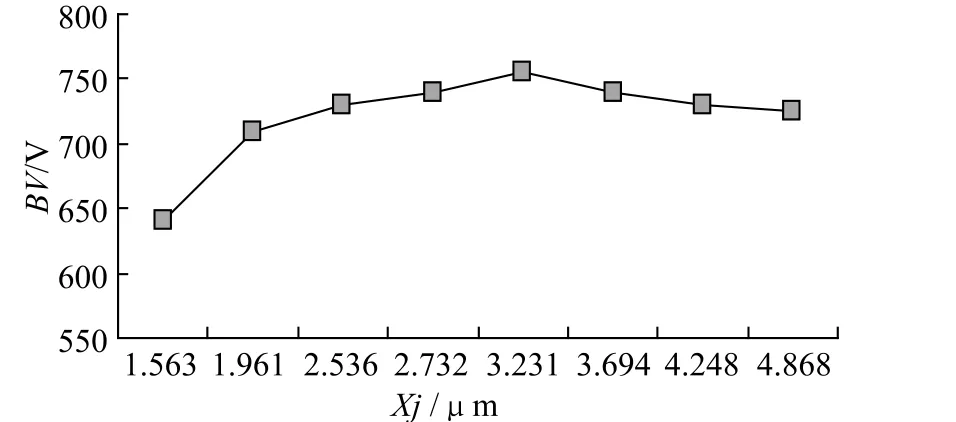

4 漂移区结深对器件击穿电压的影响

当漂移区注入剂量为1×1012cm-2的磷离子时,改变推NWELL的时间,得到了不同的结深,结深与击穿电压变化关系曲线如图7。从图7可以看到,开始时随着漂移区结深的增加,击穿电压增大,当结深超过3.231μm后,随着结深的继续增加,击穿电压略有下降。其原因为,当漂移区结深较小时,场强的最高点在图1所示漏极的左端靠近表面处,随着结深的增加,RESURF效应逐渐明显,缓解了此处的场强,使得场强向体内延伸,击穿电压逐渐趋近最优值,当结深很大时(大于3.231μm)时,场极板下等压线弯曲程度变大,使Si-SiO2界面处的水平方向的场强变大,源极处场极板末端等压线尤为密集,击穿点由漏区左端表面转移到了源极场极板末端表面处。所以选取NWELL推阱时间420min、温度1200℃较合适。

图7 击穿电压与结深的关系曲线

5 场极板长度对器件击穿电压的影响

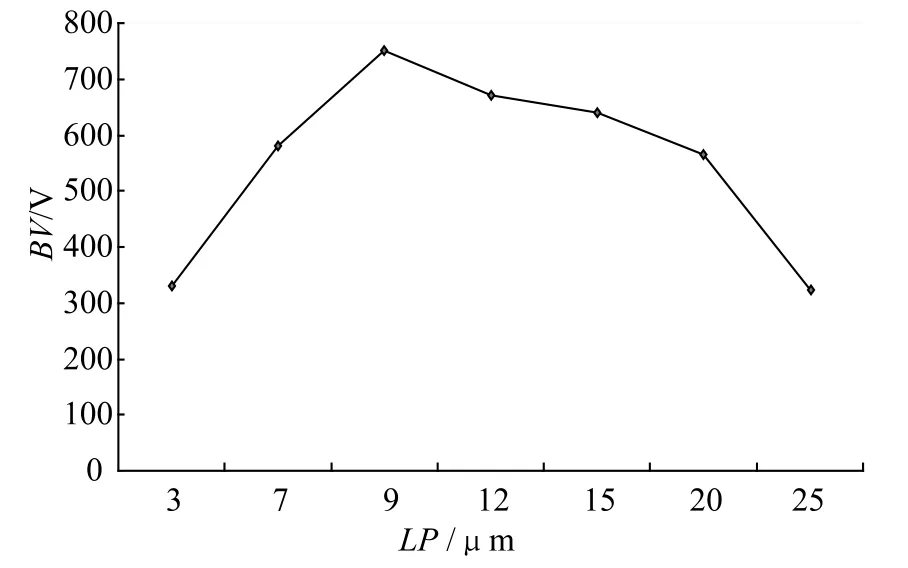

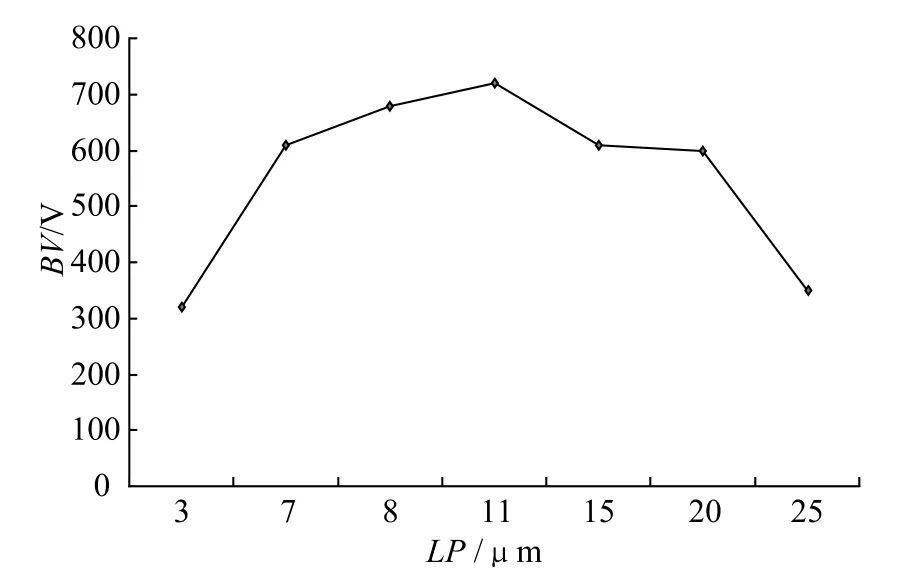

场极板是提高器件耐压的重要手段之一,它对表面电场具有较强的抑制作用,同时场极板的边缘也是击穿的一个影响因素。在漂移区注入剂量为1×1012cm-2、漂移区长度为50μm的情况下,在漏极场极板LP等于12μm时,得到了击穿电压与源极场极板的长度关系曲线,如图8。当源极场极板为9μm时,得到了击穿电压与漏极场极板的长度关系曲线,如图9。从图8、图9中可以看出,当场极板较短时,击穿电压较低,当源极场极板为9μm、漏极场极板达到11μm时,达到图中的最高点,场极板再加长时,击穿电压下降。主要原因是:场极板较短时,漂移区不能完全耗尽,较高的电压分布在较短的空间电荷区上,导致了较高的PN结峰值电场,更严重的是场极板的尖端产生的峰值叠加在PN结的峰值电场上,使器件容易失效。如果场极板过长,漂移区比较容易耗尽,但此时却把场极板尖端引起的峰值电场引到了另一端,在漂移区的模拟中提到漂移区完全耗尽时,另一端有一个峰值电场,这两个峰值电场叠加,很容易超过临界电场,使器件击穿。所以源极场极板为9μm,漏极场极板达到11μm,器件可以承受很高的电压。

图8 击穿电压与源极场极板的长度关系曲线

图9 击穿电压与漏极场极板的长度关系曲线

6 确定最终参数

实践工艺中,对漂移区浓度的控制是通过调节注入剂量和推阱时间来实现的。因此,对于相同的注入剂量推深阱,必然使漂移区浓度降低。由于二者具有相关性,在优化器件性能的过程中,不能简单地将前面曲线中的最优值作为器件的最优参数,经验最优值稍大于此剂量。这一点在剂量与长度的关系上体现得更明显,漂移区长度一定,在某一注入剂量下达到最优击穿电压,增大漂移区长度,击穿电压会升高,但却不是此漂移区长度下的最优值,继续增大漂移区的浓度会得到更高的击穿电压,漂移区长度继续增加,最优击穿电压有一个上限,而这个上限受漂移区结深、浓度和衬底浓度的限制。在漂移区浓度较小时,由于漂移区完全耗尽,同时耗尽了漏区的一部分,漂移区结深越大,极限击穿电压越大;在漂移区浓度较大时,漂移区不能完全耗尽,极限击穿电压由漂移区和P-base的浓度决定,基本上不受结深的影响。随着场极板的位置变化,漂移区的电场分布发生变化,因而影响漂移区的长度、浓度、结深对器件击穿电压的关系。通过上面的分析,很难找出精确的全局最优解,因此只能采用迭代模拟方法搜索出一个能够满足设计要求的次优解。首先将器件各个参数赋值(可以通过建模等方法得到),称之为初始集合,然后每次固定初始集合中的其他变量,优化其中的一个变量,找出此变量的最优值后,将此值代替初始集合的原始值,然后再继续优化其他变量,往返循环几次直到满足设计要求。最终得到击穿电压的参数为:漂移区长度46μm,注入剂量1.2×1012cm-2,在1200℃下推阱430min,结深为3.3μm。漏极场极板的长度为10.5μm,源极场极板的长度为9.5μm。此器件的版图如图10,在CMOS工艺上流片验证得到了器件的击穿电压为700V,满足我们的设计要求。

图10 nLDMOS版图

7 结论

为了不增加器件成本,方便和低压器件集成到一起时实现自主隔离,设计了700V nLDMOS器件的耐压结构。利用专业软件Athena和Atlas 700V nLDMOSFET对器件的耐压结构(漂移区和场极板参数)进行了模拟。结果表明,器件的击穿电压随漂移区长度的增加逐渐上升,最后趋于一个稳定值。击穿电压随漂移区结深的增加先是逐渐上升,然后由于击穿点的转移而略有下降;击穿电压随漂移区浓度的增加先是上升,然后下降。击穿电压随场极板长度先是逐渐上升,然后随着长度的增加而略有下降。最后通过这些参数的优化,利用迭代模拟法搜索出一个满足设计的次优解。

[1] Jongdae Kim, Tae Moon Roh,Sang-Gi Kim, et al. High-Voltage Power Integrated Circuit Technology Using SOI for driving Plasma Display Panels[J].IEEE Transactions on Electron Devices,2001,48(6):1256-1262.

[2] M.R.Lee,Oh-Kyong Kwon,S.S.Lee, et al. SOI High Voltage Integrated Circuit Technology for Plasma Display Panel Drivers[A].Power Semiconductor Device& ICs,ISPSD’99.Proceedings of the 11thInternational Symposium,1999:285-288.

[3] Kenya Kobayashi,Hiroshi Yanagiawa,Kazuhisa Mori,et al..High Voltage SOI CMOS IC Technology for Driving Plasma Display Panels[A].Proceeding of 10thinternational Symposium on Power Semiconductor Device &ICs,ISPSD’98,1998:141-144.

[4] Amato M,Rumennik V. Comparison of Lateral and vertical DMOS specific on – resistance[J].Electron Devices Meeting,31:736-739.

[5] 陈星弼. 功率MOSFET与高压集成电路[M]. 南京:东南大学出版社,1990:289.