ESD保护结构中的SCR设计

黄昀荃,陈 卫

(中国电子科技集团公司第58研究所,江苏 无锡,214035)

1 引言

CMOS集成电路随着量产工艺的进步,器件尺寸不断缩小,以增进集成电路的性能及运算速度,以及降低每颗芯片的制造成本。但CMOS器件由于不断缩小的器件尺寸,使得集成电路对静电放电的防护能力下降很多。就算器件的尺寸不变,因工艺的变化,器件的ESD防护能力也大幅降低;即使把器件的尺寸加大,其ESD耐压度也不一定能得到相应的提升,反而由于器件尺寸增大使得布局面积也相应增大,整个芯片大小也增大,其对静电放电的承受能力严重下降,许多深亚微米CMOS集成电路产品都面临这个棘手的问题。但是,CMOS集成电路对静电放电防护能力的规格却没有变化。

2 工艺的影响

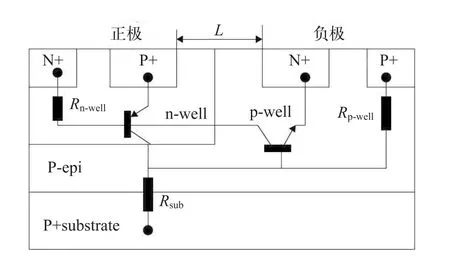

现在工艺中普遍采用的LDD和Silicide等方法,对电路的ESD保护性能带来负面影响。

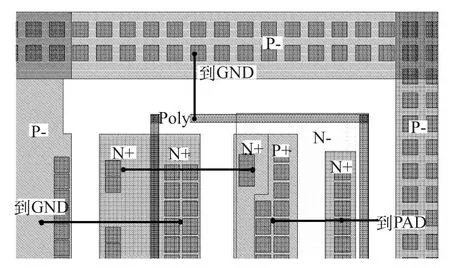

在图1中,NMOS器件有LDD结构,LDD用来减低MOS的漏端在沟道下的电场强度分布,以克服因热载子效应所造成的I-V特性因长时间使用而漂移的问题。但这个LDD结构做在MOS器件沟道的两端,LDD深度只有约0.02μm,这等效于在漏端与源端形成两个“尖端”,ESD放电作用类似于雷击,“尖端放电”的现象便容易发生在LDD这个尖端结构上,NMOS器件很容易便被ESD所破坏,即使NMOS器件在输出设计中拥有很大的尺寸(W/L),其ESD防护能力在HBM测试下仍常低于1000V。

图1 NMOS中的LDD结构

Silicide是0.35μm(含以下)的CMOS标准工艺,主要目的在于降低MOS器件在漏端与源端的串联电阻Rd及Rs。在没有Silicide的CMOS工艺下,N+的阻值约30Ω~40Ω/□,但在有Silicide的工艺下,其阻值下降到约1Ω~3Ω/□,由于扩散层的电阻大幅降低,使得MOS器件的操作速度可以有效提升,因而使CMOS技术可以做到更高频率的应用。Silicide技术在0.35μm(含以下)的CMOS工艺中已属于标准配备。

但当有Silicide的MOS器件被用来做输出级的器件时,由于其Rd与Rs都很小,ESD电流很容易便经由PAD传导到MOS器件的LDD结构,一下子就因LDD做“尖端放电”而把MOS器件破坏掉,因此0.35μm工艺的MOS器件,其ESD防护能力大幅度下滑,制作再大尺寸(W/L)的器件当输出级也无法有效提升其ESD防护能力。

综上所述,随着工艺进步,ESD保护越来越困难,以前的ESD保护电路的效率下降,逐渐难以满足需要。随着设计的日益完善,场管(FOD)、ggNMOS(FPD)、GCNMOS等保护器件的防护能力进一步提高,但仍无法满足更高的ESD需求,这时我们把目光投向了SCR器件。

3 ESD器件I-V曲线

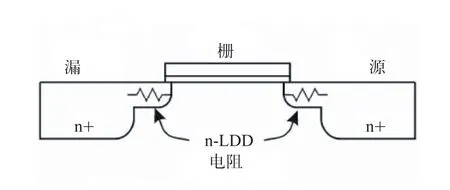

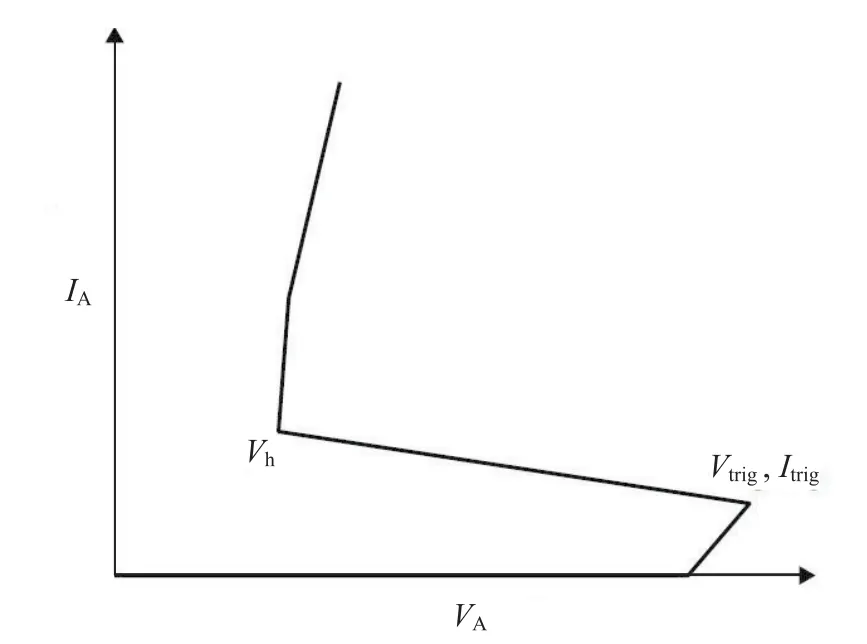

在研究ESD器件前,我们先来关注一下器件的电特性表现,以利于后面说明器件物理表现和对电路工作过程进行分析。两类典型的ESD的I-V特性曲线如图2所示,分别为简单的开启曲线a和折转效应SNAP BACK曲线b,后者是ESD保护器件的工作曲线,其对电流的处理能力更强。

ESD保护器件在曲线中经历几个过程。首先是保护器件处于高阻状态,电路不导通,没有电流通过保护器件。随着电压升高,到达雪崩击穿,是器件的一次击穿,触发了ESD保护器件启动,它的触发电压和触发电流是Vt1和It1。然后器件立即转折进入负阻区,电压大幅降低。保护器件进入低阻状态,电压基本保持在Vh,保持电流Ih大幅增加,形成电流泻放。随着电流和电压的增加,器件到达二次击穿点(Vt2,It2),器件最终失效,节的击穿不可恢复。

图2 两类典型ESD的I-V特性曲线

ESD保护器件性能需要考虑的是减小触发点Vt1,使得触发难度降低;增加It2,即导通状态时加大电流导通能力;另外适当提高Vh,可以提高抗干扰性。

4 SCR电路

4.1 SCR原理

硅控整流器SCR器件在单位布局面积下具有很高的ESD防护能力。利用这种特殊器件,CMOS IC的ESD防护能力能够在只占用到较小的布局面积下即可有效地大幅提升,而不需要用到工艺上的额外处理。其作为一种被广泛认识的晶闸管器件用于功率器件中,它有从极高阻到极低阻的切换能力。所以合理设计的SCR是非常高效的ESD保护器件。

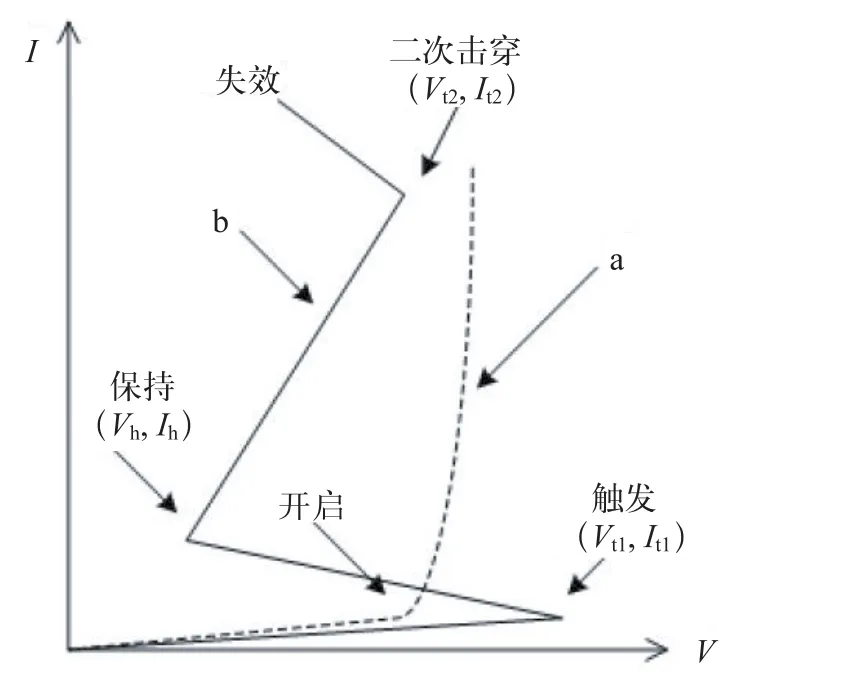

图3是一个简单的横向SCR剖面图。其中n-well中的P+是正极,p-well中的N+是负极,从正极到负极有P+、n-well、p-well、N+形成的PNPN结构。SCR可以看成两个三极管,T1管是PNP管,E、B、C分别是P+、n-well、p-well,T2管是NPN管,E、B、C分别是N+、p-well、n-well。使用时负极接地,正极接ESD电压。

图4是I-V曲线。当电压V超过Vtrig后,PNP的EB节正向导通,PNP打开,电流通过PNP流入p-well,NPN打开。然后,流过n-well的电流提供了PNP的正向偏置,正极电压不再需要提供给PNP偏置用,所以V减小,结果进入负电阻区域。接着PNP提供了大量电流供NPN正向偏置,V保持在最小电压Vh。横向PNP和NPN的基极B的宽度也就是正负极间距L,决定了Vh。

图3 简单横向SCR剖面图

图4 I-V曲线

SCR的等效电路图表明,SCR进入锁定状态时必须满足βnpn·βpnp≥1。在SCR的其他重要参数中,Itrig受Rp-well影响,Vh依赖于L和Rn-well(一般在2V~5V,亚微米在1V~2V)。

在SCR处于导通状态时,和导致CMOS Latchup问题的结构相同,电阻大约可到1Ω,是理想的ESD防护器件,其能在最小的布局面积下提供最高的ESD防护能力。在我们一般的ESD保护器件的SCR设计中,在低电流状态时,NPN的增益大于PNP,并且NPN的打开比PNP更易实现。Vtrig是受n-well和衬底的p-well的雪崩击穿电压决定的,大约30V~50V,而Itrig如前所述。我们可以通过减小正负极间距L减小Vtrig。SCR的ESD性能在非Silicide工艺下好于Silicide工艺下,但由于性能非常优异,以至于这个差别并不重要了。

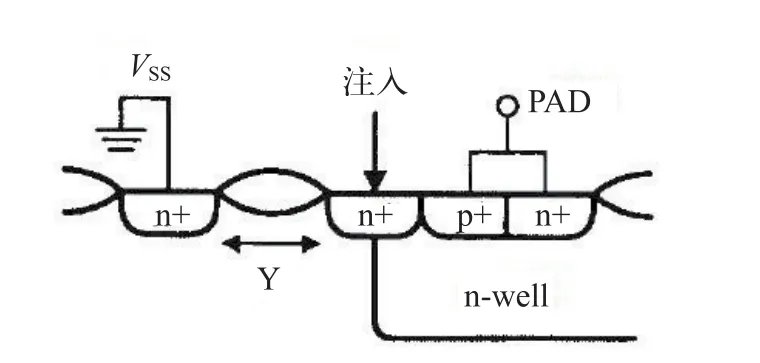

4.2 MLSCR电路

SCR的Vtrig等效于CMOS工艺下n-well与P-substrate的节击穿电压。由于n-well具有较低的掺杂浓度,因此其节击穿电压高达30V~50V(依工艺而定)。具有如此高的节击穿电压,使得SCR启动并不容易,修改设计把高浓度注入做在n-well边界的表面,使得节由N-和P-变成N+和P-,击穿电压得到有效降低,这就形成了MLSCR。MLSCR的启动电压Vtrig大概在20V左右,比SCR更易启动。MLSCR剖面图见图5。

图5 MLSCR剖面图

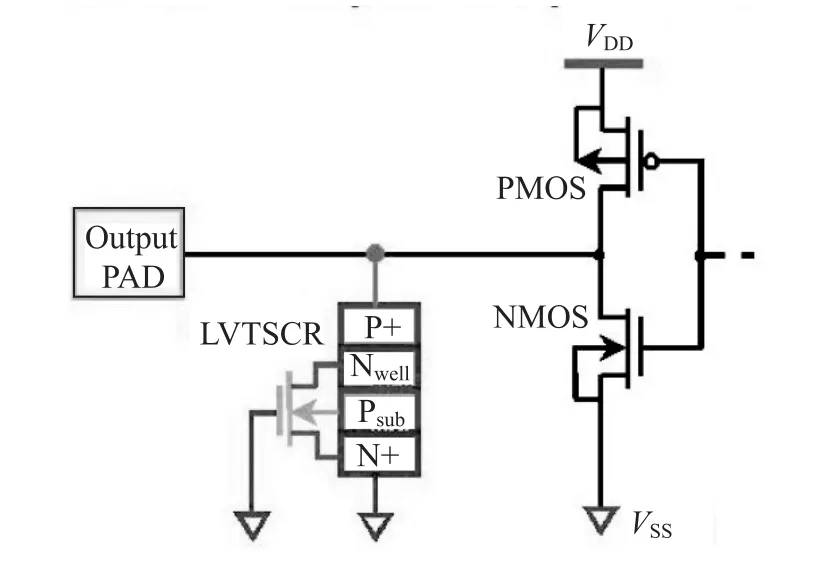

4.3 LVTSCR电路

将MLSCR中的Y部分变成一个薄氧化层的短沟道NMOS器件,便形成了LVTSCR器件。换一种表述方式,用PNPN四层表示SCR,LVTSCR的示意图如图6。LVTSCR器件的导通原理是:当其内嵌的短沟道NMOS器件发生击穿时,引发电流自其漏极流向P-substrate,这会引起电流自n-well流向P-substrate,因而触发了SCR器件的导通。由于NMOS的加入,LVTSCR的Vtrig进一步降低到10V左右,性能得到提高。图7是LVTSCR的剖面图。为了防止LVTSCR器件在CMOS IC正常工作情形下被导通,其内含的NMOS器件的栅极必须要连接到地,以保持该NMOS器件平时是关闭的。LVTSCR器件使得CMOS IC在深亚微米工艺技术下的ESD防护能力得以大幅提升,且不需要额外的工艺处理,但其缺点是不容易设计,要有一定的经验才能够将这个寄生器件的缺点(造成CMOS Latchup)转化成ESD防护上的优势。

图6 LVTSCR示意图

4.4 SCR组合保护电路

4.4.1 组合保护原理

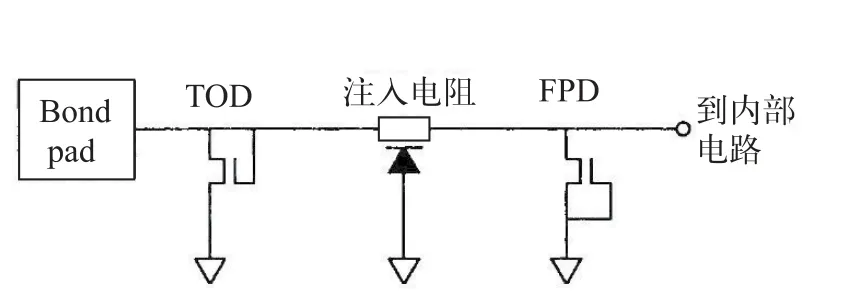

因为SCR器件要到较高电压才导通,在ESD电压尚未升到Vtrig之前,此SCR器件是关闭的,这时SCR器件所要保护的内部电路可能早就被ESD电压破坏了,所以仅仅有SCR保护电路是不够的。SCR作为主要保护电路还需要和二级保护电路相结合才能有效地保护内部电路。以前的ESD保护电路结构有场管(厚氧器件TOD)和栅接地的GGNMOS(利用漏区二极管,也叫场板二极管FPD)以及隔离电阻的组合。电路电压首先使FPD节击穿,ESD电压是通过隔离电阻降压到FPD的,所以TOD上也就是PAD上的电压继续上升,到达TOD触发点使TOD启动,通过能力更强的TOD释放电流,达到保护内部电路的目的。但随着LDD等工艺的加入,TOD-R-FPD的保护电路效率下降,不再使用。

图7 LVTSCR的剖面图

图8 TOD-R-FPD保护电路

SCR加上第二级保护电路,形成SCR-R-FPD组合结构。利用适当的设计,在第二级保护电路未被ESD破坏之前,SCR器件能够被触发导通来排放ESD电流,只要SCR器件一导通,其低保持电压(Vh)便会将ESD电压箝制在很低的电位,从而有效地保护内部电路。但是第二级保护电路需要正确设计才能达到上述目的,另外第二级保护电路会占用额外的布局面积,这使得在pad附近的Layout会变得较复杂。

4.4.2 隔离电阻

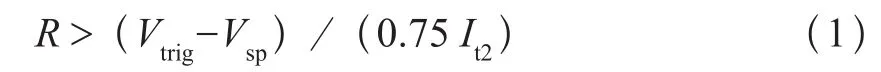

隔离电阻是隔在SCR和FPD之间的电阻,它对FPD起到了保护作用。隔离电阻设计可以遵照以下公式。

R是隔离电阻值,Vtrig是SCR触发电压,Vsp是FPD保持电压,It2是FPD二次击穿电流。

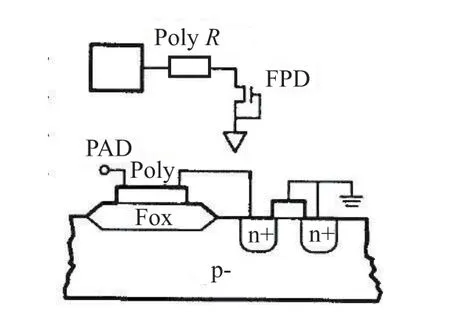

注入电阻通常用来做隔离电阻。但注入电阻也是到衬底的寄生二级管,这个电阻也会发生节击穿从而被损坏。正因为这样,注入电阻必须有较大的面积来实现对自身的保护,并且在电阻上覆盖低浓度的well,以抑制节击穿,这进一步加大了面积。多晶电阻也可以做隔离电阻。多晶热传导效率低,它的热绝缘性容易导致有功耗的情况下损坏,使ESD水平降低。

4.4.3 二级保护电路

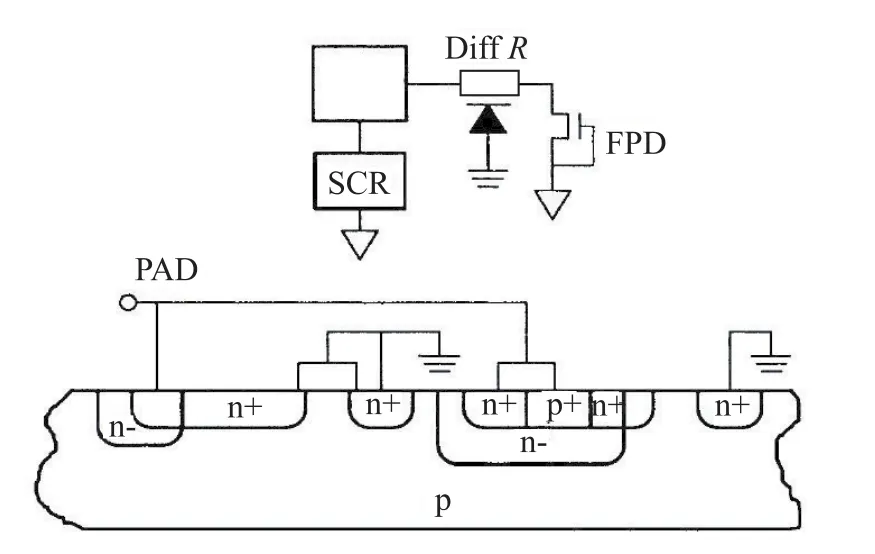

注入电阻DIFF R和FPD组合结构的电路图和剖面图见图9。在此结构中,FPD可以对注入电阻起到保护作用,如果FPD去掉,电流将全部通过注入电阻的二极管节流入衬底。因而注入电阻DIFF R和FPD组合结构保护等级比单纯电阻的保护等级更高。当然注入电阻的尺寸仍对失效等级有影响,但尺寸无需增加太大,需要和FPD能力做适当配合。另外,注入电阻损坏开始发生在电阻体内,不能被电测试方法发现,直到FPD短路才显现,所以注入电阻设计引起的失效等级变化还是比较难以测量的。

图9 注入电阻DIFF R和FPD组合结构的电路图和剖面图

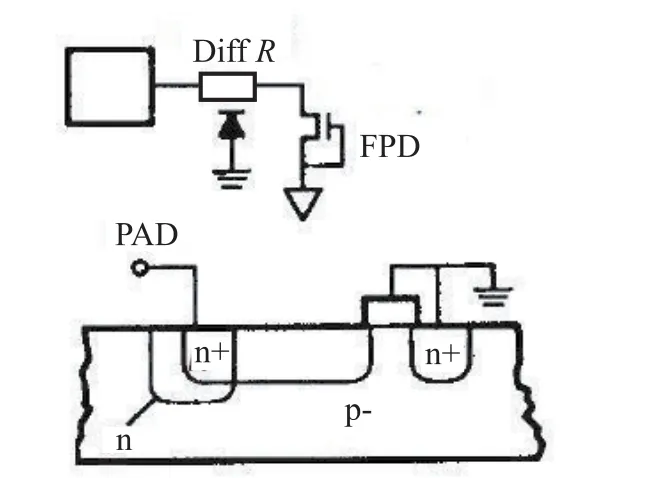

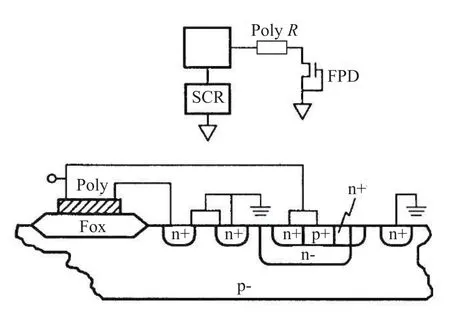

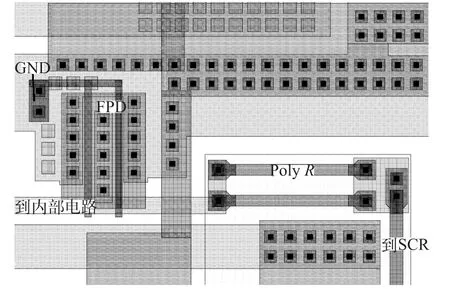

多晶电阻和FPD组合结构的电路图和剖面图见图10。在此结构中,需要解决的是多晶电阻的热损坏问题。另外没有SCR而只看二级保护电路的性能时,有无多晶电阻和FPD一起,ESD性能无明显影响。而多晶电阻太大也对二级保护电路有不利影响。

图10 多晶电阻和FPD组合结构的电路图和剖面图

4.4.4 组合保护电路性能

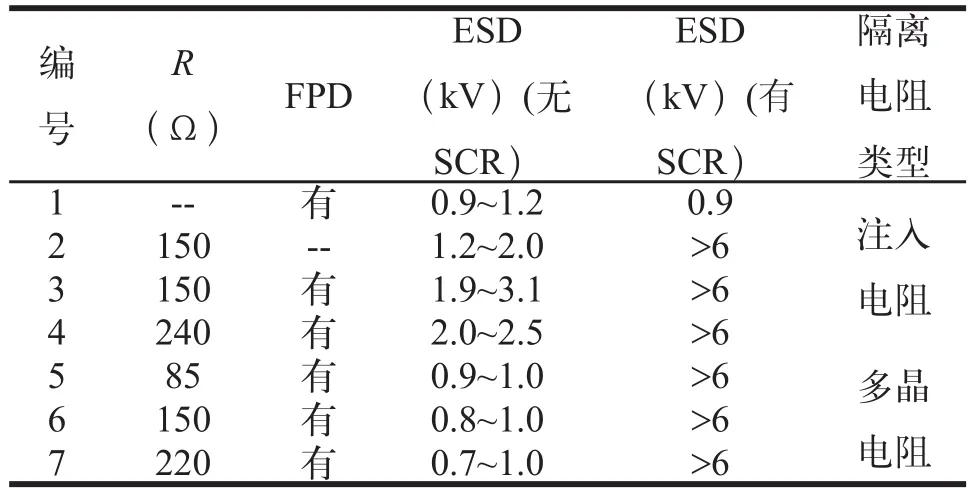

组合保护电路的ESD防护能力较强,除了没有隔离电阻的结构,其他结构的ESD等级都基本大于6kV。从表1的数据可以看出,没有SCR而只有二级电路时,ESD防护能力有限。在加入了SCR的组合保护电路中,一方面二级电路要足以使SCR结构启动;另一方面,由于SCR的启动,二级电路对ESD的贡献相对减弱,但整体的保护能力依然良好。SCR-DIFF R-FPD组合结构的电路图和剖面图见图11。SCR-Poly R-FPD组合结构的电路图和剖面图见图12。

表1 组合保护电路ESD防护能力

图11 SCR-DIFF R-FPD组合结构的电路图和剖面图

图12 SCR-Poly R-FPD组合结构的电路图和剖面图

5 LVTSCR电路设计举例

LVTSCR电路及其组合保护电路的设计需要考虑多方面问题,除了前面叙述的问题,还要考虑到电路以及版图通用性,另外电路需通过设计技巧进一步提升性能。

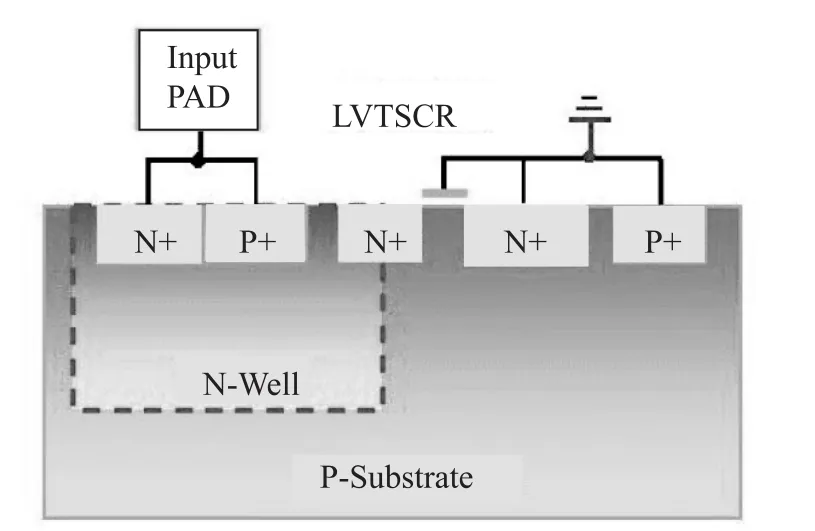

5.1 LVTSCR结构图形调整

先从LVTSCR的结构来看。LVTSCR器件的导通是利用当其短沟道NMOS器件发生击穿时,引发电流自其N+漏极流向P-衬底,再从P+衬底接触流到接地端。因NMOS的漏极跨在n-well和P-衬底,它的电流会引起电流自n-well流向P衬底,也因而触发了SCR器件的导通。

我们看一下普通的ggNMOS击穿过程。首先,大量的正电荷聚集在漏端,一定的正电荷通过漏端和P-衬底之间反偏的PN结转移至P-衬底,这部分正电荷聚集到同为P型材料的P+接触端,转移到地。第二步,聚集到衬底的正电荷,使得与源端的PN结导通,由此导通寄生的三极管。第三步,寄生三极管被打开,大量正电荷通过栅下面的区域迅速由漏端转移到源端。聚集的正电荷得以快速泻放到地。LVTSCR器件的短沟道NMOS器件击穿过程和ggNMOS击穿过程完全一样。

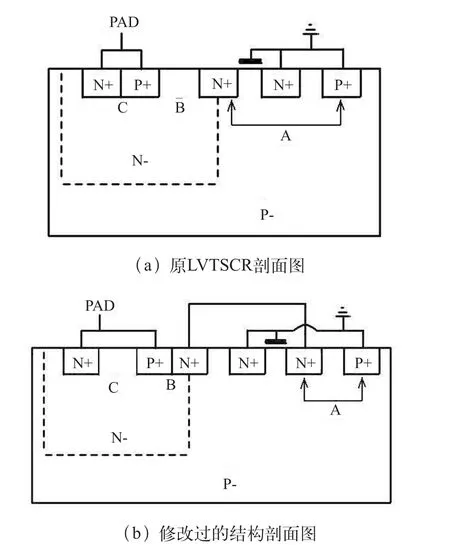

从上面看来,使短沟道NMOS器件更易触发是LVTSCR器件的关键,而NMOS触发关键是“漏极-衬底-接触-地”通路。图13(a)是前面介绍过的LVTSCR剖面图,(b)是修改过的结构剖面图。图中的距离A反映了NMOS的触发能力,图13(b)比图13(a)的A短,更易触发。

图13 修改结构剖面图对比

图13(b)将B处的P+和N+距离缩小到连接在一起,原来图13(a)的P+和N-的节电压减小到图13(b)的P+和N+的节电压,进一步降低了触发电压Vtrig。

由于改变后的保护电路进入低阻态灵敏度很高,抗干扰能力相应下降,保护电路可能在电路正常工作中因为意外因素进入锁定状态,所以在图中C处做了调整,图14增大了Rn-well,使得Vh抬高一些,提高抗干扰性。这个处理会对保护性能有所削弱,但LVTSCR本身性能很好,所以可以接受。图14是修改过后的LVTSCR的版图。

图14 修改后的LVTSCR版图

5.2 二级保护设计

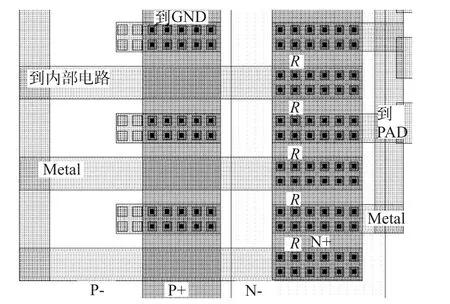

二级保护分两组。一组是多晶隔离电阻和FPD构成的保护电路,主要用于对输入电路的保护,见图15。另一组是注入隔离电阻构成的保护电路,主要用于对输出电路的保护,见图16,由于输出电路本身可以看成FPD,所以也构成了完整的二级保护电路。在输入电路上用多晶隔离电阻,寄生性较小,可以提供更好的RC特性。在输出电路上用注入隔离电阻不用多晶隔离电阻,是因为有功耗发生,避免多晶隔离电阻的热损坏。在输出电路上用注入隔离电阻,要保证输出参数,注入隔离电阻值要小,另外注入隔离电阻本身避免ESD损坏版图尺寸却不能小,所以设计成插指型并联电阻,阻值为R/n,n为并联个数。

图15 多晶隔离电阻和FPD构成的保护电路

图16 注入隔离电阻构成的保护电路

5.3 双向保护

图中对电源方向的保护只采用了反偏的二级管保护,是简化了保护电路的设计,增加可靠性。如果要想进一步增强这个方向的保护性能,把现在对地的LVTSCR结构做个对称的结构,增加一组到电源,器件的类型也都要反过来。这样保护电路就形成了互补式LVTSCR结构,具有了正负双向的近似保护能力,但这样也增加了设计的复杂性和难度。

6 结束语

SCR电路设计有一定的复杂性,工艺关键参数和设计的图形尺寸都会极大地影响电路特性,简单的复制并不一定能达到理想效果。因此,设计时一定要着重考虑特定工艺条件,并且尽量摆脱工艺敏感性。所有这些都需要我们进一步探索,通过不断实践达到更高目标。

[1] Wu Yanhui.ESD protect of PAD design[J].2005.

[2] Ming-Dou Ker.ESD Protection in CMOS Integrated Circuits[M].

[3] Ajith Amerasekera, Charvaka Duvvury.ESD in Silicon Integrated Circuits, 2nd Edition[M].2002.