7~13 GHz宽带高效率驱动放大器设计

豆兴昆 李彬 谭小媛 蒋乐 叶坤

收稿日期:2023-08-22

DOI:10.19850/j.cnki.2096-4706.2024.05.016

摘 要:基于0.25 μm GaAs PHEMT工艺设计了一款7~13 GHz微波单片高效率驱动放大器。芯片采用两级级联拓扑结构,在输入级引入共源并联负反馈结构拓宽工作带宽,同时为兼顾输出功率和效率,在输出级引入等效RC模型拟合输出管芯的最优阻抗。基于等效RC模型,通过采用电抗匹配方式降低输出宽带匹配网络的损耗来实现较高的输出功率和附加效率。实测与仿真曲线吻合度较好,实测结果显示:在7~13 GHz工作带宽范围内,输入驻波比小于1.5,输出驻波比小于1.8,线性增益大于13 dB,3 dB压缩点输出功率大于24 dBm,功率附加效率大于35%,芯片面积为1.8 mm×0.8 mm。

关键词:砷化镓;微波单片集成电路;驱动放大器;功率附加效率;并联负反馈;阻抗匹配

中图分类号:TN722 文献标识码:A 文章编号:2096-4706(2024)05-0073-05

Design of 7~13 GHz Broadband High-efficiency Driver Amplifier

DOU Xingkun, LI Bin, TAN Xiaoyuan, JIANG Le, YE Kun

(China Key System & Integrated Circuit Co., Ltd., Wuxi 214000, China)

Abstract: A 7~13 GHz microwave monolithic high-efficiency driver amplifier based on 0.25 μm GaAs PHEMT process is designed. The chip uses a two-stage cascade topology, introduces a common source parallel negative feedback structure in the input stage to broaden the working bandwidth. In order to take into account both the output power and efficiency in the output stage, an equivalent RC model is introduced to fit the optimal impedance of the output transistor. Based on the equivalent RC model, high output power and power added efficiency are achieved by using a reactance matching topology to reduce the loss of the output broadband matching network. The simulation curves agree well with the measured curves, and test results show that during the bandwidth from 7 to 13 GHz, the input VSWR is less than 1.5, the output VSWR is less than 1.8, the linear gain is more than 13 dB, the 3 dB compression point output power is greater than 24 dBm, and the power added efficiency is higher than 35%, and the chip area is 1.8 mm×0.8 mm.

Keywords: GaAs; MMIC; driver amplifier; PAE; parallel negative feedback; impedance matching

0 引 言

放大器是各類射频模块不可缺少的有源器件,放大器的性能对射频模块的各项指标都有着重要的影响。微波单片集成电路(Microwave Monolithic Integrated Circuit, MMIC)因具有尺寸小、重量轻、可靠性高等优点,目前已在各类射频模块取得了广泛的应用[1-3]。目前常见的MMIC宽带放大器主要包括以下几种类型:平衡放大器、负反馈放大器、有源匹配放大器以及分布式放大器[4]。其中,负反馈放大器具有线性度好、稳定系数高、易于进行宽带阻抗匹配等优点。

本文基于0.25 μm砷化镓赝配高电子迁移率晶体管(Gallium arsenide Pseudomorphic High Electron Mobility Transistor, GaAs PHEMT)工艺设计了一款7~13 GHz微波单片驱动放大器,可应用于发射机输出功率放大器的前级驱动单元,为后级功率放大器提供足够的输入功率[5]。该驱动放大器的设计难点在于实现7~13 GHz工作频带内较高的输出功率和功率附加效率(Power-added Efficiency, PAE)以及较小的芯片尺寸。通过最佳输出阻抗分析、匹配网络设计以及输入级引入负反馈电路,该驱动放大器实现了工作带宽内较高的功率和效率,同时具有简单的电路结构,良好的增益特性和端口驻波等优势。

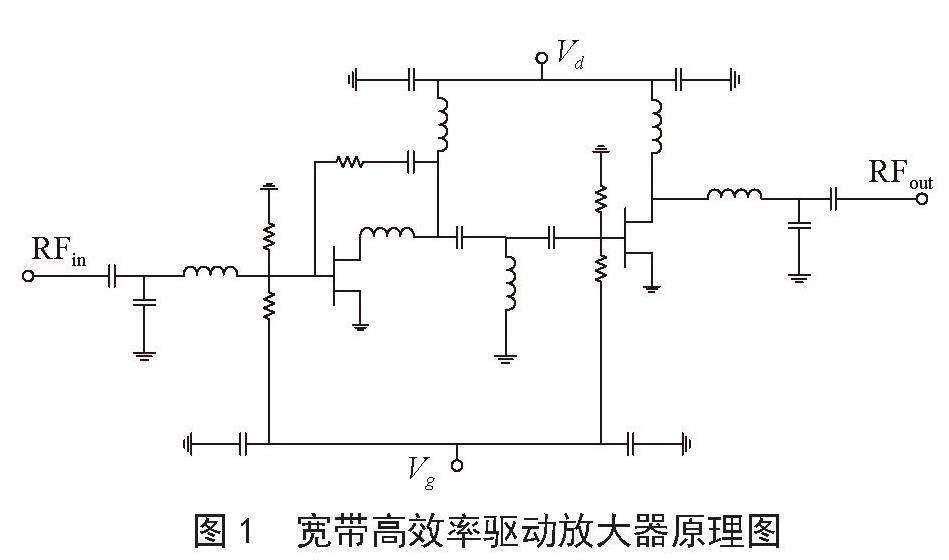

1 电路设计

文中驱动放大器采用两级级联结构,图1为其原理图。电源分别采用Vd = +5 V、Vg = -5 V供电,栅极电压通过芯片内部分压电阻进行调节,采用双电源结构的优势在于不但能灵活调节晶体管的工作状态,同时可以避免采用自偏置结构源极电阻的负反馈影响降低射频输出功率和效率。本文设计的驱动放大器工作在AB类,既可以保证放大器的线性度,又能实现高效率输出。输入级晶体管主要提供适当的增益并调节输入端口的匹配,输出级晶体管主要进行高效率的功率输出。对前级晶体管采用并联负反馈结构,通过对匹配结构以及负反馈的综合调节,牺牲低频增益,改善寄生电容导致的带内增益负斜率下降的问题,从而获得较好的增益平坦度[6]。

图1 宽带高效率驱动放大器原理图

1.1 最佳输出负载阻抗分析

对于工作在线性区的放大器,通过负载线理论获得最佳负载阻抗匹配点是一种良好的设计方法[7]。当有源器件工作在非线性状态时,负载牵引方法将更为行之有效,采用负载牵引方法可以获知器件的功率、效率以及对应的最佳负载阻抗点[8]。

本文设计的驱动放大器工作在非线性状态,采用负载牵引方法进行设计。该0.25 μm GaAs PHEMT工艺的功率密度为0.5 W/mm,根据实际的输出功率(Pout)需求,考虑到匹配网络引入的损耗,末级管芯采用8 μm×100 μm的尺寸。在确定晶体管的直流工作点后,使用负载牵引测试平台对晶体管进行最大输出功率、最高功率附加效率的最佳阻抗点进行测试,表1是10 GHz时最佳功率匹配和最佳效率匹配的负载牵引结果。

表1 10 GHz时负载牵引测试结果

频率/ GHz Pout / dBm 最佳功率

阻抗ZL / Ω PAE / % 最佳效率

阻抗ZL / Ω

10 25.8 17.8 + j*11.3 54.4 14.2 + j*16.5

通常,最佳输出功率和最大功率附加效率對应的阻抗点不完全一致但相近,根据设计目标需要对负载阻抗进行折中选取,实际选取阻抗点如表2所示。

表2 实际选取阻抗点

频率/ GHz 7 10 13

负载阻抗ZL / Ω 21.3 + j*12.2 17.5 + j*11.5 14.3 + j*9.3

Pout / dBm 25.3 25.6 25.6

PAE / % 47 50 46

为了更清晰地表征晶体管的物理特性,简化宽带匹配网络拓扑分析,基于上述实际选取的负载阻抗ZL,根据式(1~3)所示的阻抗变换关系,将串联晶体管等效成图2所示的RC并联输出阻抗模型[9]。RC模型具有一定的物理意义,用于表征具有电流和电压摆幅限制的有源器件,并可以在宽带匹配网络的设计中分析网络拓扑[10]。

(1)

(2)

(3)

式中,γ为负载阻抗等效导纳,G为等效电导,B为等效电纳,ω为10 GHz时对应的角频率,Rp为并联等效电阻,Cp为并联等效电容,根据该并联RC模型可以对匹配网络的性能进行分析。

图2 管芯最佳负载阻抗RC模型

1.2 阻抗匹配

匹配网络是射频电路设计中的关键,良好的匹配网络能够让放大器获得优良的射频性能,保证功率的稳定传输。对于宽带匹配网络,根据Bode-Fano规则,相同的负载条件下,最佳带内反射系数响应Гm和带宽Δω两者之间相互制约[11],1.1节中的晶体管并联RC负载条件下的Bode-Fano约束条件如式(4):

(4)

式中,Δω = ω2 - ω1,ω2、ω1分别为13 GHz和7 GHz时对应的角频率。将式(1~3)所得的Rp、Cp值代入式(4)中,表明7~13 GHz理论上匹配枝节数n→∞时可得到最佳带内反射系数Гm = 0.05。因此,在满足宽带匹配要求的前提下,将放大器的反射系数目标设为Гm<0.2(VSWR<1.5)进行匹配网络设计,可将匹配枝节最简化,通过电抗匹配实现较低的插入损耗。

同理,根据输出级的最佳源阻抗及所需输入功率,对前级晶体管的输出阻抗以及输出级晶体管的源阻抗进行级间匹配,使得前级提供足够的输出功率及增益以推动后一级[12]。最后将前级的最佳源阻抗匹配至50 Ω,通过调节前级输入匹配可以对增益进行优化。

1.3 负反馈共源电路

为了进一步调节放大器的增益等性能,在第一级晶体管漏极和栅极之间引入共源并联负反馈,结构如图3所示。该结构可以使得放大器的输入阻抗和输出阻抗在工作频带内保持相对恒定,既可以提高放大器的线性度,减少失真,降低工艺敏感度,又便于实现增益调节和端口的阻抗匹配[13]。

图3 共源负反馈电路

图4是带有反馈网络的晶体管π型等效电路,忽略器件寄生电抗的影响,可以得到该电路的导纳矩阵[Y][14]:

(5)

式中,Rf为反馈电阻,Cgs、Cgd和gm分别为晶体管栅源电容、漏源电容和跨导系数。反馈电路的核心器件是反馈电阻Rf,Rf基本决定放大器的带宽和增益,其他器件的加入是为了能够得到更好的频响特性。现代射频电路设计中,负反馈网络一般都是通过仿真软件进行优化设计,从而获得理想的效果。实际设计中为得到Rf仿真初值,可在低频段简化分析,忽略电容效应,即Cgs = 0和Cgd = 0,可得:

(6)

由式(6)可导出散射矩阵[S]:

(7)

式中,

(8)

(9)

(10)

(11)

(12)

式中,Z0为系统阻抗。从上式中所示的[S]矩阵可以看出,S11、S21以及S22均与Rf有关。根据放大器增益分配即可反馈电阻初值,实际电路设计中需要考虑Cgs、Cgd的影响,通过调节Rf和Cf的值并引入电抗反馈进行仿真优化,实现良好的端口匹配和增益特性。

图4 π型等效电路

2 电路仿真结果及分析

确定该放大器的级联拓扑结构后,利用仿真软件进行原理图仿真和相应元器件版图仿真替换,替换完成后进行整版电磁仿真。如图5所示,在7~13 GHz工作带宽内的线性增益为14 dB,带内波动0.5 dB;射频输入端口第一级放大器采用共源负反馈结构,具有良好的端口匹配性能,输入驻波低于1.4;输出端口主要进行附加效率和输出功率匹配,输出驻波比最大为1.6。

图5 端口驻波及增益仿真结果

图6仿真结果表明在中心频点10 GHz处,压缩

3 dB点输出功率达到25.3 dBm,功率附加效率为41%;由于不同频点对应的最佳负载阻抗存在差异,在设计过程中将部分频点的实际负载阻抗与最佳负载阻抗进行一定失配,从而实现了整个工作频带内平坦的输出功率,在7~13 GHz内输出功率大于24.5 dBm,附加功率效率高于37%。综上分析,该宽带驱动放大器的电磁仿真性能优良。

图6 压缩3 dB点时输出功率和附加效率仿真结果

3 测试结果分析

图7为该款驱动放大器的实物图,基于Cascade半自动探针台进行在片测试。测试结果如图8所示,在7~13 GHz工作带宽内的线性增益为13.5 dB,输入驻波低于1.4,输出驻波比最大为1.8。增益呈现正斜率,原因在于管芯模型在高频部分寄生参数提取有偏差。

图7 驱动放大器芯片实物图

图8 端口驻波及增益测试结果

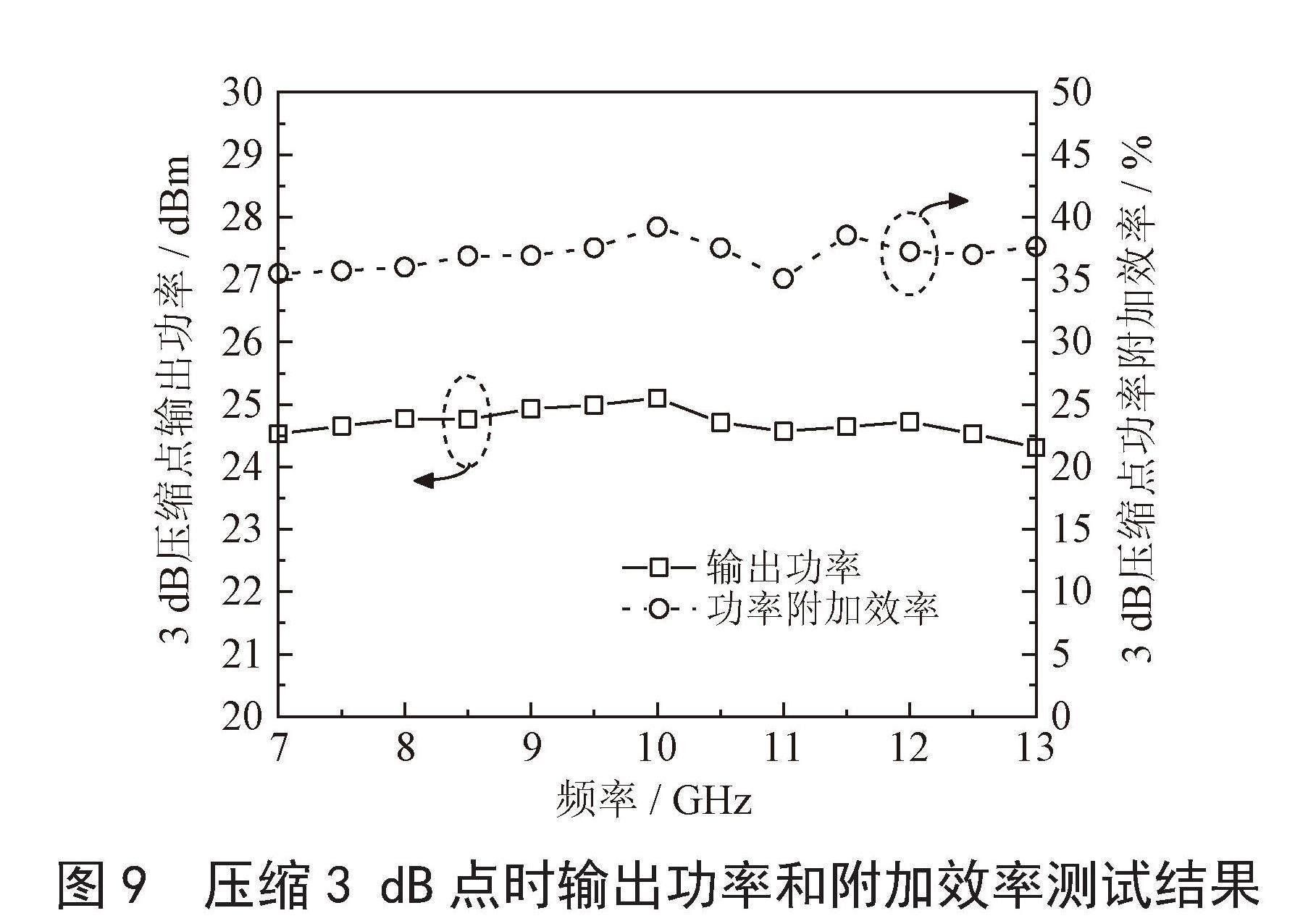

图9结果表明在中心频点10 GHz处,压缩3 dB点输出功率达到25.1 dBm,功率附加效率为39%;在7~13 GHz工作带宽内,增益压缩点3 dB时输出功率大于24.3 dBm、附加功率效率高于35%,与仿真结果相比输出功率和效率均有部分下降,其原因除上述管芯模型偏差问题外,还存在实际输出电路匹配插入损耗大于仿真值的问题。

图9 压缩3 dB点时输出功率和附加效率测试结果

综上,测试结果与仿真数据对比吻合较好,实测与仿真误差较小,芯片射频性能优良。

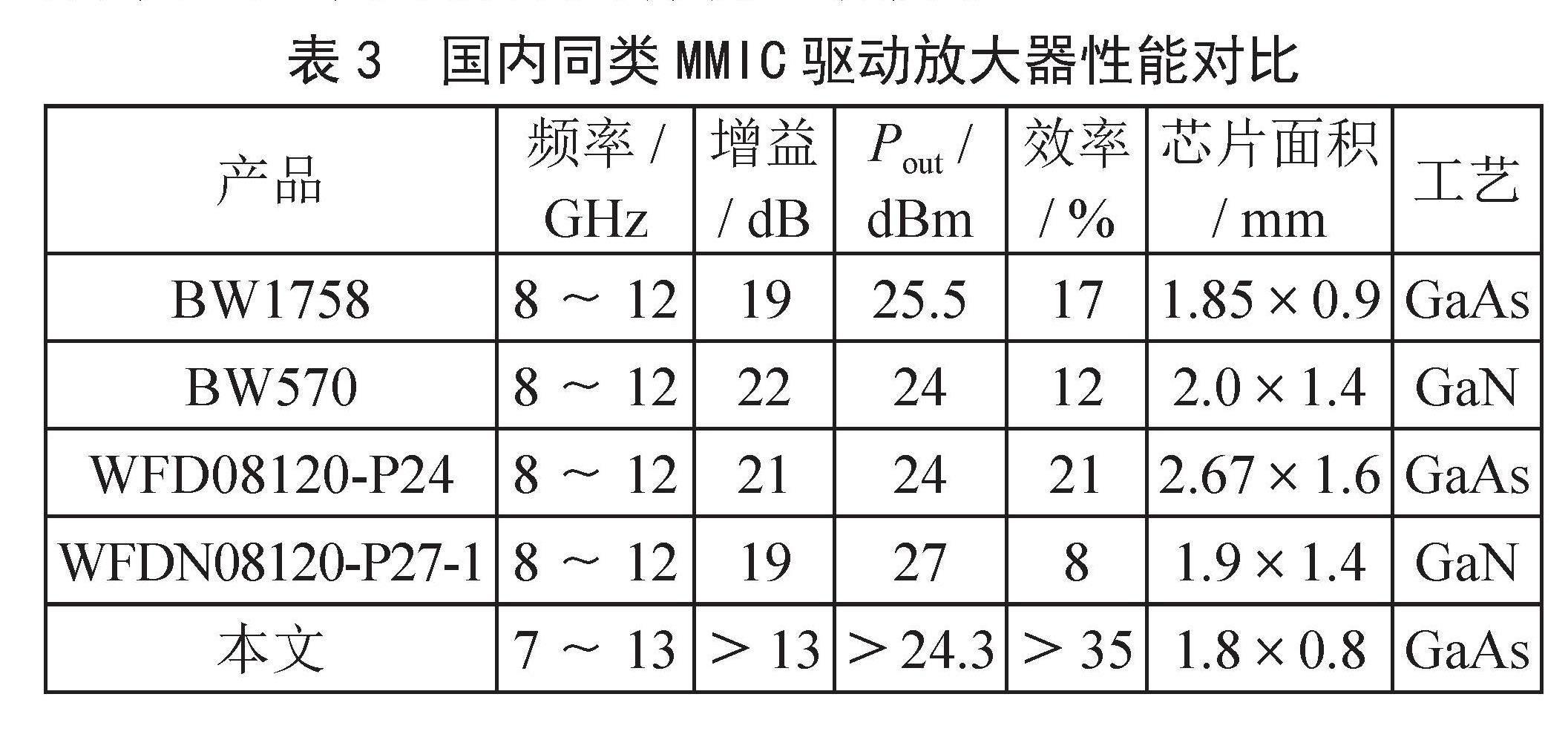

表3将本文设计与国内市场在售MMIC驱动放大器进行了对比,在带宽、效率、芯片尺寸以及工艺成本上,本文设计具有明显优势。

表3 国内同类MMIC驱动放大器性能对比

产品 频率/ GHz 增益/ dB Pout / dBm 效率/ % 芯片面积/ mm 工艺

BW1758 8~12 19 25.5 17 1.85×0.9 GaAs

BW570 8~12 22 24 12 2.0×1.4 GaN

WFD08120-P24 8~12 21 24 21 2.67×1.6 GaAs

WFDN08120-P27-1 8~12 19 27 8 1.9×1.4 GaN

本文 7~13 >13 >24.3 >35 1.8×0.8 GaAs

4 结 论

基于0.25 μm GaAs PHEMT工艺设计了一款7~13 GHz MMIC驱动放大器,该放大器采用两级级联结构,线性增益大于13 dB,3 dB压缩点输出功率大于24.3 dBm,功率附加效率大于35%,在芯片尺寸、效率、输出功率方面具有一定的优势,适用于雷达T/R组件等系统中功率放大器的前级驱动单元。

参考文献:

[1] THOME F,TURE E,IANNUCCI R,et al. Frequency Multiplier and Mixer MMICs Based on a Metamorphic HEMT Technology Including Schottky Diodes [J].IEEE Access,2020,8:12697-12712.

[2] JOHN L,TESSMANN A,LEUTHER A,et al. Broadband 300-GHz power amplifier MMICs in InGaAs mHEMT technology [J]. IEEE Transactions on Terahertz Science and Technology,2020,10(3):309-320.

[3] 井永成,尹军舰,李仲茂,等.2~4 GHz MMIC低噪声放大器 [J].电子设计工程,2019,27(1):75-79.

[4] 朱熔琦,徐锐敏.0.5-18GHz超宽带低噪声放大器单片电路研制 [J].微波学报,2016,32(S1):220-222.

[5] 尹洪浩,冯媛,朱臣伟,等.一种宽带高效率小型化功放模块的设计 [J].电子与封装,2020,20(11):58-61.

[6] 王巍,彭能,王颖,等.3~5GHz超宽带并联负反馈低噪声放大器的设计 [J].微电子学,2011,41(1):10-14.

[7] MAY S,SATOSHI T,TAIZO Y,et al. Rf Power Amplifier for Wireless Communication Apparatus:EP1755214A1 [P].2007-02-21.

[8] 陳晓青,戈硕,时晓航.基于GaN HEMT的S波段大功率内匹配功放管设计 [J].电子与封装,2019,19(7):45-48.

[9] CHEN R T,LI R H,ZHOU S L,et al. An X-Band 40 W Power Amplifier GaN MMIC Design by Using Equivalent Output Impedance Model [J/OL].Electronics,2019,8(1):99[2023-07-20].https://doi.org/10.3390/electronics8010099.

[10] 陈瑞涛. 宽带 GaN 功率放大器 MMIC 研究与设计 [D].浙江工业大学,2019.

[11] RHEA R .The Yin-Yang of Matching: Part 2—Practical Matching Techniques [J].High Frequency Electronics,2006:28-40.

[12] 徐鼎,陈晓娟,胡俊,等.9~15 GHz GaAs MMIC宽带高效率功率放大器 [J].电子设计工程,2021,29(1):24-29.

[13] 马翠红,靳伟超,陈宇擎,等.基于ADS宽带微波低噪声放大器设计与仿真 [J].现代电子技术,2019,42(15):170-174+180.

[14] BAHL I J. Fundamentals of RF and Microwave Transistor Amplifiers [J].Microwave Journal,2010,53(1):146.

作者简介:豆兴昆(1991—),男,汉族,江苏南京人,工程师,研究生学历,研究方向:微波单片集成电路设计。