基于FPGA软件安全性的HDL编码规范分析与研究

曹明 姜宗维 李敬磊

收稿日期:2023-09-01

DOI:10.19850/j.cnki.2096-4706.2024.05.019

摘 要:随着FPGA的广泛应用,FPGA的运行代码的安全性也越来越重要。文章从HDL编码的角度,研究了影响FPGA软件功能安全性的几个重要因素,分析了信号跨时钟域处理、状态机设计、信号毛刺等因素在编码阶段对软件安全性的影响,并提出了对应的防范措施;形成了基于FPGA软件功能安全性的HDL编码和设计规范,为规避在编码阶段引入软件功能安全性问题提供了一定的依据和参考。

关键词:FPGA;HDL;安全性;编码规范

中图分类号:TN79 文献标识码:A 文章编号:2096-4706(2024)05-0085-04

Analysis and Research on HDL Coding Specification Based on FPGA Software Security

CAO Ming, JIANG Zongwei, LI Jinglei

(The 5th Electronics Research Institute of Ministry of Industry and Information Technology, Guangzhou 510610, China)

Abstract: With the wide application of FPGA, the security of FPGA running code is becoming more and more important. From the perspective of HDL coding, this paper studies several important factors that affect the functional security of FPGA software, analyzes the influence of signal across clock domain processing, state machine design, signal glances and other factors on software security in the coding stage, and puts forward the corresponding preventive measures. The HDL coding and design specification based on FPGA software functional security is formed, which provides a certain basis and reference for avoiding the problem of software functional security introduced in the coding stage.

Keywords: FPGA; HDL; security; coding specification

0 引 言

目前,FPGA器件已广泛应用在雷达、导弹、武器、航空、航天等国防领域,其安全性关乎着整个型号装备的质量好坏。除了FPGA器件本身的安全性外,运行的软件代码的安全性直接影响着FPGA软件的功能。因此,研究FPGA软件代码设计的安全性编码规范,规避在编码阶段引入的安全性问题,是十分有意义和必要的。

作者借助单位多年来开展软件测评积累的FPGA软件缺陷库分析了影響FPGA软件安全性的问题缺陷,归纳总结出信号跨时钟域、状态机设计、信号毛刺等方面的主要问题缺陷。本文将从这几个方面入手,分析影响FPGA应用软件功能的主要安全因素,然后从HDL编码方面提出防范措施,并形成基于FPGA软件安全性的HDL编码和设计规范,从而提高FPGA软件的安全性。

1 信号跨时钟域

1.1 影响安全性因素

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态[1]。当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。FPGA器件中包含了大量的触发器资源,主要用于数据的采集,只有当输入数据满足器件本身的建立/保持时间时,数据才能够正确被采集,否则会出现亚稳态,导致采集的数据错误。FPGA软件一般存在多个时钟域,由于各个时钟间的时序不同,经常会出现信号跨多个时钟域传输时建立/保持时间不满足的问题,从而导致信号在多个时钟域间传输错误,出现亚稳态,影响FPGA软件的安全性。

信号跨时钟域是指信号在不同时钟域间传输的情况,主要包括外部输入的异步信号以及内部跨时钟域传输的信号,主要分为单比特数据和多比特数据。

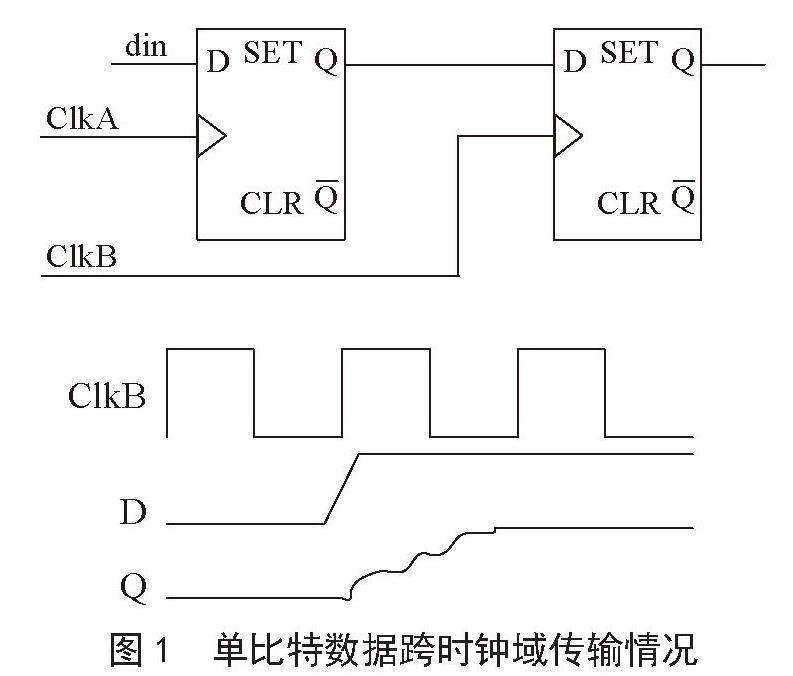

1.1.1 单比特数据跨时钟域传输

单比特数据跨时钟域传输情况如图1所示。当数据从A时钟域传输至B时钟域时,信号的建立/保持时间不满足要求时,在B时钟域数据采集时,会出现亚稳态,采集的数据值不定,可能为0或1,从而影响数据传输的正确性。尤其当传输的数据为跳变信号或者在B时钟域进行信号的沿操作时,会造成功能逻辑错误。

图1 单比特数据跨时钟域传输情况

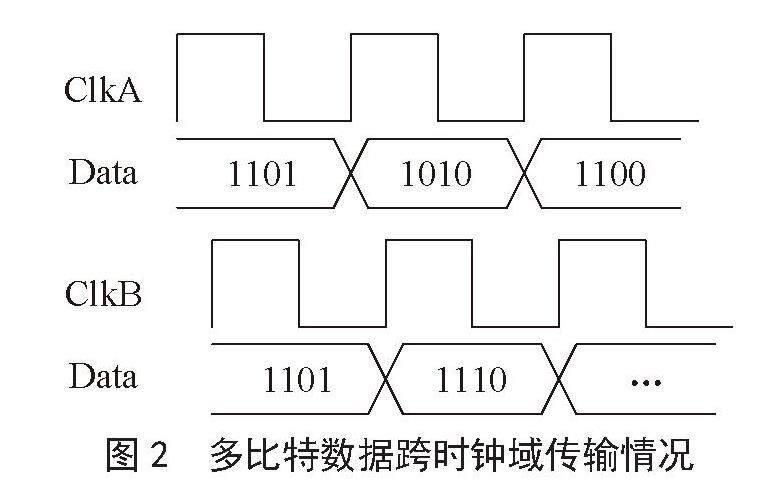

1.1.2 多比特数据跨时钟域传输

多比特数据跨时钟域传输情况如图2所示。多比特数据由于每比特信号在布局布线时的传输线路不同,造成到达B时钟域触发器的时延不同。因此,当多比特数据在B时钟域进行信号汇聚时,可能会导致采集的多比特数据信号值错误,从而造成功能逻辑错误。

图2 多比特数据跨时钟域传输情况

1.2 防范措施

为保证数据在多个时钟域间传输的正确性,在HDL编码时通过信号的同步处理[2]来提高FPGA软件的安全性。

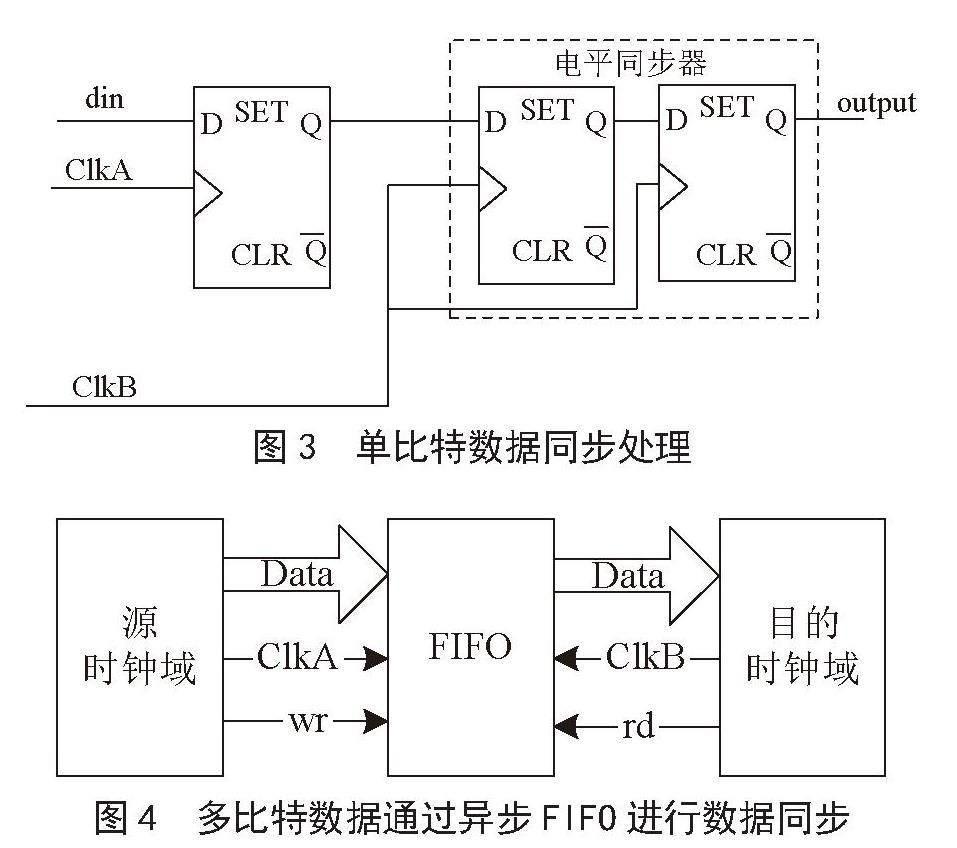

1.2.1 单比特数据跨时钟域同步

单比特数据跨时钟域传输时可采用图3中的电平同步器设计[3],在目的时钟域通过打两拍同步的操作实现信号的正确采集。HDL编码时需要注意,单比特数据一般包括缓变的电平信号以及有脉宽限制的脉冲信号,对于脉冲信号的跨时钟域传输,需要考虑从快时钟域到慢时钟域,信号脉宽小于慢时钟周期时,会导致信号丢失的情况,此时需要在快时钟域对信号进行展宽,再送入目的时钟域进行打两拍同步处理。

1.2.2 多比特数据跨时钟域同步

多比特数据跨时钟域传输时,由于每个信号经过布局布线后传输时延不同,因此不能够简单通过打两拍实现数据同步。对于多比特数据跨时钟域传输时,一般通过以下方式实现同步:

1)使用异步FIFO [4]。如图4所示,对于多比特数据,一般通过FIFO将两个时钟域的数据进行隔离,通过源时钟域将数据写入FIFO,通过目的时钟域将数据从FIFO读出。HDL编码时,需考虑FIFO读写时钟的速率以及FIFO存储深度,以保证数据不会丢失。

图3 单比特数据同步处理

图4 多比特数据通过异步FIFO进行数据同步

2)使用格雷码。由于格雷码相邻两个状态之间只有单比特信号发生跳变,其余比特信号不变,因此降低了多比特信号跨时钟域传输的风险。HDL编码时,如果数据变化状态为2的N次幂,且状态变化连续时可以考虑使用格雷码。

3)使用握手信号[5]。源时钟域发送数据时,同时发送握手信号至目的时钟域,目的时钟域接收到握手信号后,开始接收数据,并在数据接收完成后发送回馈信号装至源时钟域,源时钟域接收到回馈信号后,停止发送数据。使用握手信号,可以保证数据正确传输,但需要的时序开销也较大,HDL编码时需综合考虑。

4)将多比特信号转换为单比特。譬如在源时钟域有a_en和b_en信号需要传输至目的时钟域,HDL编码时,可以将两个信号通过ab_en=a_en&b_en合并为单比特信号ab_en后,在目的时钟域按照单比特信号进行同步处理。该方式适用于多个比特信号之间逻辑关系依赖性较强,且可以通过运算符合并为单比特信号的情况。

多周期路径同步。多周期路径同步是一种通用的安全传递多比特跨时钟域信号技术。多周期路径同步是指在传输非同步数据到目的时钟域时同步传输一个同步的控制信号,数据和控制信号被同时发送到目的时钟域,同时控制信号在目的时钟域使用两级寄存器同步到目的时钟域,使用此同步后的控制信号来加载数据,这样数据就可以在目的寄存器被安全加载。多周期路径同步常用于总线数据在不同时钟域间的传输,HDL编码时,需要保证源时钟域内控制信号有效期间,数据不会发生变化,从而在目的时钟域采集数据时,数据不会在目的时钟域采样沿发生变化,从而有效地避免了数据路径亚稳态的发生。

2 状态机设计

2.1 影响安全性因素

状态机通常是表示有限个状态以及在这些状态之间的转移和动作等行为的数学计算模型。如图5所示,FPGA软件中经常会通过设计状态机来实现工作状态的切换。如果状态机发送误跳转或进入非法状态,将会导致FPGA软件功能失效,进而影响FPGA软件的安全性[6]。其影响软件安全性的因素主要有:

1)状态机未设置初始状态。上电后,狀态机未设置初始状态,导致上电后FPGA软件工作状态不定,影响FPGA软件安全性。

2)状态机存在冗余状态或死锁环。如图6所示,上述两个状态机设计中,存在冗余状态S4以及死锁环S4<->S5,当状态机误跳转到冗余状态或死锁环中,将无法跳转回正常状态,导致FPGA软件功能失效。

3)采用组合逻辑实现状态机跳转。采用组合逻辑来实现状态机跳转,尤其当综合出现锁存器时,容易受到毛刺信号影响,导致状态机发生误跳转,影响FPGA软件安全性。

4)状态机未设置为安全模式。目前,各FPGA厂商支持综合时将状态机设置为安全模式,从而保证当状态机跳转到未定义的非法状态时,能够重新跳回到已知的状态。当未设置为安全模式时,在复杂电磁环境以及SEU环境下,状态机会出现非法状态,此时FPGA软件无法从非法状态跳回到已知状态,导致FPGA软件功能失效,影响FPGA软件安全性。

图5 状态机跳转示意图

(a)冗余状态S4 (b)死锁环S4<->S5

图6 状态机存在冗余状态和死锁环

2.2 防范措施

针对以上影响安全性因素,为提高FPGA软件安全性,状态机设计时一般要遵循以下编码规范[7]。

1)状态机在上电后应进行初始化,确保上电后状态机处于合法的初始状态。HDL编码时,通常将状态机加入复位逻辑中,保证状态机上电复位后处于明确的预期状态。

2)状态机状态定义时,应确保不存在无效的冗余状态,状态跳转时不存在死锁的情况。HDL编码时,不定义和声明非必要的冗余状态,避免出现死锁环逻辑。

3)状态机跳转时,避免出现毛刺引起的误跳转。HDL编码时,宜采用时序逻辑来实现状态机跳转,从而降低毛刺的风险[8]。

4)状态机设计时,应补全case语句的default或others分支,并且通过开发工具设置或约束状态机为安全模式,从而保证出现非法状态时,能够跳回到有效状态,提高状态机的安全性。

3 信号毛刺

3.1 影响安全性因素

信号毛刺主要是由于竞争冒险产生的。信号经由不同的路径传输到达电路中某一汇合点的时间有先有后,称之为竞争。由于竞争现象引起电路输出发生瞬间错误的现象,称之为冒险。如图7所示,发生冒险时,往往会出现一些错误的尖峰信号,这些尖峰信号就是毛刺。

图7 信号毛刺

当出现毛刺时,如果FPGA电路对毛刺敏感,则会导致FPGA软件功能出现错误,从而影响FPGA的安全性。影响FPGA软件安全性的毛刺信号主要包括以下几方面:

1)通过IO端口引入的外部毛刺信号。此类毛刺信号由FPGA外部器件产生,本身无法消除,只能通过电路设计减少毛刺信号的影响。

2)内部产生的毛刺信号。此类毛刺信号由FPGA器件内部产生,由于信号在FPGA的内部走线和通过逻辑单元时造成的延迟不同,在多路信号变化的瞬间,组合逻辑的输出会出现毛刺信号。

3.2 防范措施

为了降低毛刺带来的风险,HDL编码时要遵守相应的编码规范,以减少毛刺信号对FPGA软件安全性的影响[9,10]。

1)外部输入的信号进行同步处理。利用D触发器输入端对毛刺不敏感的特点,HDL编码时,对外部输入的信号进行同步处理,从而减少毛刺信号的影响。

2)尽量采用时序电路来实现逻辑功能。由于组合逻辑容易出现竞争冒险,导致毛刺出现,而时序电路在时钟沿有效时进行逻辑操作,对毛刺不敏感。因此,HDL编码时,在FPGA资源允许的情况下,尽量采用时序电路来代替组合逻辑,从而降低毛刺带来的风险。

3)应避免出现毛刺敏感电路。HDL编码时,使用组合逻辑时应避免出现锁存器、组合逻辑环等敏感电路,譬如if语句应补全else分支,case语句应补全default分支;组合逻辑编码时,应避免输出信号反馈至输入,导致出现组合逻辑环。

4)通过滤波电路对毛刺信号进行滤除。HDL編码时,对关键信号设计滤波电路,将小于滤波宽度的毛刺信号滤除掉,保证信号采集的正确性。

4 结 论

影响FPGA软件安全性的因素较多,本文从信号跨时钟域、状态机设计、信号毛刺等方面分析了其对安全性的影响,并从HDL编码方面提出了防范措施,形成了HDL编码规范,从而能够在设计阶段对HDL编码提供参考,有效规避可能出现的FPGA软件安全性问题,达到提升FPGA软件质量的目的。

参考文献:

[1] 祝宇,董冠涛,张硕.FPGA软件亚稳态处理技术研究 [J].中国检验检测,2020,28(3):14-17.

[2] 宋文强,胡毅.FPGA跨时钟域信号同步设计方法研究 [J].单片机与嵌入式系统应用,2018,18(9):24-27+81.

[3] 贾永兴,杨宏,刘文慧,等.基于国产FPGA的网络平台跨时钟域设计方法 [J].通信技术,2021,54(10):2447-2450.

[4] 游斌相,廖育富,任午龙,等.FPGA在数据重排中的跨时钟处理 [J].火控雷达技术,2021,50(3):59-63.

[5] 黄琳,王新,胡成辉.基于FPGA的异步跨时钟域设计 [J].山西电子技术,2020(1):76-78.

[6] 丁宗杰,门永平,白正尧,等.FPGA状态机综合可靠性探究 [J].空间电子技术,2021,18(1):23-27.

[7] 杨亮,李祁.基于三模冗余架构的航天器FPGA可靠性设计 [J].计算机测量与控制,2019,27(12):244-248.

[8] 于潇,刘文红,赵静,等.基于航天系统的FPGA可靠性安全性分析方法研究 [J].中国检验检测,2021,29(2):14-15+36.

[9] 何伟,张玲.消除CPLD/FPGA器件设计中的毛刺 [J].重庆大学学报:自然科学版,2002(12):69-73.

[10] 中央军委装备发展部.军用可编程逻辑器件软件Verilog语言编程安全子集:GJB 10157-2021 [S].北京:国家军用标准出版发行部,2021.

作者简介:曹明(1989.08—),女,汉族,河南开封人,工程师,研究方向:FPGA测试。