ABF 塑封基板叠孔的高可靠结构设计

葛一铭,谢爽,吕晓瑞,刘建松,孔令松

(北京微电子技术研究所,北京 100076)

0 引言

军用塑封器件产品需要在大温差、强机械振动、高辐照等严酷环境下使用,温差引起的热胀冷缩效应导致有芯一体化塑封基板不同材料之间发生热失配,基板内部产生内应力,进而导致基板出现翘曲变形、塑封体分层、叠层铜过孔开裂等可靠性问题[1-4]。

塑封基板在封装过程中产生内应力的主要原因有2 个:1)塑封料在高温液化及再固化过程中产生收缩,不同材料的热膨胀系数(CTE)存在差异,导致在此过程中产生内应力;2)在温度变化的条件下,不同材料间因CTE 不同产生热失配,进而产生内应力。内应力过大会引发封装结构的薄弱部位产生裂纹、翘曲等可靠性问题[5-7]。国内外学者针对塑封基板结构的可靠性开展了大量研究,NAGAOKA 等人[8]通过黏弹性分析来预测叠层过孔的疲劳寿命,对2 种树脂材料的8 种堆叠过孔结构进行了热循环实验、弹性分析和黏弹性分析,结果表明,黏弹性分析结果与热循环实验结果一致。孙宏超等人[9]对盲孔孔内镀铜与孔底连接盘分离的失效模式进行分析,找到引发失效的主要原因,并提出了可行的改善措施,同时还制定了1 种有效监控与评价盲孔可靠性的方法。TOK 等人[10]针对嵌入铜合金热块结构的新型塑料球栅阵列(PBGA)封装在温度循环过程中的过孔开裂问题,对不同的过孔填充材料和过孔尺寸展开研究,证明了嵌入铜合金热块结构对封装可靠性有负面影响。LI[11]提出了1 个简单的热过孔设计分析模型,设计参数包括孔径、间距、镀层厚度和过孔内填充材料的空隙率,并使用热阻作为目标函数,对设计参数进行优化,将分析结果与有限元模型进行关联,可作为封装中的热通道设计指南。KOBAYASHI 等人[12]建立了通孔开裂的失效模型,并采用几种热循环条件对PBGA 封装进行了评估,结果表明,可以用修正的Coffin-Manson 方程模拟通孔的疲劳失效。GOVAL 等人[13]讨论了金属化孔(PTH 孔)在温度循环应力作用下的可靠性,采用仿真建模和实验验证的方法研究了材料、工艺和设计对通孔基板裂纹的影响。LEICHT 等人[14]提出了1 种弯曲疲劳可靠性测试模型,研究连接到PCB 上的球栅阵列封装的机械弯曲疲劳问题,该方法考虑了疲劳断裂形态及其与焊点位置和裂纹扩展速率的关系。LI 等人[15]研究了无芯倒装芯片封装中C4 凸块开裂的可靠性问题,以及C4 凸块的几何形状、层压板材料性能和其他形状因素对其疲劳性能的影响,并建立了仿真模型,用于预测无芯倒装芯片封装中C4 焊点的疲劳情况。

现有的研究大多基于工艺实验及传统的整体建模分析方法,本文主要研究ABF 塑封基板的高可靠结构设计,针对军用塑封倒装焊结构基板的布线过孔结构进行热力耦合仿真分析,并采用子模型法来解决仿真结构中的跨尺度问题。本文分析了叠孔位置、叠孔层数、芯层厚度、布线长度对器件级封装与温度循环可靠性的影响,总结了塑封基板的叠孔结构设计要求,通过对ABF 塑封基板叠孔进行优化设计,可以降低生产成本,提高生产效率,有助于提高产品的可靠性和性能,为增强型有芯一体化塑封基板的布线层结构设计提供有效指导。

1 ABF 塑封基板叠孔可靠性仿真

为实现对叠孔可靠性的有效预测,节约实验成本,本文基于Ansys 有限元分析软件对典型的ABF 塑封基板的温度循环疲劳寿命进行仿真分析。分析过程中主要使用了瞬态热学模块、瞬态结构力学模块及疲劳分析模块。

1.1 大尺寸跨尺度结构仿真建模

常规的塑封有芯基板的叠孔尺寸较小,一般为微米级,芯片及塑封基板的整体尺寸为毫米级。采用子模型方法可以有效解决塑封基板整体模型及叠孔的跨尺度问题,在保证计算精度的同时大幅减少计算时间,因此本研究采用整体模型与子模型相结合的建模方法进行分析。

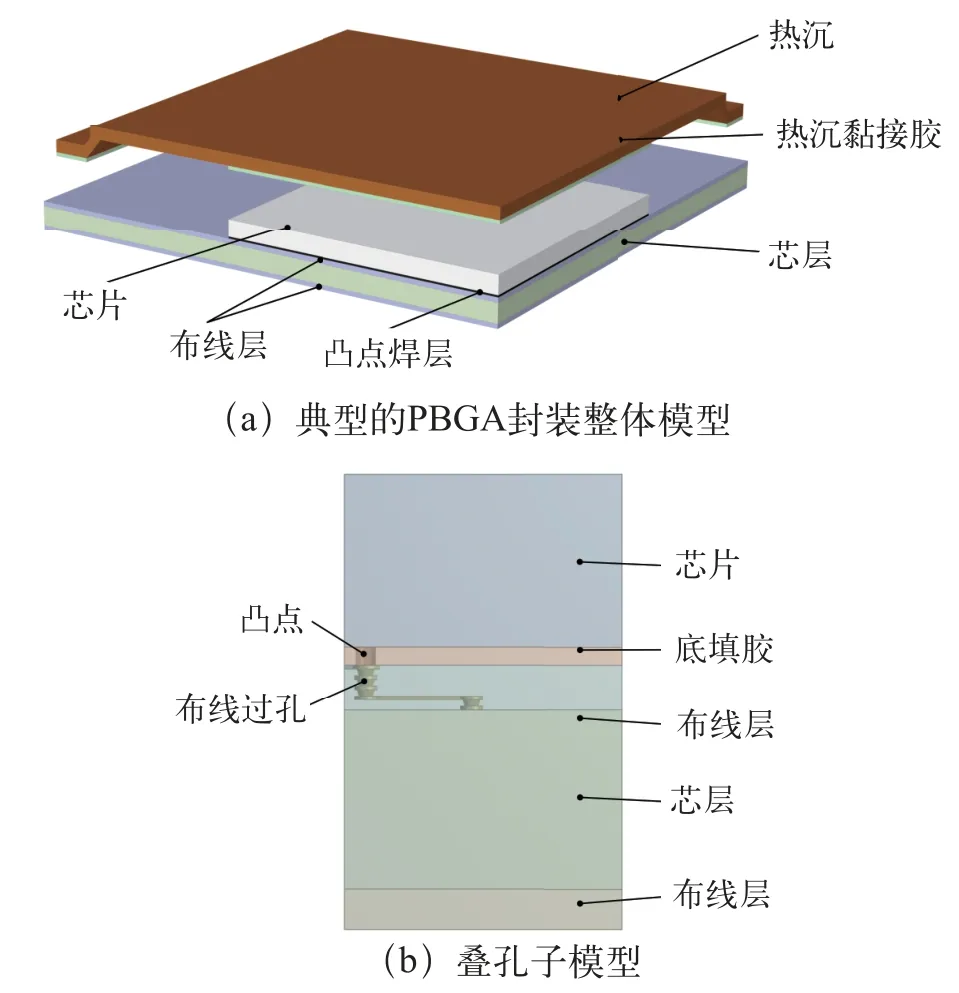

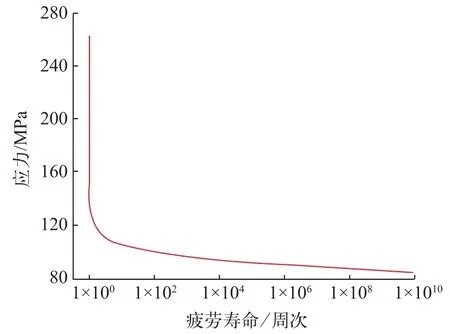

具有芯板结构的IC 封装基板在结构上主要分为3 个部分,中间部分为芯板,上下部分为积层,布线层之间通过铜过孔实现电气连接[16]。典型的PBGA 封装整体模型如图1(a)所示,整体模型主要由热沉、热沉黏接胶、芯片、凸点焊层、布线层及芯层组成,采用1/4模型进行建模,并对凸点焊层材料进行均匀化处理。叠孔子模型如图1(b)所示,主要包括芯片、凸点、底填胶、布线过孔、布线层及芯层,其中对凸点、布线过孔进行了详细建模,忽略芯层中的PTH 孔。在实际应用中,依据电路设计要求,基板内存在多种叠孔,本模型采用的是1 种典型的3 层叠孔,内部主要为铜填充,叠孔的S-N 曲线如图2 所示,裸芯片的主要成分为硅,凸点使用Pb63Sn37 焊料。

图1 PBGA 封装结构的整体模型与叠孔子模型

图2 叠孔的S-N 曲线

1.2 叠孔的热力耦合有限元模型

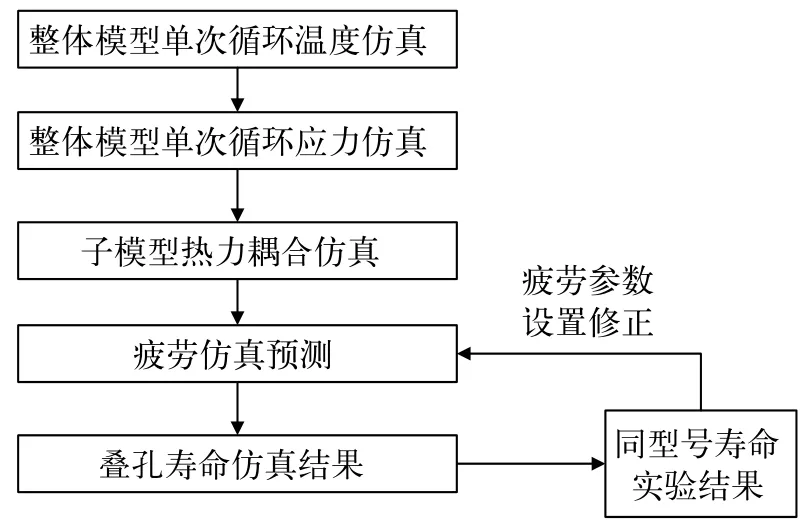

单次温度循环的加载温度为-65~150 ℃,在高低温阶段的停留时间均为15 min。在仿真中选取SOLID 186 单元模型,基于瞬态热学模块计算单次温度循环时整体模型的温度变化情况,将结果导入结构模块,进行热力耦合分析,最后将整体模型应力及温度场结果作为边界条件导入子模型,完成子模型的结构仿真,基于单次温度循环应力的计算结果,计算叠孔的疲劳寿命。为保证仿真结果的准确性,选取典型实验数据对疲劳寿命仿真中设定的相关参数(应力缩放因子、疲劳强度因子)加以修正。ABF 塑封基板叠孔的疲劳寿命仿真流程如图3 所示。

图3 ABF 塑封基板叠孔的疲劳寿命仿真流程

1.3 疲劳寿命的仿真预测

Ansys 软件的疲劳分析模块包含多种疲劳分析方法,本仿真采用应力寿命分析和应变寿命分析[17]。基于S-N 曲线进行应力寿命分析,Basquin 模型[18]是反映应力幅值与疲劳寿命之间关系的数学模型,表达式为

对于低周疲劳问题,一般采用应变寿命分析,应变寿命分析基于Coffin-Manson 方程[19],该方程需要定义4 个应变寿命特性参数和2 个循环应力应变参数,通过这些参数来描述材料在低应力水平下的疲劳寿命。Coffin-Manson 方程为

式中:K′为循环强度系数,n′为循环应变硬化指数。

2 叠孔可靠性仿真结果分析

2.1 叠孔的疲劳寿命预测

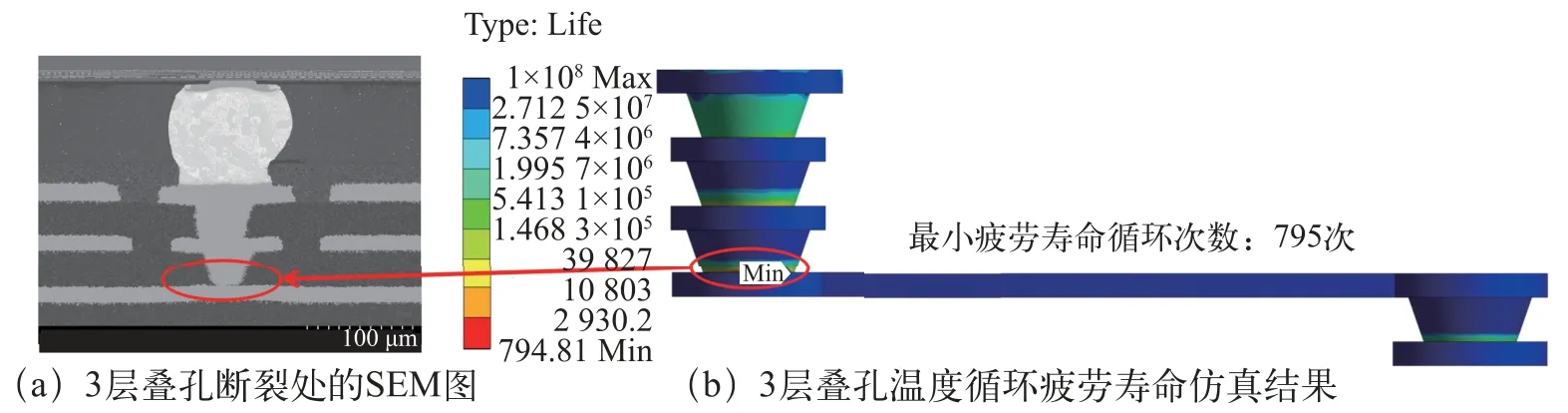

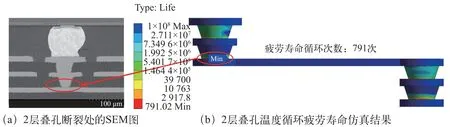

某型号PBGA 封装电路经过约900 次温度循环后,在叠孔与布线层连接处出现明显的贯穿裂纹,图4(a)为3 层叠孔断裂处的SEM 图,该裂纹出现在位于芯片中心位置的3 层叠孔处。为明确失效机理,优化布线参数,基于1.1 节建立的有限元模型及仿真方法进行热应力分析,依据实验条件,将子模型的位置设定在芯片中心区域,借助疲劳分析工具计算该位置处的单轴拉伸疲劳结果,选择非对称加载方式,在整体应力缩放因子为0.6、疲劳强度因子为0.91 的条件下,应力危险点处的最小疲劳寿命循环次数的计算结果约为795 次,接近实验结果(约900 次温度循环)。芯片中心位置的3 层叠孔温度循环疲劳寿命仿真结果如图4(b)所示。

图4 芯片中心位置的3 层叠孔SEM 图及温度循环疲劳寿命仿真结果

为验证疲劳寿命预测的准确性,针对该型号PBGA 封装电路位于芯片对角位置的2 层叠孔进行实验及仿真分析。在经历了约850 次温度循环后,2 层叠孔出现裂纹,图5(a)为2 层叠孔断裂处的SEM 图,在疲劳计算中,在整体应力缩放因子为0.6、疲劳强度因子为0.91 的条件下,2 层叠孔的温度循环疲劳寿命仿真结果约为791 次循环,如图5(b)所示,仿真结果与实验结果(约850 次温度循环)较为接近,这说明针对该型号PBGA 封装电路的塑封基板叠孔,使用当前设定的疲劳计算参数得到的仿真结果是可靠的。

图5 芯片对角位置的2 层叠孔SEM 图及温度循环疲劳寿命仿真结果

2.2 影响叠孔可靠性的因素

2.2.1 叠孔位置对可靠性的影响

为了评估塑封基板不同位置叠孔的可靠性,选取芯片中心、芯片对角和基板对角3 个典型位置的叠孔对3 层叠孔的可靠性进行仿真研究。通过调整子模型相对于整体模型的坐标,可以实现对不同位置叠孔的仿真,位于基板对角位置叠孔的子模型不包含芯片、凸点和底填胶等。不同位置的3 层叠孔疲劳寿命仿真结果如图6 所示,其中,基板对角位置叠孔受到的应力最小,疲劳寿命仿真结果约为933 次循环,芯片中心位置叠孔的疲劳寿命仿真结果约为795 次循环,芯片对角位置叠孔受到的应力最大,疲劳寿命仿真结果约为509 次循环。芯片对角位置叠孔的疲劳寿命相比中心位置叠孔下降约36%。温度变化过程中各层材料间的CTE 失配导致界面间产生较大的应力,其中各界面边缘处产生的应力最大,因此芯片边角位置叠孔的可靠性较低,在布线设计中应尽量避免在该位置设计较多叠孔。

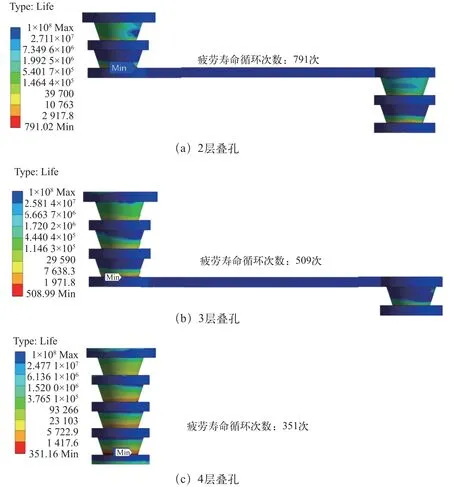

2.2.2 叠孔层数对可靠性的影响

常规的PBGA 封装基板布线层存在多种叠孔,为探究叠孔层数对基板可靠性的影响,选择芯片对角位置的叠孔,分别对2 层、3 层及4 层的叠孔进行仿真分析。不同层数叠孔的疲劳寿命仿真结果如图7 所示,各叠孔的应力危险点均位于最下层过孔根部位置与布线层连接处,2 层、3 层及4 层叠孔的疲劳寿命分别约为791 次、509 次及351 次循环,随着叠孔层数的增加,基板可靠性显著降低,相比于2 层叠孔,4 层叠孔疲劳寿命下降约55.6%,原因可能是随着叠孔层数的增加,叠孔处的弯矩增大,进而导致疲劳寿命下降。以1 000 次循环作为判据,在当前材料及几何参数下,芯片对角位置的3 层、4 层叠孔的疲劳寿命均已不满足要求。

图7 不同层数叠孔的疲劳寿命仿真结果

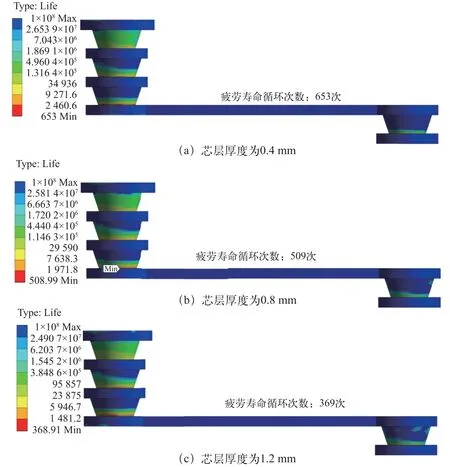

2.2.3 芯层厚度对可靠性的影响

芯层是有芯塑封基板的主要组成部分,其厚度的变化直接影响封装内部各组分的占比,进而影响热加载条件下内应力的分布及基板翘曲程度。基板特定位置的内应力变化对叠孔可靠性有较大影响,为了研究叠孔温度循环疲劳寿命随芯层厚度的变化情况,对芯片对角位置的3 层叠孔进行仿真分析。在芯层厚度分别为0.4 mm、0.8 mm 和1.2 mm 时,叠孔的温度循环疲劳寿命仿真结果如图8 所示,从图8 可知,随着芯层厚度的增加,叠孔温度循环疲劳寿命呈现下降趋势,每增长0.4 mm,叠孔寿命相较于芯层厚度增长前分别降低约22.1%和27.5%,这是由于芯层材料与积层材料的CTE 差异较大,芯层厚度的增加加剧了材料间的热失配程度,导致叠孔可靠性降低。在3 种芯层厚度下,芯片对角位置的3 层叠孔的可靠性均不满足1 000 次循环的要求,因此,当芯片边缘位置的多层叠孔较多时,应尽量避免使用芯层较厚的塑封基板。

图8 不同芯层厚度时叠孔的温度循环疲劳寿命仿真结果

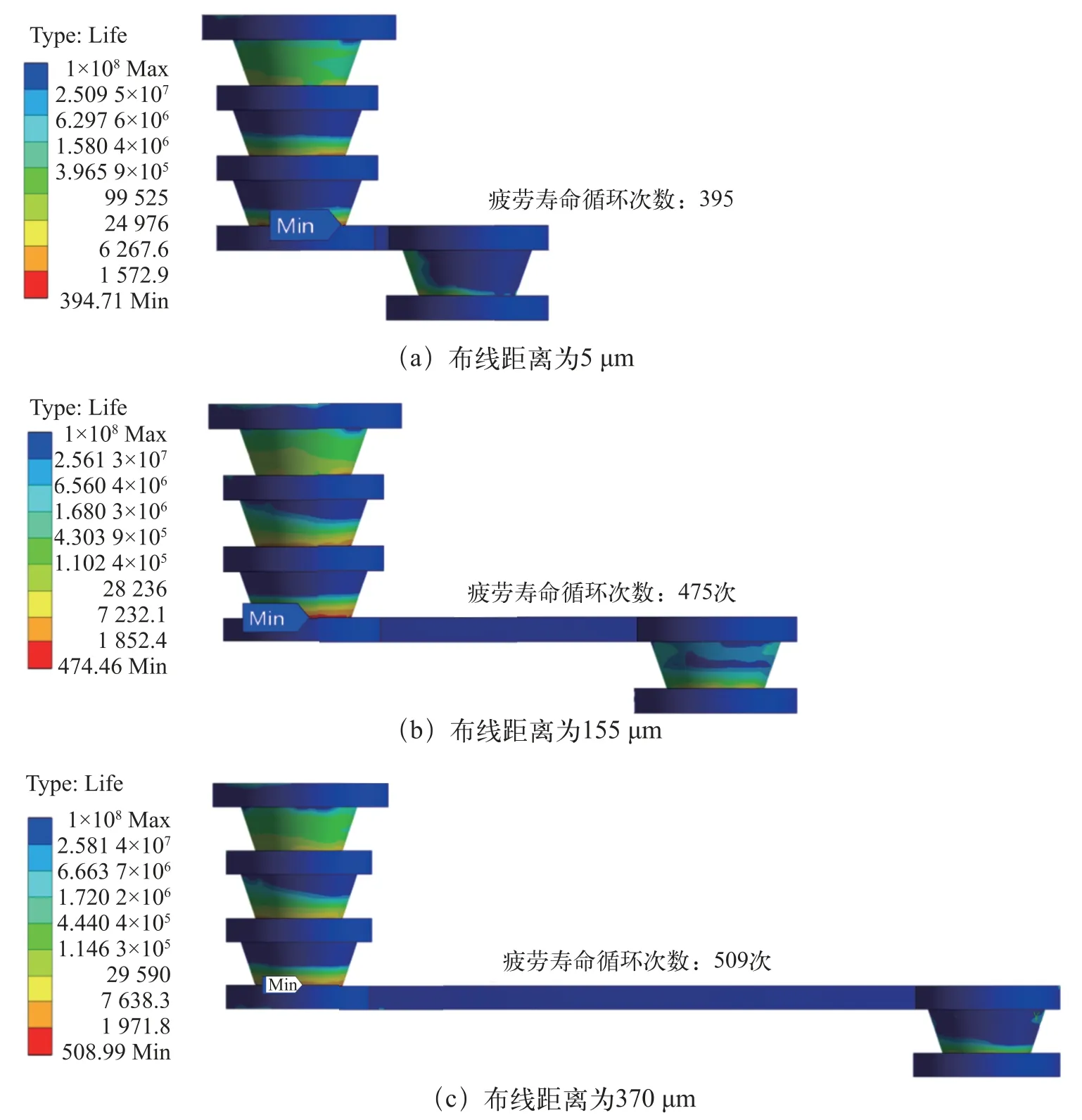

2.2.4 布线长度对可靠性的影响

在实际的封装基板中,依据不同的布线形式,不同层间过孔的布线距离也有所不同,常规的塑封基板过孔间布线距离为5~370 μm。本文以芯片对角位置的2 层叠孔为例,针对孔间布线距离分别为5 μm、155 μm 和370 μm 的叠孔进行仿真分析,不同布线距离下叠孔的温度循环疲劳寿命仿真结果如图9 所示,分别约为395 次、475 次及509 次循环。可以看出,随着孔间布线距离的减小,叠孔疲劳寿命下降,相比于布线距离为370 μm 的叠孔,布线距离为5 μm 的叠孔疲劳寿命降低约22.4%,在弯矩相似的情况下,布线距离的缩短导致叠孔根部应力增加,进而降低了疲劳寿命。

图9 不同布线距离下叠孔的温度循环疲劳寿命仿真结果

3 结论

本文提出了ABF 塑封基板叠孔温度循环疲劳寿命的预测方法,并进行温度循环实验,基于提出的疲劳寿命预测方法,对叠孔位置、叠孔层数、芯层厚度、布线长度等因素进行了进一步仿真分析,结论如下。

1)采用仿真方法得到的疲劳寿命预测结果与实验结果基本一致,铜布线结构的应力危险点出现在底端过孔与布线层连接处,与实际失效情况相符。

2)不同布线结构的最大应力均集中在最下层过孔与布线层连接的根部位置,该位置同时也是实验中的主要失效位置。

3)仿真分析结果表明,芯片对角位置叠孔疲劳寿命较低,同时叠层数量、芯层厚度的增加及走线距离的缩短均会使叠孔可靠性降低。

综上所述,在布线设计中应充分结合仿真分析结果,合理选择较优的布线参数,避免在芯片边缘位置设计多层叠孔以及进行短距离布线,选用较薄的芯层也有助于提升基板可靠性。