增强型β-Ga2 O3/4H-SiC 异质结VDMOS 的设计与研究

王海林,栾苏珍,,程梅霞,贾仁需

(1.西安科技大学 通信与信息工程学院,陕西 西安 710054;2.西安市网络融合通信重点实验室,陕西 西安 710600;3.西安电子科技大学 微电子学院 宽带隙半导体材料与器件重点实验室,陕西 西安 710071)

随着科技的发展,以汽车、高铁为代表的交通工具,以光伏、风电为代表的新能源领域,以手机为代表的通信设备,以电视机、洗衣机、空调、冰箱为代表的消费级产品,都在不断提高电子化水平。与此同时,工业、电网等传统行业也在加速电子化进程,几乎全行业的电子化发展大大增加了对功率半导体器件的需求。近年来,由宽禁带半导体材料制作而成的功率器件受到广泛关注。宽禁带半导体材料相较于传统Si 材料有着更优良的材料特性,可以更好地满足功率器件大功率、大电压的需求。氧化镓(Ga2O3)作为新一代宽禁带半导体材料,有五种不同的结晶形态,其中单斜晶系β 形态最稳定。其禁带宽度为4.6~4.9 eV,击穿场强为8 MV/cm,且Baliga 优值远超SiC、GaN 等宽禁带半导体,在功率器件应用中已引起广泛关注。同时,利用熔融技术可以生长出大尺寸、低成本的Ga2O3单晶,且通过分子束外延(MBE)法可以获得高质量的N 型Ga2O3材料。因为其优越的材料特性和较低的晶圆制备成本,β-Ga2O3有望成为新一代的高压大功率半导体器件材料。

针对β-Ga2O3器件的研究开始于2012 年[1],基于β-Ga2O3基的异质结日盲探测器[2-3]、功率器件如肖特基势垒二极管(SBD)[4]和场效应管(FET)[5-7]的研发进展很快。已报道的结构有击穿电压达到1 kV 的带场板的肖特基势垒二极管[8]、功率品质因数达到50.4 MW/cm2的带源极场板MOSFET[9]、击穿电压超过750 V 的带栅极场板MOSFET[10]、击穿电压超过1 kV 的纵向增强型MOSFET[11]。由于氧化镓难以形成有效的P 型掺杂,上述β-Ga2O3MOSFET 结构中仅使用了N型β-Ga2O3材料,没有在器件中形成PN 结。无结MOSFET 的关断性能以及耐压性能相较于有结器件会差一些,且不容易形成增强型器件,限制了器件性能的优化。截止到目前,β-Ga2O3器件的性能还远远低于理论值,还需要进一步优化结构来提升器件性能。

为了实现有结增强型的β-Ga2O3功率器件,本研究提出了一种具有异质结结构的β-Ga2O3VDMOS。通过在外延层中添加P 型4H-SiC,与N 型β-Ga2O3材料形成β-Ga2O3/4H-SiC 异质结。利用它们之间形成的异质PN 结的单向导通特性,避免了器件在栅极未加偏压时提前形成导电沟道,实现了增强型器件。基于Sentaurus TCAD 软件对该器件的电学特性进行了研究,通过调节主要结构参数,对器件的性能进行了优化设计,最终实现了高性能的有结增强型β-Ga2O3功率器件。

1 模型建立

本节介绍了β-Ga2O3基器件模拟过程中的物理模型参数设置。首先查阅相关文献,总结最近的研究工作中提出的物理模型和实验数据[12-20],建立了β-Ga2O3的物理模型参数文件。纵向β-Ga2O3基器件一般使用沿(001)晶面生长的β-Ga2O3材料[11,16-17],因此本研究运用的都是关于β-Ga2O3(001)材料的物理模型。其中包括能带模型、热力学模型、费米-狄拉克统计、掺杂的不完全电离、掺杂相关的迁移率、高场迁移率、电离掺杂和电离补偿掺杂相关迁移率、碰撞电离和陷阱模型等。在功率器件中,迁移率相关模型和碰撞电离模型参数对于器件的性能影响较大,准确建立这些模型可以使仿真结果更加符合实际情况,下面详细介绍迁移率模型和碰撞电离模型。

1.1 迁移率模型

在模拟过程中,载流子迁移率不是固定不变的。在进行掺杂或器件导通后,迁移率会根据掺杂浓度、表面散射以及电场强度的变化而有所变化,所以需要添加相关依赖模型。本研究采用了Arora 掺杂依赖模型[17],与掺杂相关的迁移率表达式为:

式中:NA,ND分别为受主和施主掺杂浓度;T为温度;其余参数为材料相关模型参数和拟合系数。本文采用了Park 等[17]根据实验结果拟合出的β-Ga2O3(001)的Arora 模型参数,具体参数如表1 所示。

表1 β-Ga2O3 的Arora 模型参数Tab.1 Parameters of Arora model for β-Ga2O3

在器件工作时,载流子速度会随着电场强度的增大而增大,进而达到速度饱和,当速度饱和后电场继续增大,载流子迁移率就会随之下降。大电场下的速度饱和模型采用了典型的Caughey-Thomas 模型[18-19],在此模型中,高场下的迁移率由电子饱和速度决定,根据Pearton 等[18]报道的数据,将β-Ga2O3(001)在高场下的电子饱和速度设定为1.728×107cm/s。

1.2 碰撞电离模型

碰撞电离模型在模拟器件的击穿特性时尤为重要,本研究采用了OkutoCrowell 模型,冲击电离系数(α)表达式如下:

式中:E和T分别是电场和温度;其余参数为拟合参数。根据Ghosh 等[20]通过实验结果拟合出的β-Ga2O3(001)的OkutoCrowell 模型参数,本工作设定a=7.06×105,b=1.77×107,c=-3.29×10-2,d=0,γ和δ设定为0 和1。当α的积分大于1 时,器件发生雪崩击穿,此时的电压称为击穿电压。

2 器件结构与能带分布

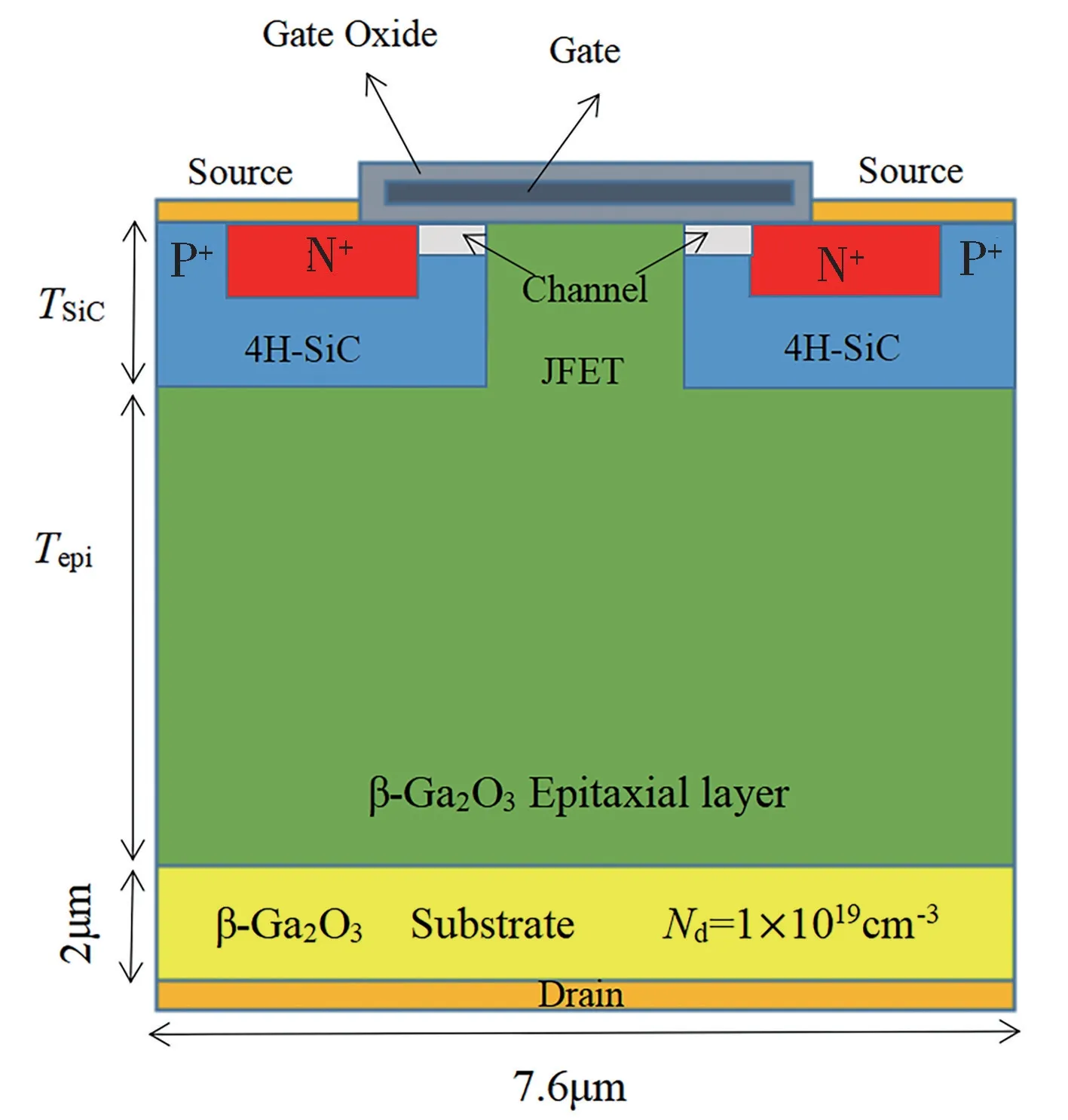

2.1 器件结构

图1 是本工作利用Sentaurus TCAD 软件设计的器件横截面图,该场效应管是一个典型的VDMOS 结构,由轻掺杂外延层、重掺杂衬底、重掺杂源区以及P 阱构成,初始结构参数参考了Salemi 等[21]报道的VDMOS 结构参数。该器件的衬底和外延层采用了沿(001)晶面生长的N 型β-Ga2O3材料。漏电极欧姆接触形成在重掺杂衬底的下方,衬底厚度为2 μm。衬底上方是轻掺杂的外延层,外延层上方是两个相邻的由4H-SiC 形成的P 阱,掺杂浓度为5×1017cm-3。P 阱除了起到与β-Ga2O3形成异质结的作用,也可以避免电场线在栅极边缘处堆积而提前击穿晶体管,增加了晶体管的稳定性。源极由P 阱包围的N 型重掺杂β-Ga2O3区域(1×1020cm-3)形成,源极厚度为0.2 μm,源极金属下方的P 型SiC 也进行了重掺杂形成P+区,使半导体和源电极形成良好的欧姆接触。相邻P 肼之间的β-Ga2O3区域为JFET 区。栅氧化层材料为HfO2,厚度为50 nm,栅氧化层包裹着栅极金属,栅极长度为4.0 μm,功函数设置为4.6 eV,金属栅极触点包裹在栅极金属上。MOS 沟道由栅氧化层下方的P阱构成,沟道长度为0.5 μm。

图1 β-Ga2O3 VDMOS 横截面图Fig.1 Cross-sectional view of β-Ga2O3 VDMOS

2.2 能带分布

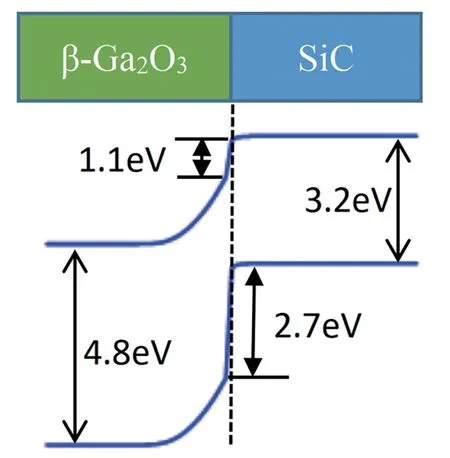

在晶体管零偏压情况下p-SiC/n-Ga2O3的异质结能带分布情况如图2 所示。β-Ga2O3和4H-SiC 的禁带宽度分别为4.8 eV 和3.2 eV[3]。导带偏置(ΔEC)为1.1 eV,价带偏置(ΔEv)为2.7 eV。由于β-Ga2O3中电子进入SiC 的势垒高度远低于SiC 中空穴向β-Ga2O3移动的势垒高度,因此β-Ga2O3的电子更容易进入SiC,电子起主要作用。

图2 p-SiC/n-Ga2O3 的异质结能带图Fig.2 Energy band diagram of p-SiC/n-Ga2O3 heterojunction

3 仿真结果与讨论

作为功率器件,在追求高击穿电压(Vbr)的同时也需要降低其比导通电阻(Ron,sp),为了折中考虑这两个参数,引入了功率品质因数(PFOM),PFOM 的表达式如下:

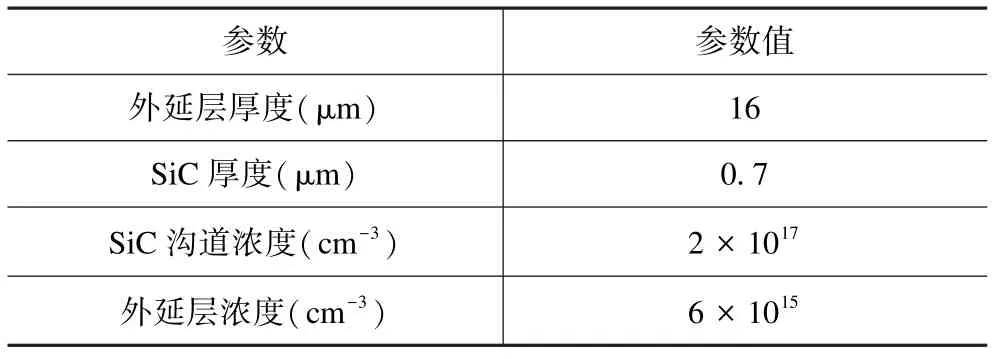

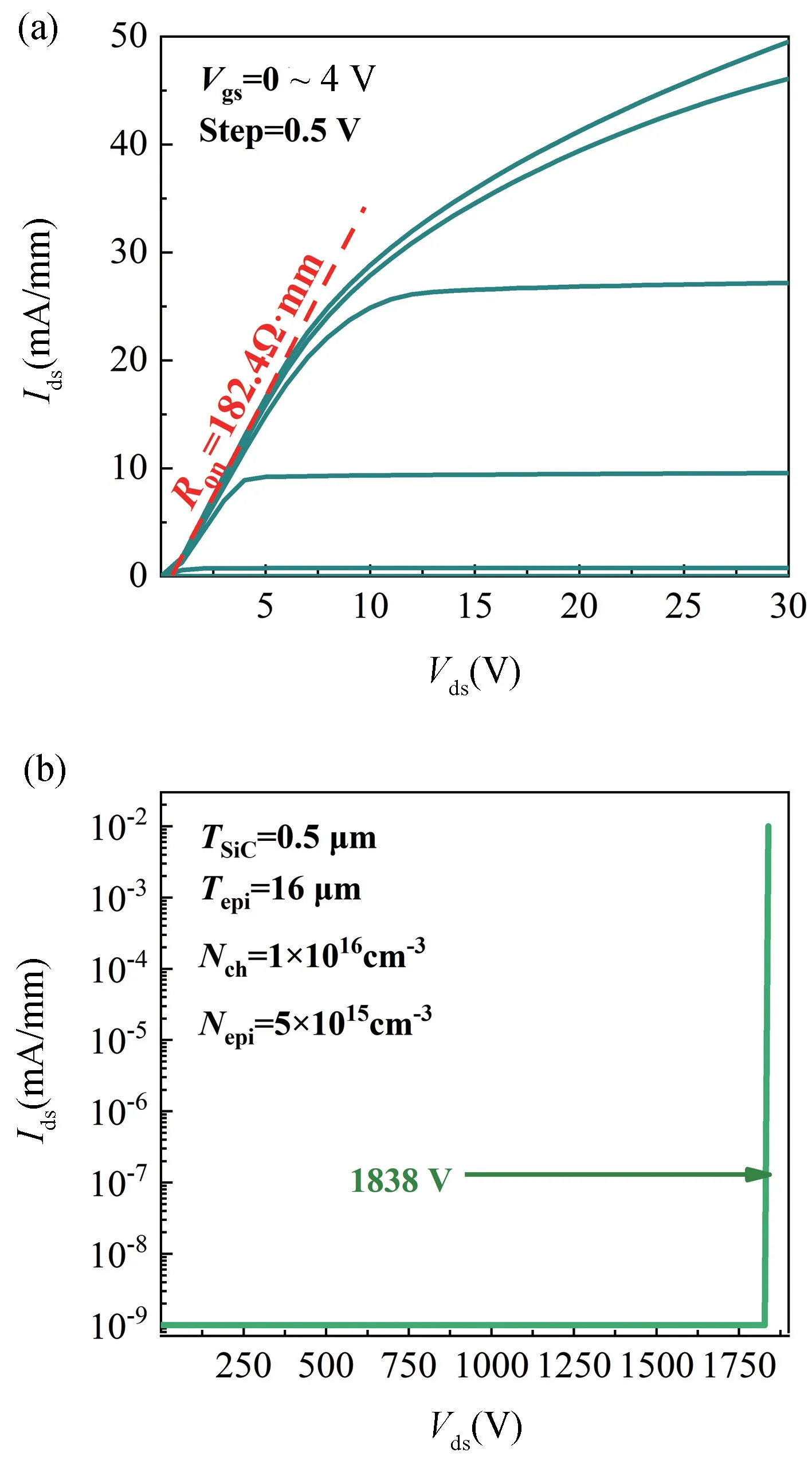

在本文设计的β-Ga2O3/4H-SiC VDMOS 结构中,SiC 厚度(TSiC)、SiC 沟道浓度(Nch)、外延层厚度(Tepi)以及外延层浓度(Nepi)这四个结构参数对于器件的性能影响较大,上述结构参数的初始值[21]如表2 所示。本节研究了上述结构参数变化时器件的Vbr、Ron,sp和PFOM 的变化情况,通过比较不同结构参数下器件的PFOM 值,得到器件PFOM 最优值,进而确定上述结构参数的最优值。

表2 器件主要结构参数初始值Tab.2 Initial values of the main structural parameters of the device

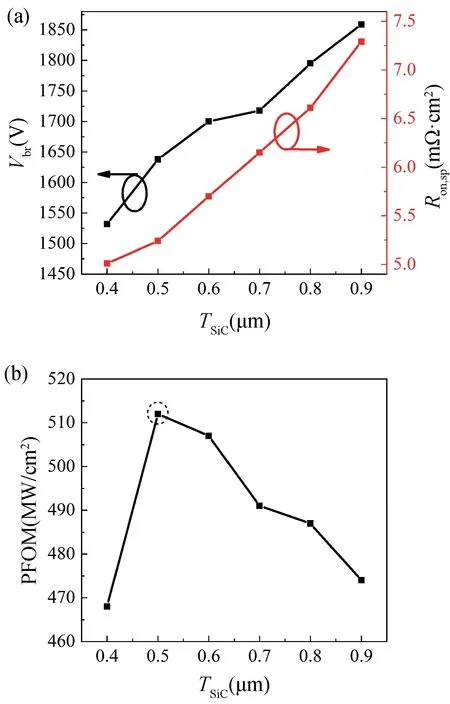

3.1 SiC 厚度优化

首先模拟了SiC 厚度变化时器件的性能变化,图3 显示了该器件的Vbr、Ron,sp以及PFOM 随TSiC的变化情况。图3(a)表明随TSiC的增加,Vbr和Ron,sp都随之增大。TSiC增加,电流从源极流向漏极的距离增加进而导致Ron,sp增大,同时TSiC增大,P 肼在被击穿前可以承受更高的电压,所以Vbr也增大。图3(b)显示随着TSiC的增加,器件的PFOM 的变化是先增大后减小。在TSiC为0.5 μm 时器件有最大的PFOM,所以SiC 厚度的最优值是0.5 μm。

图3 不同SiC 厚度下β-Ga2O3 VDMOS 的性能。(a)Vbr和Ron,sp;(b)PFOMFig.3 The (a) Vbr and Ron,sp and (b) PFOM of β-Ga2O3 VDMOS with different SiC thicknesses

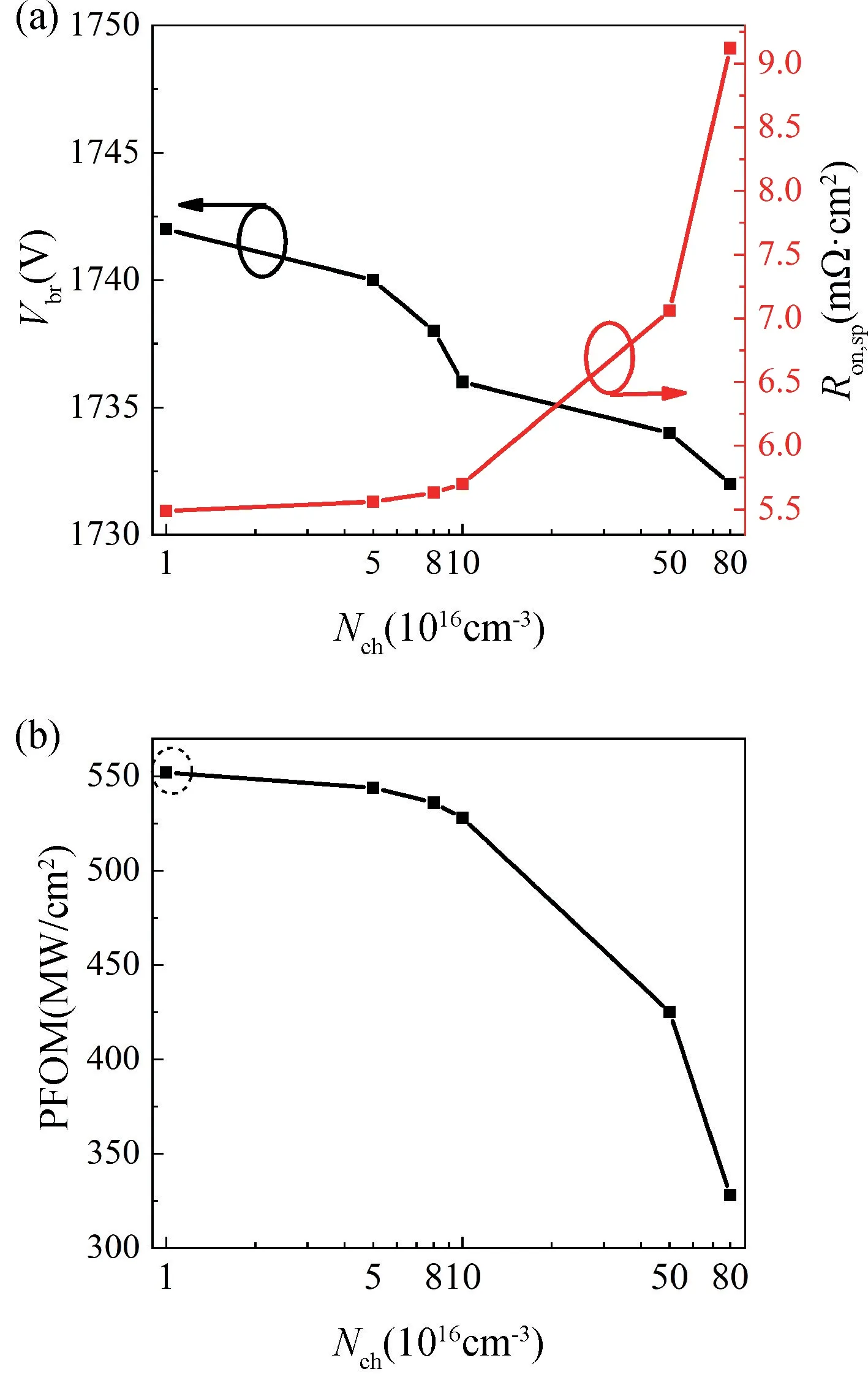

3.2 SiC 沟道浓度优化

图4 显示了器件性能随着SiC 沟道浓度的变化趋势,SiC 沟道浓度对器件的比导通电阻影响较大,对器件的击穿电压影响较小。图4(a)显示随着Nch的升高,Vbr略微降低,Nch越高,PN 结宽度越窄,PN 结就越容易击穿,所以Vbr降低。图4(a)中还显示随着Nch的升高,器件的Ron,sp逐渐增大,当Nch大于1×1017cm-3时,Ron,sp显著增大。这是因为Nch越高,电离杂质散射越强,沟道的载流子迁移率就越低,进而导致Ron,sp越大。图4(b)显示器件在Nch为1×1016cm-3时有最优PFOM,所以器件最优沟道浓度为1×1016cm-3。

图4 不同SiC 沟道浓度下β-Ga2O3 VDMOS 的性能。(a)Vbr和Ron,sp;(b)PFOMFig.4 The (a) Vbr and Ron,sp and (b) PFOM of β-Ga2O3 VDMOS with different SiC channel concentrations

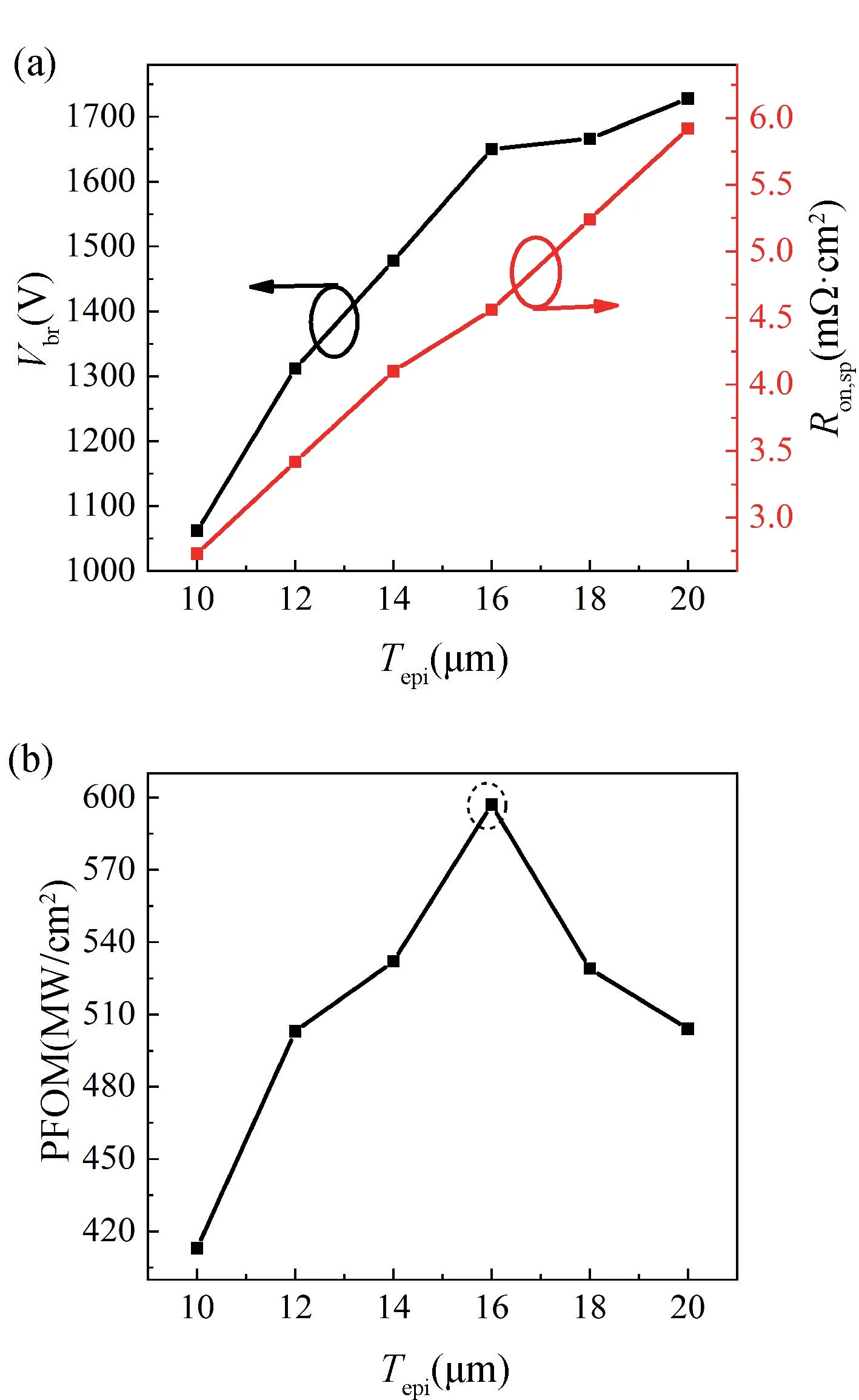

3.3 外延层厚度优化

β-Ga2O3/4H-SiC VDMOS 在高压环境中工作时,大部分的电压主要由外延层承受,因此外延层参数对器件性能影响较大。当TSiC和Nch固定为最优值时,器件性能随着外延层厚度的变化趋势如图5 所示。图5(a)显示,器件的Vbr和Ron,sp随着Tepi的增大而增大,因为Tepi越大,需要更大的电压才能将外延层耗尽,所以Vbr越大。同时Tepi越大,电流从源极流向漏极的距离也越远,所以Ron,sp越大。图5(b)显示随着Tepi的增大,PFOM 先增大后减小,在Tepi为16 μm 时,器件有最大的PFOM,所以外延层最优厚度为16 μm。

图5 不同外延层厚度下β-Ga2O3 VDMOS 的性能。(a)Vbr和Ron,sp;(b)PFOMFig.5 The (a) Vbr and Ron,sp and (b) PFOM of β-Ga2O3 VDMOS with different epitaxial layer thicknesses

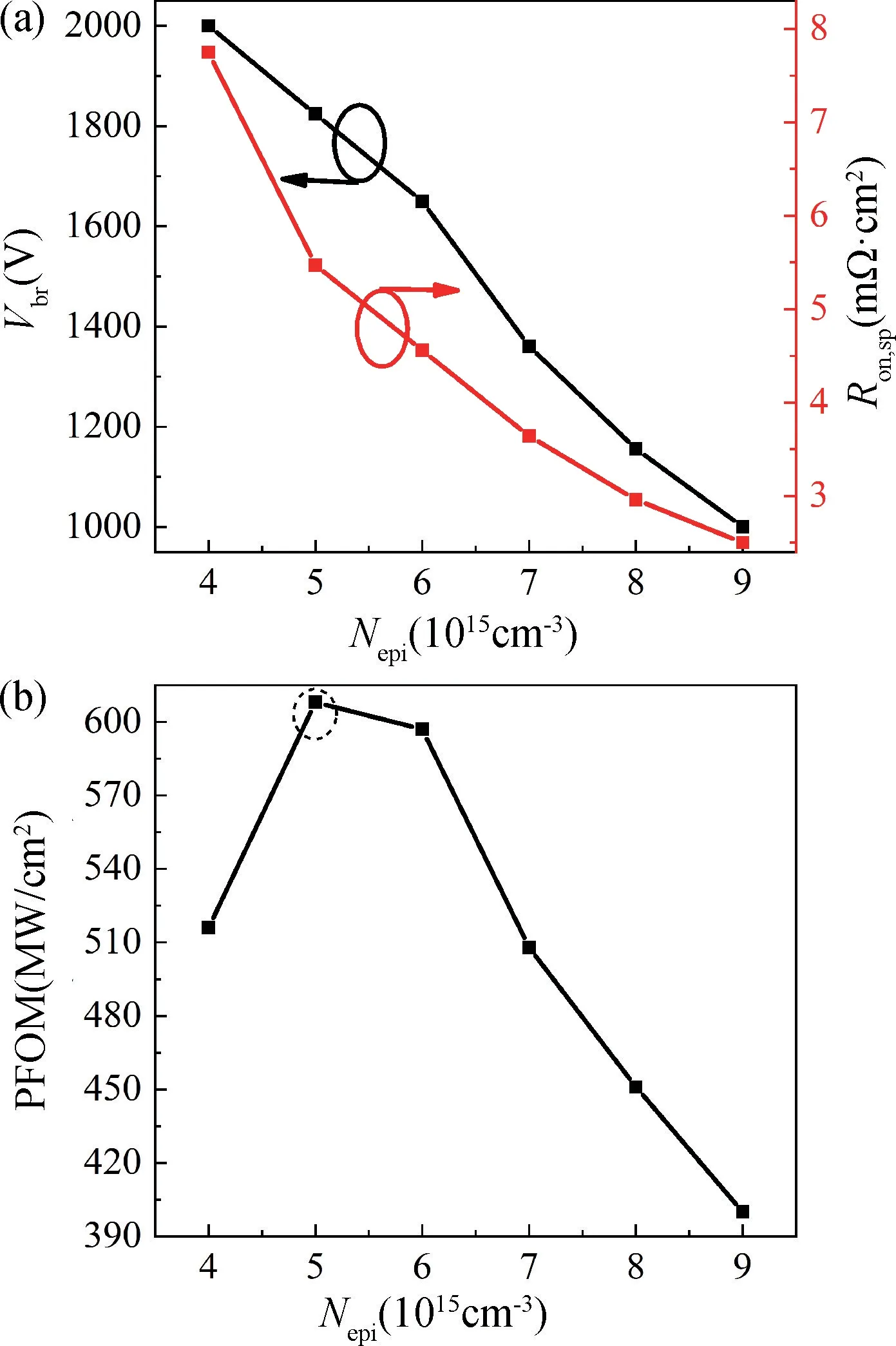

3.4 延层浓度优化

由文献[22]得知β-Ga2O3的外延层浓度需要低于2×1016cm-3,且外延层浓度对器件的性能影响较大。因此模拟了在不同Nepi下器件的性能变化,如图6 所示。由图6(a)可以看出,Vbr和Ron,sp都随着Nepi的增加而降低。随着Nepi的增加,外延层的电阻率下降,使得器件的Ron,sp降低。同时随着Nepi的增大,外延层带电离子间距变小,导致外延层的电场增大,更加容易击穿,所以器件的Vbr降低。图6(b)表明,随着Nepi的增大,PFOM 先增大后减小,在Nepi为5×1015cm-3时器件的PFOM 达到最大值,所以器件的外延层浓度最优值为5×1015cm-3。

图6 不同外延层浓度下β-Ga2O3 VDMOS 的性能。(a)Vbr和Ron,sp;(b)PFOMFig.6 The (a) Vbr and Ron,sp and (b) PFOM of β-Ga2O3 VDMOS with different epitaxial layer concentrations

3.5 优化后的器件性能

上述模拟结果表明,当SiC 层厚度为0.5 μm,SiC 沟道浓度为1×1016cm-3,外延层厚度为16 μm,外延层浓度为5×1015cm-3时,本研究设计的β-Ga2O3VDMOS 有最优的器件性能。优化后的器件主要结构参数如表3 所示。

表3 优化后的器件主要结构参数Tab.3 Main structural parameters of the optimized device

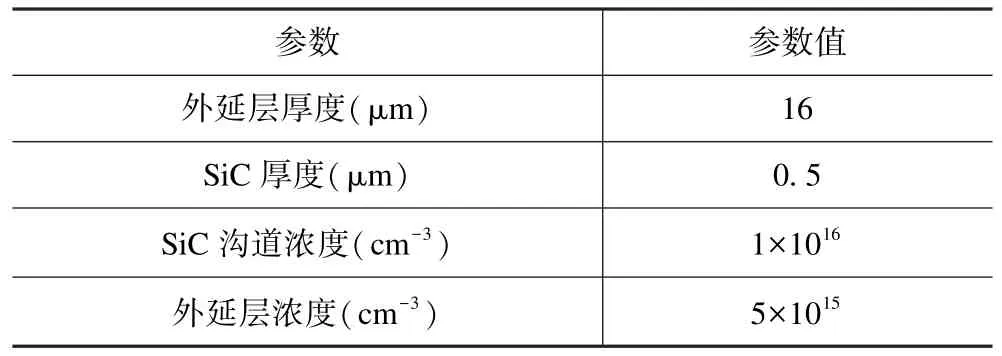

优化后的器件的转移特性如图7 所示,图7(a)是漏极偏压(Vds)为30 V 时晶体管的转移特性曲线和跨导曲线,图中曲线显示器件的阈值电压为1.62 V。P型SiC 与源区之间的异质结发挥了优良的单向导电特性,实现了常关型操作。由转移曲线中漏极电流(Ids)对栅极偏压(Vgs)的微分可求得器件的跨导(gm),器件的最大跨导为39.29 ms/mm。图7(b)是在Vds为30 V 时的半对数尺度转移特性曲线,曲线显示器件的开关电流比大于109。

图7 优化后的VDMOS 器件性能。(a)转移特性曲线和跨导曲线;(b)半对数尺转移特性曲线Fig.7 The (a) transfer characteristic and transconductance curves and (b) half-log scale transfer characteristic curve of optimized VDMOS device

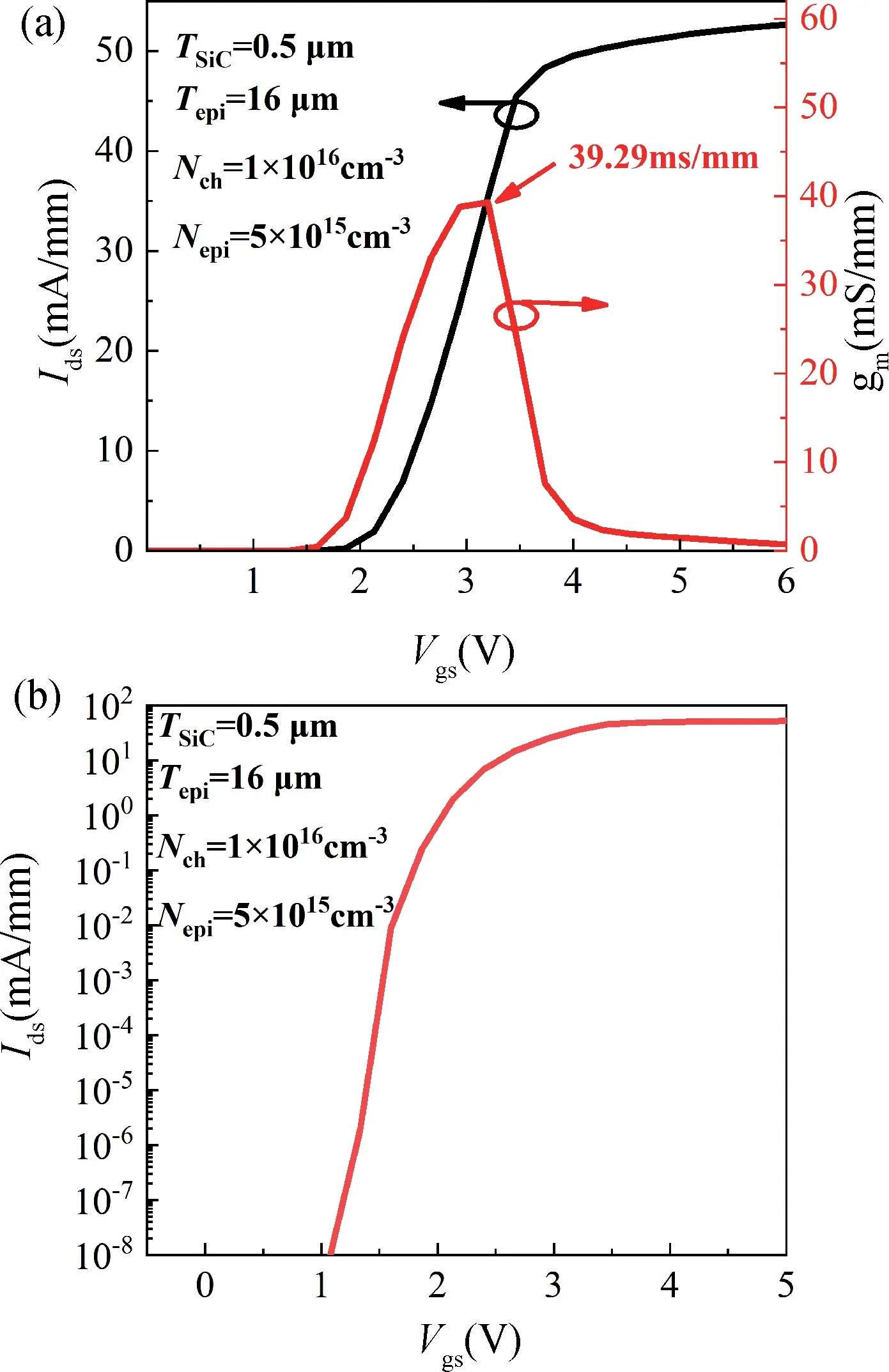

优化后的β-Ga2O3VDMOS 的输出特性曲线和击穿电压如图8 所示。图8(a)显示了器件在Vgs在0~4 V时的输出特性曲线,图中显示在Vgs为4 V,Vds为30 V 时,器件的饱和电流达到49.51 mA/mm。器件的最小导通电阻为182.4 Ω·mm,进而得到器件的比导通电阻为5.47 mΩ·cm2。图8(b)显示了优化后的器件击穿电压为1838 V,此时器件的PFOM 为617 MW/cm2。

图8 优化后的VDMOS 器件性能。(a)输出特性曲线;(b)击穿电压Fig.8 The (a) output characteristic curves and (b) breakdown voltage of optimized VDMOS device

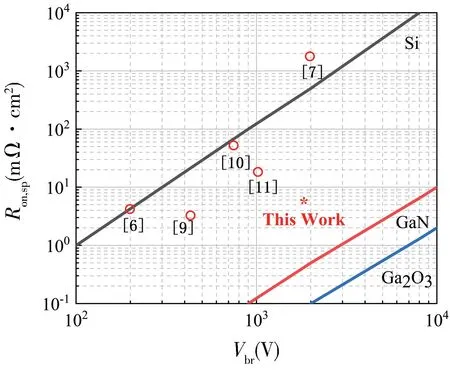

图9 显示了部分已发表文献的β-Ga2O3MOSFET和本研究设计的β-Ga2O3VDMOS 的Vbr和Ron,sp。相比于传统无结器件,本研究设计的β-Ga2O3/4H-SiC 异质结VDMOS 具有更低的Ron,sp和更高的Vbr。因此该器件具有更加优异的性能,更加适合于功率器件应用。

图9 优化后的β-Ga2O3 VDMOS 和部分已发表文献的β-Ga2O3 MOSFET 的比导通电阻和击穿电压Fig.9 Specific on-resistance and breakdown voltage of optimized β-Ga2O3 VDMOS and some published β-Ga2O3 MOSFETs

4 结论

综上所述,本文提出了一种具有β-Ga2O3/4HSiC 异质结结构的VDMOS。利用PN 结的开关特性,得到了1.62 V 的阈值电压,实现了增强型器件。通过调节4H-SiC 层和外延层的相关结构参数,优化了器件性能,实现了较大的击穿电压和较小的比导通电阻。结果表明,该器件的比导通电阻为5.47 mΩ·cm2,击穿电压为1838 V。同时具有39.29 mS/mm 的最大跨导以及高达617 MW/cm2的功率品质因数。β-Ga2O3/4H-SiC 异质结VDMOS 与传统无结器件相比,在实现增强型的同时具有更加优异的PFOM 值,为β-Ga2O3功率器件的性能优化提供了可靠的解决方案。