基于单一PMOS 差分对的轨到轨输入运算放大器设计

杨九川,杨发顺,,马 奎,

(1.贵州大学大数据与信息工程学院,贵州 贵阳 550025;2.半导体功率器件可靠性教育部工程研究中心,贵州 贵阳 550025;3.贵州省微纳电子与软件技术重点实验室,贵州贵阳 550025)

运算放大器是模拟电路中重要的单元电路,在各种模拟电路和数模混合电路中被广泛应用[1]。随着MOS 管的特征尺寸不断缩小,电源电压也随之下降,但阈值电压并没有按比例下降[2-3],运算放大器的输入共模范围与输出电压摆幅变得越来越小,而信号幅度会随着电源电压的降低而降低,导致信噪比的下降,加剧噪声对电路的影响[4]。轨到轨输入运算放大器的输入共模范围可达到正负电源轨[5],在低压应用场景中轨到轨输入共模范围是必不可少的。轨到轨输入运算放大器常采用电荷泵技术与互补差分对技术来实现。

基于电荷泵技术的轨到轨输入级结构只需单差分对,单差分对的局部高供电电压保证尾电流源在饱和区工作,实现轨到轨的共模输入范围。Duisters 等[6]提出了-90 dB 总谐波失真的局部电荷泵轨到轨输入运放,虽然可实现轨到轨输入且总谐波失真很小,但电路结构复杂且片上电容占用较大面积,成本较高。

互补差分对输入处在正负电源中点时会同时导通,跨导变化近似为单差分对的一倍,巨大的跨导变化导致运算放大器频率特性变差[7]。如何保证输入级总跨导在整个共模输入范围内保持稳定是轨到轨运放设计的一个重点[8]。为保持输入级跨导恒定,常用的方法有电压控制法、电流控制法、宽长比控制法、过渡区重叠法、非匹配模式法以及背栅驱动法[9]。谢海情等[10]采用三倍电流镜结构通过电流补偿实现恒跨导轨到轨输入级结构,跨导变化率为5.5%,该结构低压情况下易形成正反馈环路,产生大电流,破坏正常工作状态。王丹等[11]采用改进开关电流结构实现轨到轨输入级跨导变化率为2.26%,其电流开关管与输入晶体管并联增加了输入噪声。唐俊龙等[12]采用电平移位结构结合复用选择电路的轨到轨输入级实现跨导变化率为1.44%,虽结构简单易实现,但其增益不恒定且变化幅度较大。

为此,本文设计了一种单一PMOS 差分对的轨到轨输入级结构,利用PMOS 管体效应动态调节阈值电压,实现轨到轨共模输入范围,共模输入范围内跨导变化率小于3%,无需辅助电路即可实现恒跨导,电路结构简单。输出级采用AB 类结构,静态电流可确定,实现轨到轨满摆幅输出。

1 电路设计与分析

1.1 基于互补差分对的轨到轨输入级电路

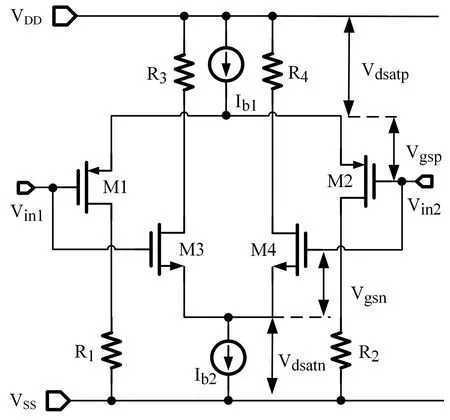

互补差分对的轨到轨输入级是采用PMOS 和NMOS 差分对并联,如图1 所示。

图1 互补差分对轨到轨输入级电路Fig.1 Rail-to-rail input stage circuit with complementary differential pair

PMOS 差分对导通时,输入共模电压范围为:

式中:Vgsp表示PMOS 的栅源电压;Vdsatp表示PMOS 差分对尾电流源的漏源饱和压降。

NMOS 差分对导通时,输入共模电压范围为:

式中:Vgsn表示NMOS 的栅源电压;Vdsatn表示NMOS差分对尾电流源的漏源饱和压降。

PMOS 实现负电源轨VSS的输入共模电压范围,NMOS 实现正电源轨VDD的输入共模电压范围,二者并联的输入共模电压范围为:

运放工作电压的最小值Vsup如式(4)所示:

PMOS 导通时的跨导gmp可表示为:

式中:IDp表示流过PMOS 的电流;μp表示空穴迁移率;Cox表示单位面积栅氧化层电容;(W/L)p表示PMOS 的宽长比。

NMOS 导通时的跨导gmn可表示为:

式中:IDn表示流过NMOS 的电流;μn表示电子迁移率;(W/L)n表示NMOS 的宽长比。

当共模输入电压从VDD向VSS变化时,输入处在正负电源中间时PMOS 与NMOS 对会同时导通。假设PMOS、NMOS 导通时的电流相同,通过调节宽长比使得gmn=gmp,输入级的总跨导gmt=gmn+gmp近似变化一倍。

运放输入级的差模增益AV由输入管跨导gm与等效输出电阻RO决定,可表示为:

二级运算放大器的单位增益带宽GBW 由密勒补偿电容CC与输入管跨导gm决定,表示为:

式(7)和(8)表明,跨导决定运算放大器的差模增益与单位增益带宽。巨大的跨导变化导致运算放大器频率补偿变得困难,影响系统的稳定性[13]。

1.2 基于单一PMOS 差分对的轨到轨输入级设计

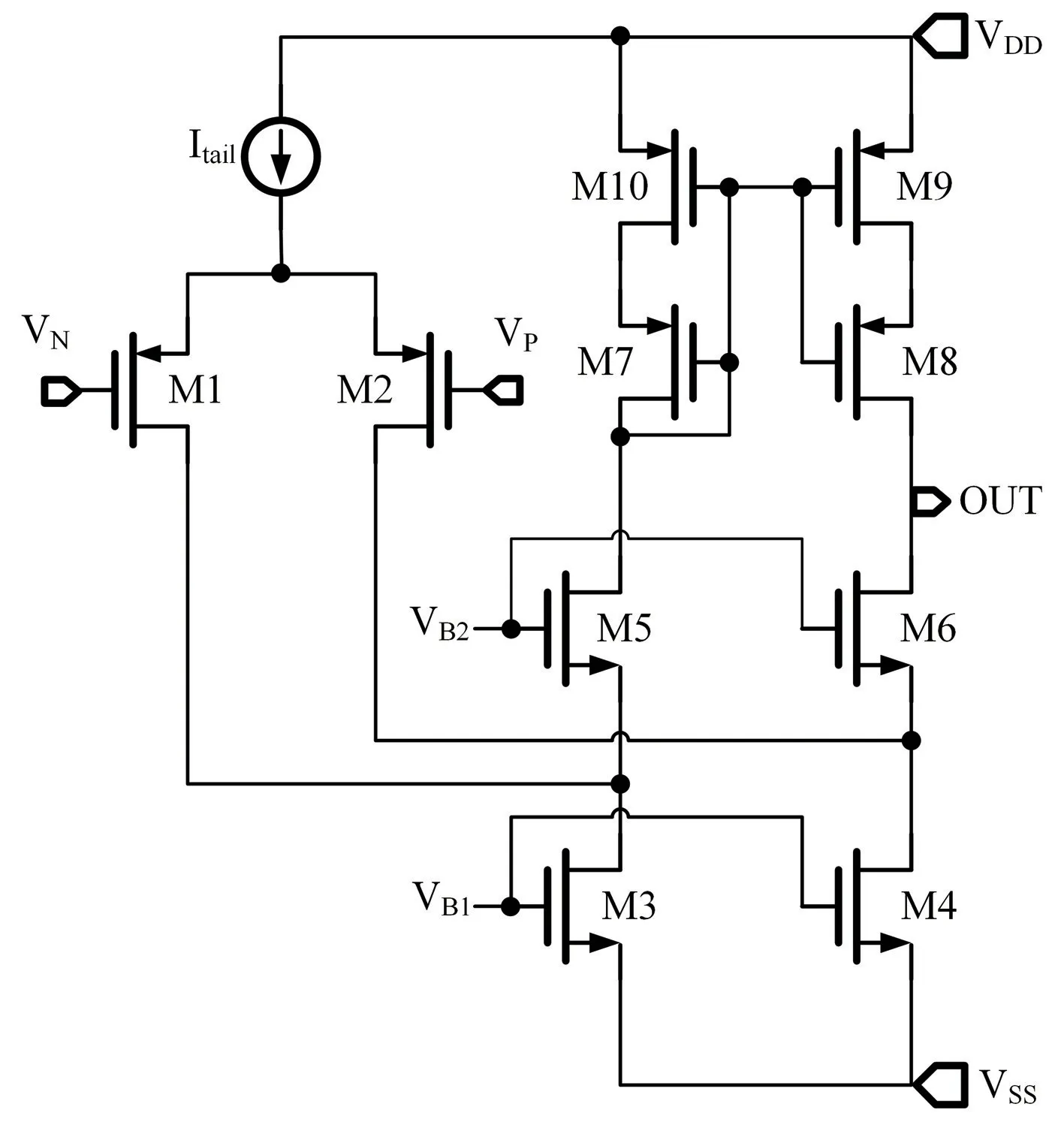

本文设计一种仅PMOS 差分对输入的折叠共源共栅结构,简化电路如图2 所示,电路是由尾电流源、共源共栅输入级以及有源负载组成。采用自级联电流镜给输入对管提供尾电流Itail,M1、M2、M3、M4、M5、M6 构成折叠式共源共栅组态,其有源负载是由M7、M8、M9、M10 组成的自级联电流镜。

图2 单一PMOS 差分对的轨到轨输入级简化电路Fig.2 Simplified circuit of rail-to-rail input stage with single PMOS differential pair

自级联电流镜等效为两管串联,其中M9 工作在线性区,较小的漏源电压提供极大的输出电阻,M8工作在饱和区。输出电阻相较于普通电流镜要大得多,通过自级联电流镜有源负载将双端输入差分信号转换为单端输出,提高差分增益,同时能较好抑制共模信号。

当MOS 管衬底和源极存在电位差时,会影响MOS 管的阈值电压[14],该效应称为衬底偏置效应,衬底偏置效应又称体效应。该结构中输入对管M1、M2 的衬底接VDD,利用衬底和源极电位差调节阈值电压。考虑体效应的PMOS 晶体管阈值电压为:

式中:φF表示费米接触势;VSB表示源极与衬底的电压差;γ表示体效应系数;VTH0表示VSB=0 时PMOS 晶体管的阈值电压。VTH0与γ可用式(10)与(11)表示:

式中:φms表示金属和半导体的功函数差;q表示电子的电荷量;Nsub表示衬底的掺杂浓度;εSi表示硅的介电常数;QSS表示半导体表面电荷密度。

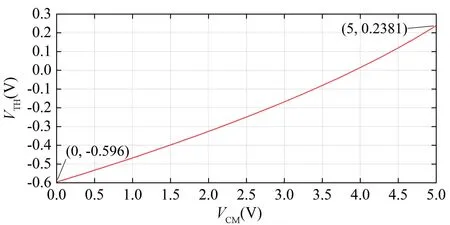

输入对管M1、M2 的衬底接正电源VDD,随着PMOS 输入对管栅极电压从正电源到负电源变化的过程中,PMOS 管阈值电压由正变负。经仿真验证栅极电压从5 V 到0 V 下降的过程中,阈值电压从0.238 V变化为-0.596 V。

输入共模范围的上限由尾电流源Itail的漏源电压决定,当尾电流源工作于饱和区边缘时,漏源电压等于过驱动电压,可计算出输入共模电压的上限:

式中:VOVtail表示尾电流源的过驱动电压;VOV1表示M1的过驱动电压。

从中国刑警学院回来后,王敬凯继续深入梳理案情,以取得更多的证据。 在那封匿名信及3张纸条中,多次出现“瓶装”这个常人颇感生疏的特殊词组。

输入共模范围下限由M3、M4 在饱和区的漏源电压决定,饱和区边缘漏源电压等于过驱动电压,可计算输入共模电压的下限:

由式(12)和(13)可以看出,输入共模范围与过驱动电压以及输入管的阈值电压有关。当输入共模电压接近正电源时,阈值电压为正值;当输入共模电压接近负电源时,阈值电压变为负值,从而利用体效应调节阈值电压抵消过驱动电压来拓宽共模输入范围到正负电源轨。

在输入共模范围内,输入晶体管工作在饱和区,饱和区MOS 管的跨导为:

式(14)表明,输入管的跨导由漏电流、宽长比、迁移率以及单位面积栅氧化层电容决定。输入差分对的漏电流平分尾电流,尾电流恒定即可实现输入级跨导恒定。

1.3 AB 类输出级设计

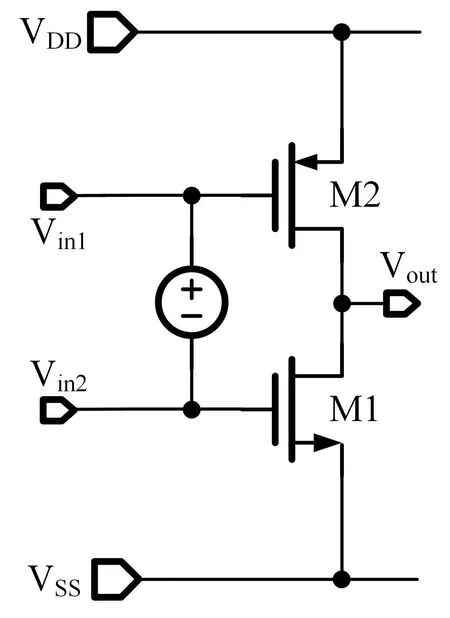

输出级直接驱动负载,需要低静态电流和高输出电流,为充分利用电源电压,满足输出级轨到轨摆幅[15],本文采用AB 类输出级,简化原理图如图3 所示。合理设计栅极之间的电压,使输出晶体管工作在较小的静态电流下以降低静态功耗。

图3 AB 类输出级简化电路Fig.3 Simplified circuit of class AB output stage

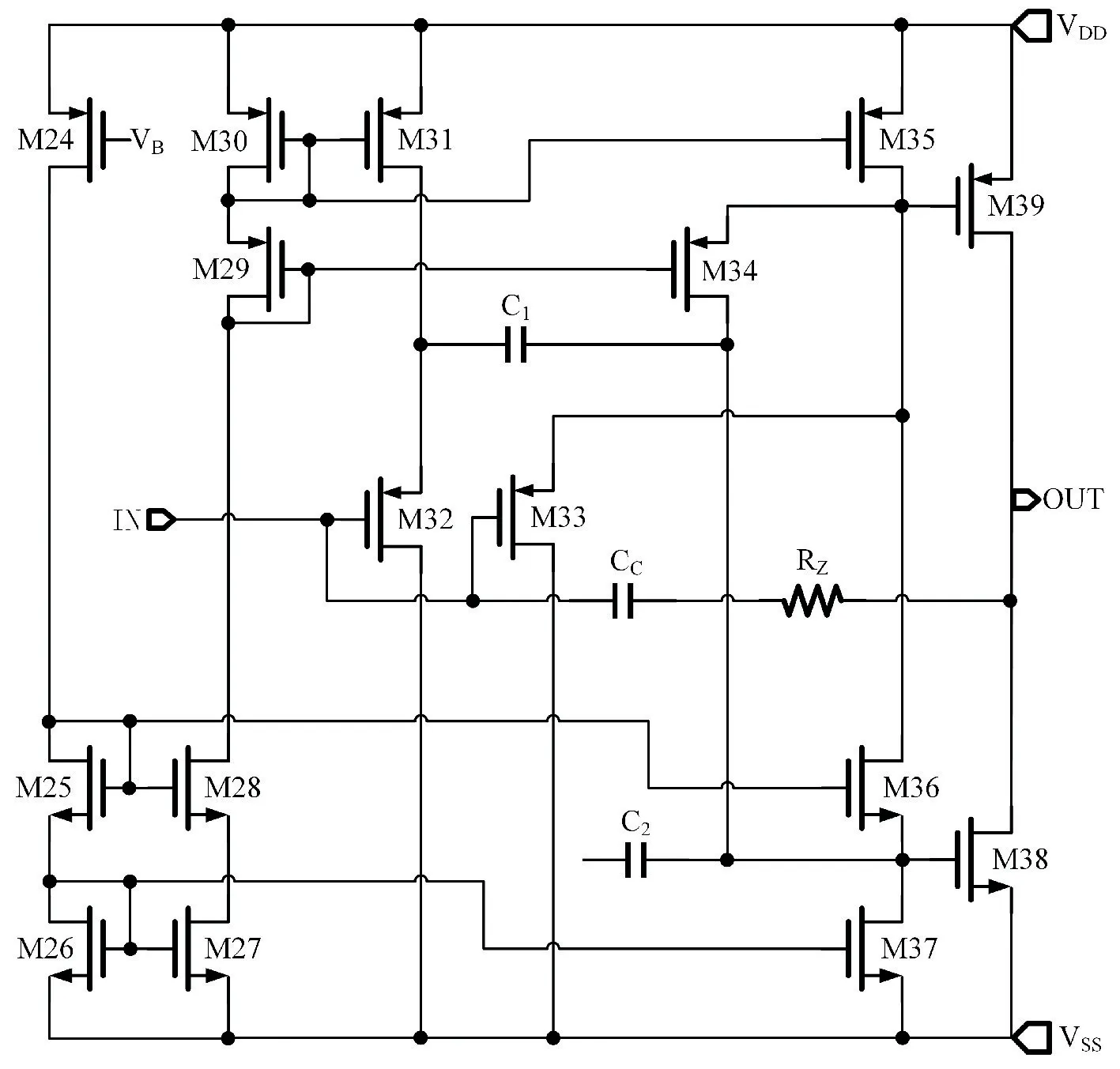

为满足设计需求,结合输入级的单端输出所设计的输出级电路如图4 所示。输入级为提高增益,输出电阻很大。M33 作为输入级与输出级之间的源极跟随器,进行级间缓冲。源极跟随器从栅极输入,低频输入电阻看作无穷,与输入级输出电阻并联,故输入级增益不受影响。AB 类输出级前级采用源极跟随器,其输出电阻很小,输出级的输入电阻远大于该值。M34、M35、M36、M37、M38、M39 组成AB 类输出级,传输大电流到负载,M34、M36 为输出管提供恒定的栅极偏置。

图4 AB 类输出级电路Fig.4 Class AB output stage circuit

该结构采用线性跨导环确定输出级的静态电流[16],线性跨导环表示为:

令μCox(W/L)=k,并通过调节NMOS 和PMOS的宽长比使得相同电流的PMOS 和NMOS 晶体管的k相同,M38、M39 流过的静态电流为IQ,将式(17)分别代入式(15)和(16)可得:

调整相应的比例关系,由式(18)和(19)可确定静态电流IQ。通过调节宽长比可以控制合适的静态电流,得到较大的输出电流。

对于轨到轨输出运算放大器,输出摆幅是一个重要参数。假设输出对管过驱动电压等于漏源电压,可得到输出摆幅范围为:

式(20)表明输出电压摆幅受到输出晶体管M38、M39 的过驱动电压影响,可实现接近轨到轨的输出电压摆幅。

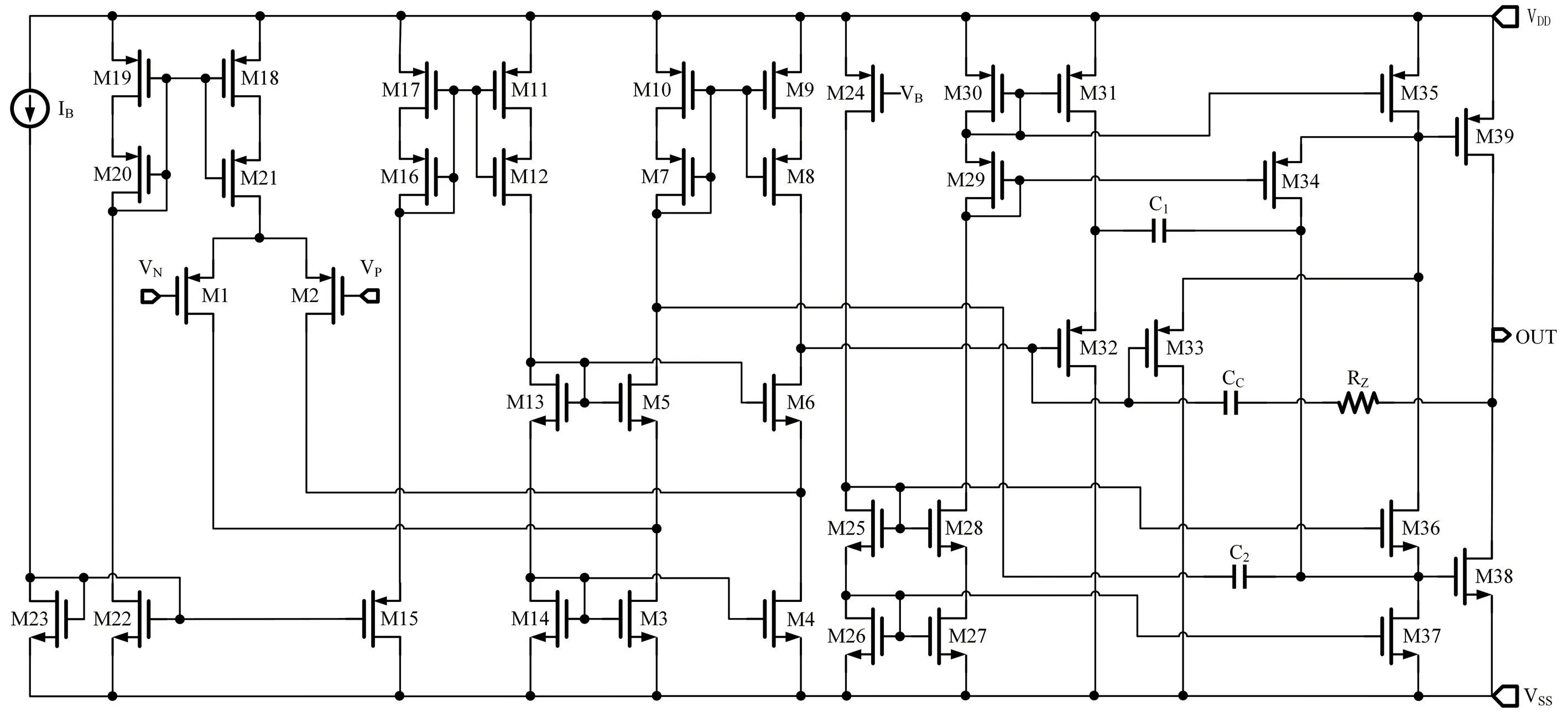

1.4 电路整合

本设计主要由单一PMOS 差分对输入的折叠共源共栅结构和AB 类输出级电路组成,除此之外还有偏置电路以及频率补偿电路,整体电路原理图如图5所示。

图5 整体电路原理图Fig.5 Overall circuit schematic

输入级偏置电路通过电流镜M23 复制电流源IB的电流,提供栅压给M22 与M15。自级联电流镜M18、M19、M20、M21 复制M22 的漏电流给差分对提供尾电流;自级联电流镜M11、M12、M16、M17 复制M15 的漏电流给M13、M14 提供偏置电流,M13 为共栅极提供偏置,M14 给折叠点电流源提供偏置;输出级偏置电路M25、M26 以M24 的偏置电流为参考,复制给M27、M28 流进M29、M30,分别为M34、M35、M36、M37 提供偏置。

电路存在多个极点,采用密勒补偿技术,使主次极点分离,通过密勒补偿后系统主极点近似为:

式中:Rout1表示第一级输出阻抗;Av2表示输出级的低频增益。Rout1、Av2分别可表示为:

式中:rO表示MOS 管的小信号输出电阻;gmb表示MOS 管的体效应跨导。

在运放输出端形成次极点可近似表示为:

式中:CL表示输出节点负载电容与寄生电容的总和;Rout2表示第二级输出阻抗,如式(25)所示:

由式(21)和(24)可以看出,主次极点被分离。当次极点在单位增益带宽范围外时,系统可看作单极点近似。

2 电路仿真分析

本设计在Cadence 平台下使用Spectre 仿真器验证,在温度27 ℃、电源电压5 V、共模电压2.5 V、负载1 MΩ 的条件下(如无特殊说明)仿真运算放大器的多项性能参数。

仿真运算放大器的共模输入范围曲线如图6 所示,输入共模电压范围为0.0027~4.995 V,表明运算放大器能够实现轨到轨输入共模范围。

图7 是仿真M1 阈值电压随共模输入电压变化的范围,阈值电压从-0.596 V 变化到0.238 V。

图7 M1 阈值电压随共模输入电压变化仿真结果Fig.7 Simulation results of transistor M1 threshold voltage change within common-mode input voltage

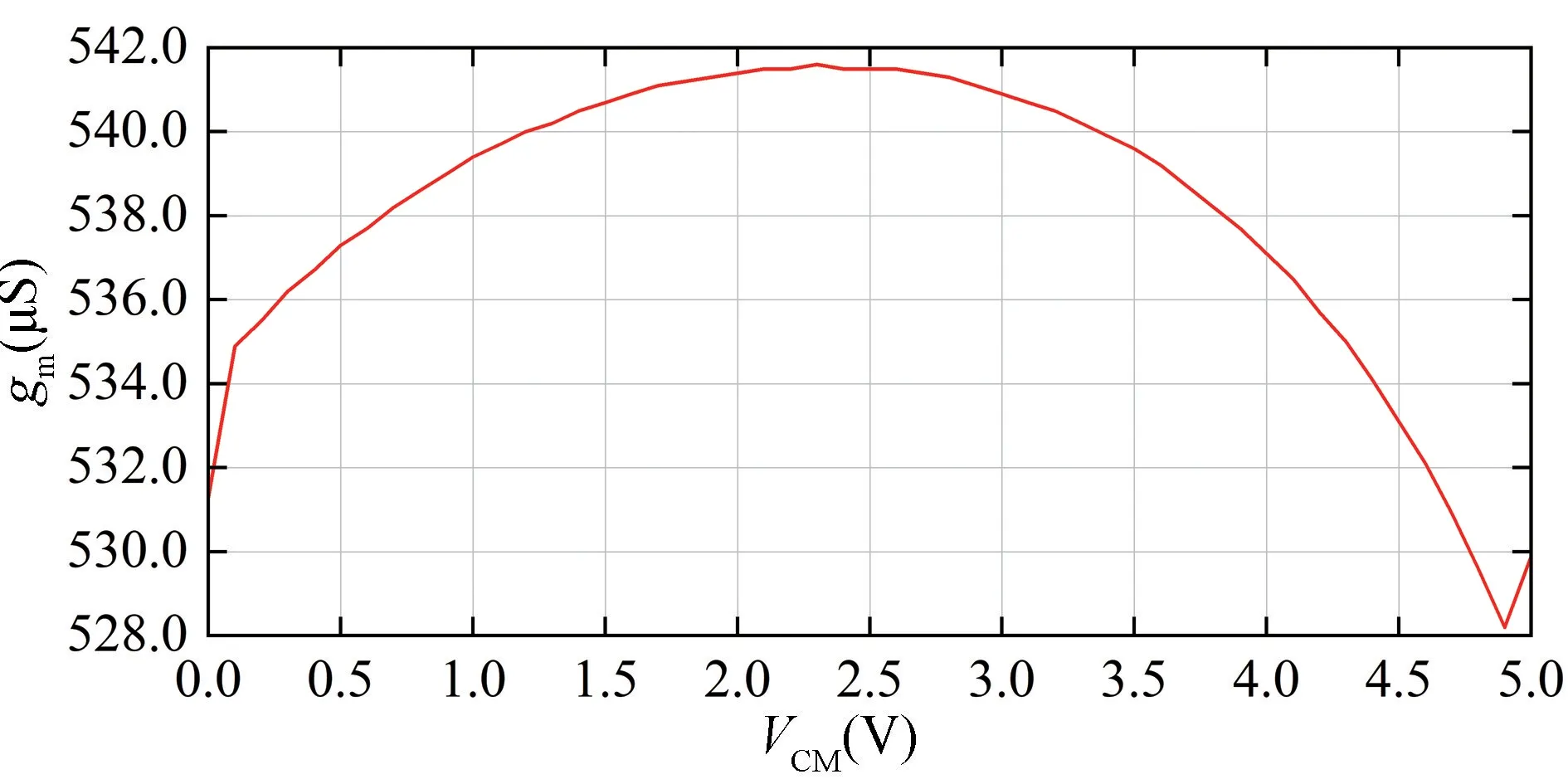

图8 是仿真输入管M1 在共模范围内的跨导变化,在整个共模输入范围能够实现跨导变化不超过3%。

图8 输入管M1 的跨导变化Fig.8 Transconductance change of input transistor M1

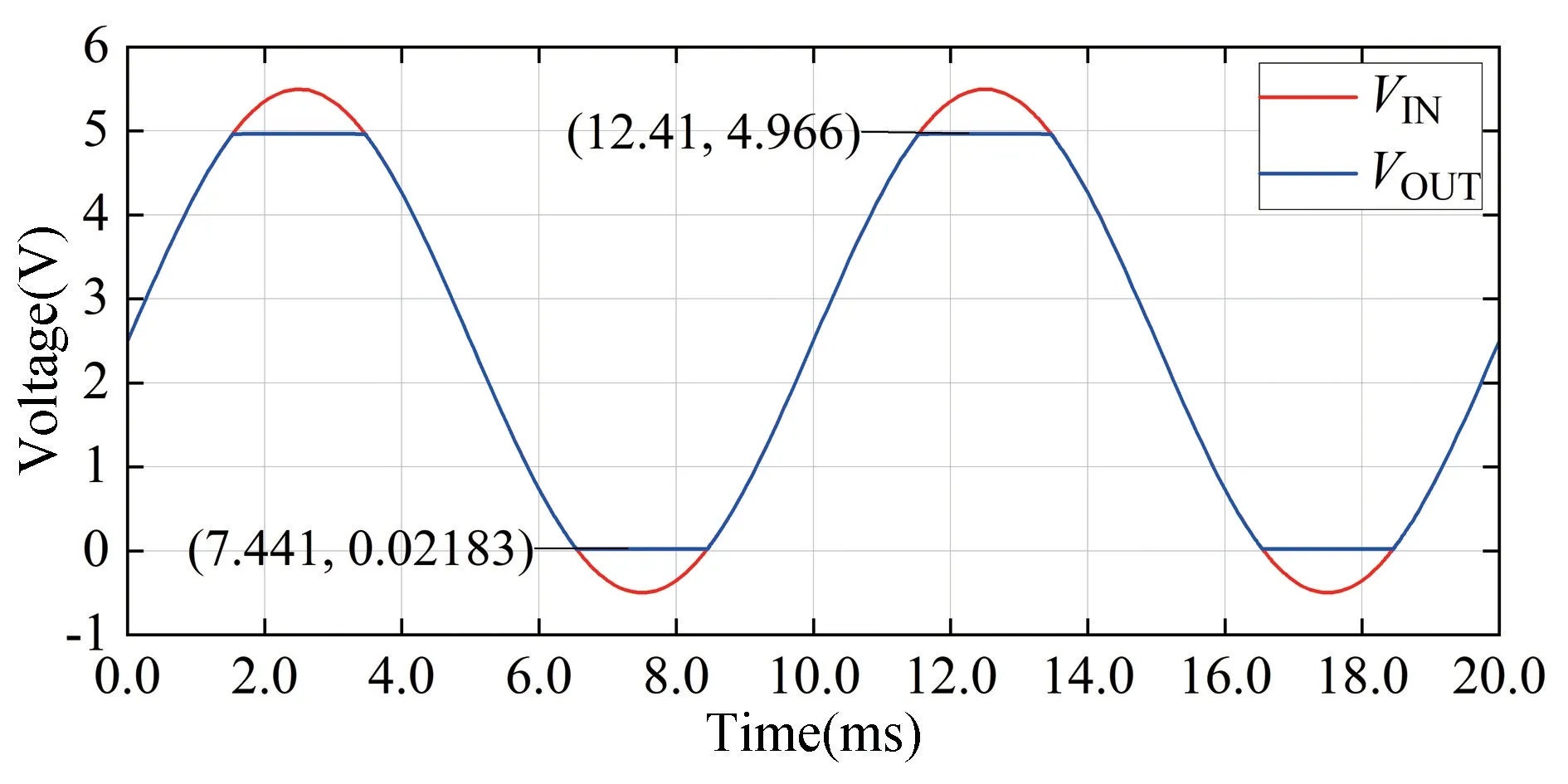

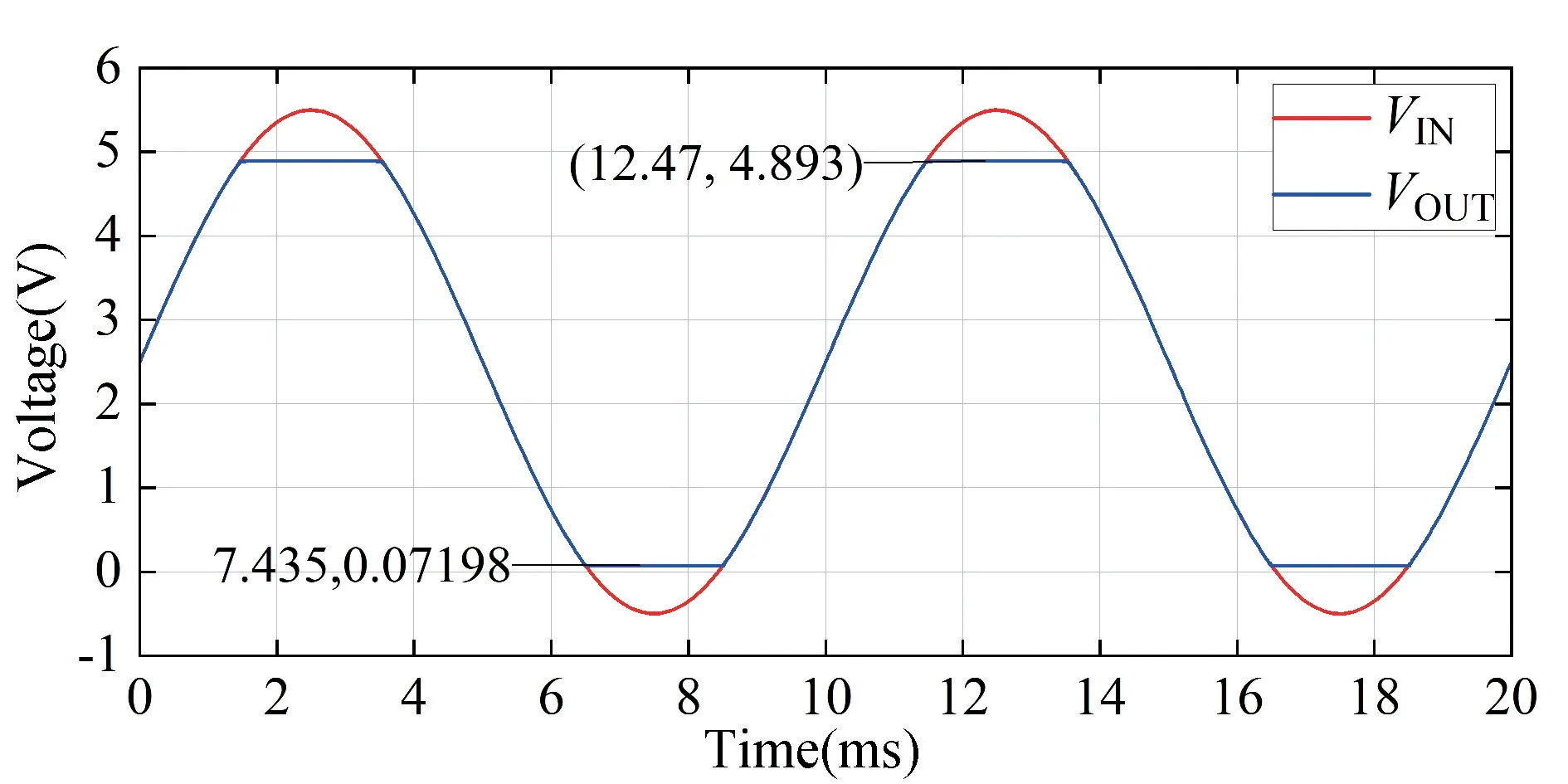

输入幅值3 V 的正弦波,负载分别为2 kΩ 与600 Ω,运算放大器采用电压跟随器形式测试输出电压摆幅,仿真结果如图9 和10 所示。结果表明,在轻负载的情况下,运算放大器的输出摆幅能够实现轨到轨满摆幅输出。

图9 2 kΩ 负载输出摆幅仿真结果Fig.9 Output swing simulation results at 2 kΩ load

图10 600 Ω 负载输出摆幅仿真结果Fig.10 Output swing simulation results at 600 Ω load

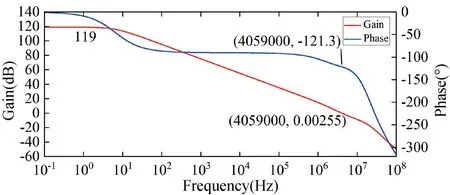

运算放大器交流特性仿真结果如图11 所示。结果显示开环增益为119 dB,相位裕度为58°,单位增益带宽为4.059 MHz,表明运算放大器具有较大的开环增益,系统稳定性好。

图11 运算放大器交流特性仿真结果Fig.11 Simulation results of the op-amp AC characteristics

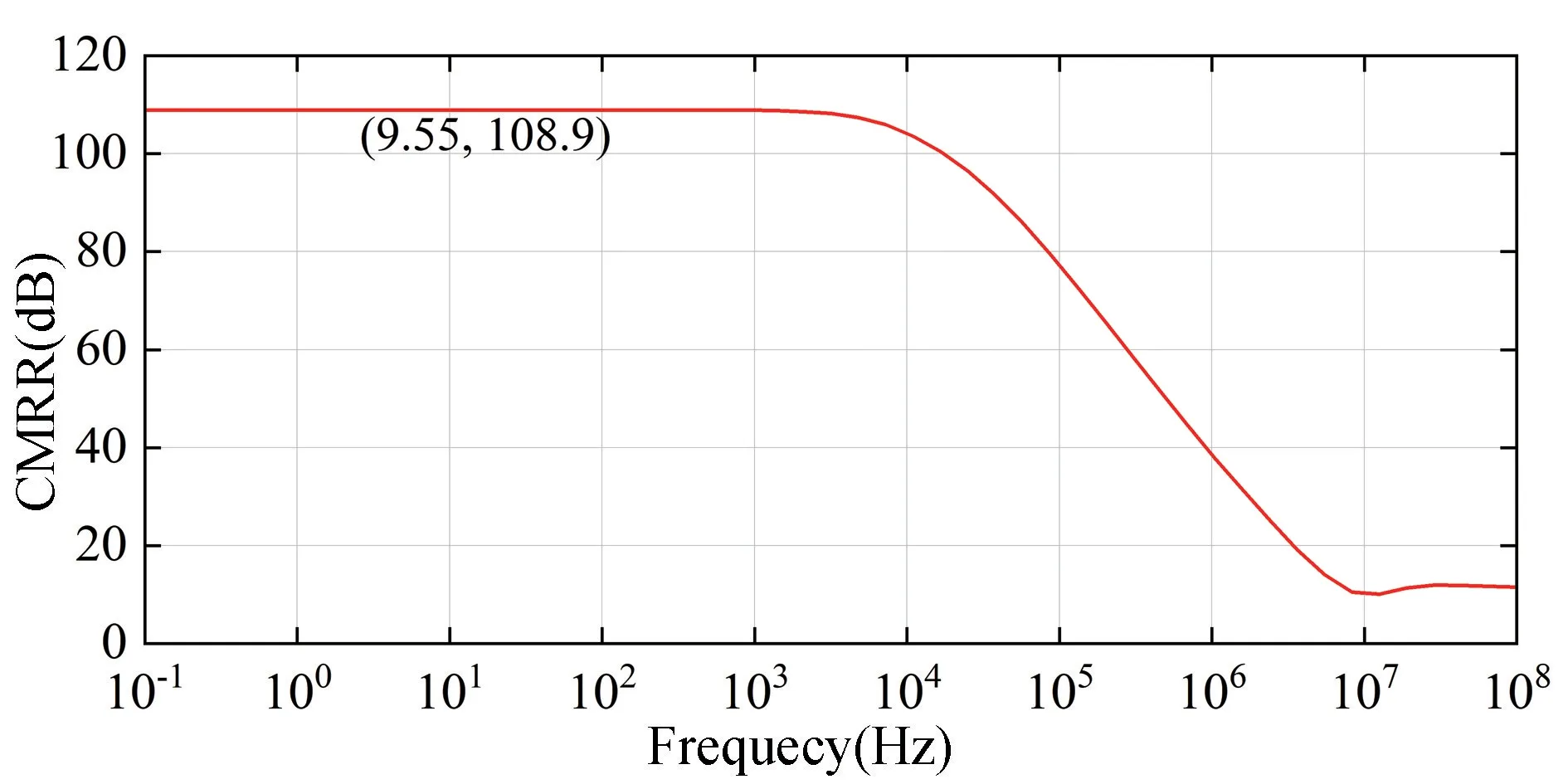

共模抑制比(CMRR)的仿真结果如图12 所示。结果显示CMRR 为108.9 dB,表明运算放大器对共模信号抑制能力较强。

图12 共模抑制比仿真结果Fig.12 Common mode rejection ratio simulation results

3 结论

传统轨到轨运算放大器输入级采用互补双差分对,需要恒跨导技术恒定输入级的跨导,电路结构复杂。本文提出的轨到轨输入运算放大器,采用单一PMOS差分对的折叠共源共栅输入级结构,通过体效应调节阈值电压实现轨到轨的共模输入范围,共模输入范围内跨导恒定,结构简单易于实现;输出级采用AB 类实现轨到轨的输出摆幅。经仿真验证,开环增益为119 dB,相位裕度为58°,共模输入范围为0.0027~4.995 V,共模输入范围内跨导变化小于3%。该运算放大器适用于汽车传感器、速度传感器、压力传感器等模拟电路信号放大领域。