一种低温漂的无运放带隙基准电压源

熊 辉,张 涛,刘 劲

(武汉科技大学 信息科学与工程学院,湖北 武汉 430000)

带隙电压基准(BGR)广泛应用于模拟和数模混合信号电路,如AD 转换器、功率转换器和闪速存储器。这些电路性能的好坏直接取决于BGR 的特性,即温度系数(TC)、电源抑制比(PSRR)、温度范围(TR)、精度、功耗等[1]。因此需要设计一个不受温度及电源电压变化而影响的带隙基准电压源[2],为上述各种电路提供稳定的参考源,从而保证整个电路能够稳定地工作。

传统的带隙基准结构一般可以划分为有运放带隙基准与无运放带隙基准,有运放结构的带隙基准往往是利用运放的“虚短”特性对电路进行钳位,但运放的使用会让带隙输出的精度受到运放失调电压的影响,同时还增加了设计的复杂性,消耗了更多的功耗,引入了新的噪声。而传统的无运放结构通过电流镜进行钳位,从而避免了运放的使用,但是由于沟道调制效应的原因,带隙输出电压精度不高,温度系数往往较大。对于传统无运放带隙基准电压源温度特性差的问题,An 等[3]提出用分段曲率补偿技术来改善无运放带隙基准的温度特性,但该电路结构设计复杂,所用芯片面积较大。而米磊等[4]则利用MOS 管在亚阈值区的温度特性来对无运放带隙基准在不同的温度段内进行补偿,但在实际的工艺中,亚阈值区的MOS 管不易控制,该方法实现上有难度。

针对上述问题,本文参考传统带隙基准电压电路,设计了一种低温漂的无运放带隙基准电压源电路,利用电流镜与环路负反馈进行钳位,避免了使用运放所带来的失调电压对电路的影响,还简化了电路结构,节省了芯片面积。同时利用不同温度系数的电阻对带隙基准中负温度系数电压的非线性项进行曲率补偿,改善了带隙基准输出的温度特性,提高了输出精度。

1 传统带隙基准电路结构

带隙基准电压的基本原理是将温度系数相异的两种电压通过合适的比例相加,从而得到零温度系数的基准电压[5]。

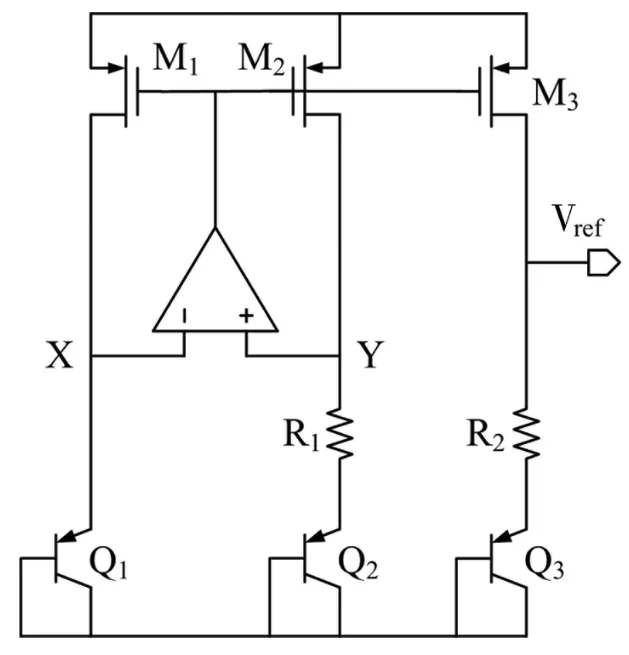

图1 所示为传统有运放带隙基准电路结构[6],图中M1、M2、M3构成电流镜,Q1和Q2为发射极面积成比例的三极管,由于运放和电阻反馈网络的存在,使得电路处于深度负反馈状态,迫使运放两输入端的电压相等,此时M1、M2流出的电流大小相同。相同的电流流过Q1、Q2,使得Q1与Q2的基极-发射极电压之差ΔVBE作用于电阻R1上,产生了PTAT(Proportional to Absolute Temperature)电流。该电流通过电流镜复制到输出,通过电阻R2转为PTAT 电压,与Q3的负温度系数电压VBE相叠加,得到基准输出Vref。

图1 传统有运放带隙基准电路Fig.1 Traditional bandgap reference circuit with operational amplifier

传统有运放带隙基准结构,对于运放的设计需求高,需要高增益、低失调电压的运放,同时运放本身的频率补偿会对整个环路产生影响,增加了环路频率补偿设计的难度。

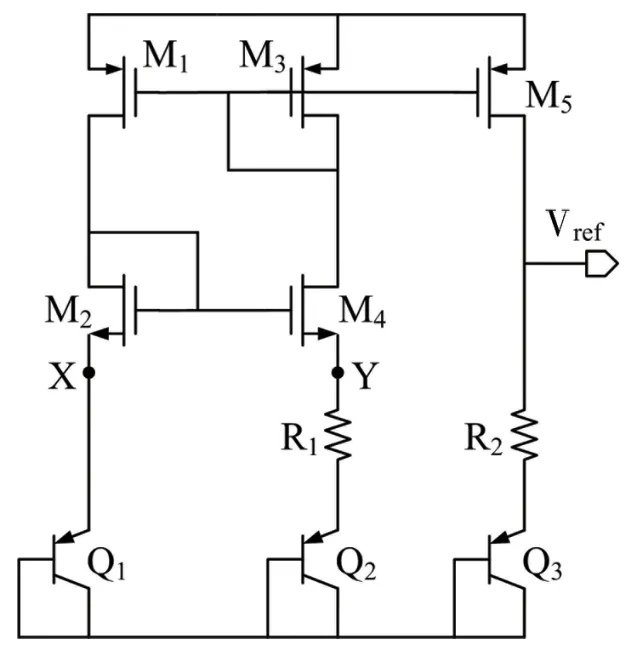

图2 所示为传统无运放带隙基准电路结构[6],其中M1、M3、M5的宽长比相等,M2、M4的宽长比相等,与有运放带隙基准结构不同之处在于,图2 通过M1~M4构成的电流镜及反馈环路对X、Y两点进行钳位。电阻R1取值较大,Q1和Q2发射极电压的差值ΔVBE作用于电阻R1上,产生PTAT 电流,该电流很小,相应地电阻R1上的压降很小,因此M4管的源端电压与VBE2大致相等,流过Q1和Q2两条支路的电流相等。则带隙基准电压Vref可以表示为:

图2 传统无运放带隙基准电路Fig.2 Traditional bandgap reference circuit without operational amplifier

根据式(1)可知,电阻R1与R2的比值及N值对带隙基准输出的影响较大,通过选取合适的比值,可以得到一阶的带隙基准电压。与传统有运放带隙基准相比,无运放带隙基准没有额外的功耗损耗,电路里所有的电流都用来直接生成Vref。同时无运放带隙基准结构简单,不需要设计复杂的运算放大器,节省了芯片面积。但由于MOS 管漏端电压的差异,导致无运放带隙基准的线性调整能力较差。

2 带隙基准电压源设计

本文在传统无运放带隙基准电路的基础上设计一种新型的低温漂无运放带隙基准电路,图3 所示为带隙基准的整体电路图,电路主要由四个模块构成,从左到右分别为启动电路模块、偏置电路模块、宽动态范围Casecode 电流镜模块和带隙基准核心模块。

图3 低温漂无运放带隙基准电压源电路Fig.3 The bandgap reference circuit with low temperature drift and without operational amplifier

2.1 启动电路与偏置电路

由于偏置电路和带隙基准核心电路中可能存在一个或者多个简并点,这些简并点的存在可能让电路处于零电流状态,或者不确定状态,为使带隙基准电路摆脱简并点,设计了如图3 所示的启动电路。电源上电时,整个电路处于零电流状态,电阻R1上基本无压降。此时EN 为高电平,于是M2管导通,形成对地通路,P1支路开始导通。M3管的栅极电压被拉低,低至M3管的栅源电压大于阈值电压时,P2支路导通。此时有电流流入Q3管的基极,开始驱动Q3管,Q3逐渐导通,并放大基极电流开始为电容C1充电,启动电路有电流开始输出。根据Q1和Q2的BE 结压降可知开启电压Vstart如式(2)所示:

启动电流逐渐注入偏置电路。为了增强基准输出的线性调整能力,本文的偏置电路采用经典Widlar 带隙基准结构,得到与电源电压无关的偏置电流。图3中Q4、Q5和R5构成基准核心,基准对管Q5与Q4的发射极面积之比为N∶1。启动电流流入Q4、Q5的基极,促使Q4、Q5导通,此时Q4与Q5基极-发射极电压之差作用在R5上产生PTAT 电流,电流大小如式(3)所示:

PTAT 电流通过电流镜映射给P3支路,此时A 点电位的大小如式(4)所示:

当Q3的发射极电压VA高于开启电压Vstart时,Q3截止,此时启动电路不再给偏置电路提供电流,启动过程结束。

2.2 宽动态范围Cascode 电流镜

为了提高镜像电流的精度,减少由于沟道长度调制效应导致的电流误差,电路设计中通常采用共源共栅电流镜结构,以较大的输出阻抗来抑制电压波动的影响。但传统共源共栅电流镜的输出电压裕度不够,无法在低压环境下正常工作。于是本文采用了在Cascode 电流镜的基础上改进得到的宽动态范围结构Cascode 电流镜。图4 所示为具体电路结构[7],其中M10~M13构成电流镜的主体部分,与传统共源共栅电流镜的结构不同的是,M11、M13的栅极电压由M12的漏极电压Vx提供,而M10、M12的栅极电压由M7构成的偏置电路提供。

图4 中M7管为了电源上电后,能够工作在饱和区,将其栅漏极短接,连接成二极管形式。同时为了使M10~M13均工作在饱和区,则Vb必须满足一定条件,M12要工作在饱和区则:

如若要M13工作在饱和区则有:

又由式(5)和式(6)可得:

当VGS13-VTH13≤VTH12时,式(7)成立。同时由式(7)可知Vb的最小电压为:

又M10~M13的宽长比如下:

则M10~M13四管的阈值电压与过驱电压相同,Vb的最小电压则可以重新表述为:

又从图4 中可知:

联立式(10)与式(11)可得:

又由于VOD7可以表示为:

式中:μn为电子迁移率;COX为单位面积的栅氧化层电容。由式(12)与式(13)可得,M7与M13的宽长比如下:

2.3 带隙基准核心电路

如图3 所示,三极管Q6、Q7、Q9和电阻R6~R9构成了带隙基准核心电路,Q6与Q7的发射极面积比为1∶N。M17和M18是镜像电流,两管的尺寸比为1∶2。为了减少MOS 管M17与M18的沟道长度调制效应,使其流过Q6与Q7的电流匹配性更强,在设计时将M17与M18的管子尺寸取较大的值。而M20作为M21共源级放大器的电流源负载,为了使M20以较小的VDS来保证M20管处于饱和区,M20管的长在设计时取较小的值。由于M17、M18与M20的尺寸不同,因此 M17、M18与M20采用了两处不同的镜像电流。传统带隙基准通过运放钳住X、Y点电压使其相等,来产生PTAT 电流,需要额外设计高性能的运放,增加了整个电路设计的复杂性,而且还带来了运放失调电压以及环路稳定性的问题。本次设计舍弃了运放,使尺寸相同的M19、M21管流过大小相同的电流,来控制两管的栅压相等即X与Y点电压相等,来产生PTAT 电流。三极管Q6、Q7的基极-发射极电压差ΔVBE可以表示为:

式(15)中电流I1与I2均为IPTAT电流镜像而来,三者比例关系为1∶2∶1。ΔVBE又通过电阻R8得到正温度系数电流IPTAT1:

IPTAT1为正温度系数电流,流经电阻R7、R8、R9产生PTAT 电压,三极管Q9的基极-发射极电压VBE9具有负温度系数,两者电压叠加得到带隙输出电压,表达式如下:

其中VBE可以表示为[8]:

式中:VG(T)表示硅在任意温度T时的带隙电压;VBE(T0)表示在温度T0下三极管基极-发射极电压;VG(T0)表示硅在温度T0时的带隙电压;η是一个与温度无关的工艺参数;α为三极管集电极电流与温度的关系常数。将式(18)按泰勒级数展开可得:

式中:a0,a1,a2,…为与温度无关的常数。从式(19)中可以看出,三极管的VBE电压中不仅存在与温度相关的一阶项,还有与温度相关的高阶项。

在本次设计所使用的工艺库中,有许多不同类型的电阻,这些电阻的温度特性也不尽相同。利用这些不同温度系数的电阻,产生与温度相关的电压分量,来抵消VBE(T)中的高阶项电压,从而降低带隙基准的温度系数。

式(17)中,R6~R9为高阻多晶硅电阻;R5为低阻多晶硅电阻,因此(R7+R8+R9)/R8与温度不相关。高阻多晶硅电阻与低阻多晶硅电阻都为负温度系数电阻,但二者的负温度系数不相同,所以-R6/R5与温度相关。设R6的温度系数为-K1,R5的温度系数为-K2,则-R6/R5的泰勒展开式可以表示为:

将式(20)代入式(17)得到温度补偿后带隙基准输出电压与温度的表达式:

从式(21)中可以看出,式中有关于温度的高阶非线性项,通过对R6与R5进行合理的取值,可以与VBE9中的高阶温度项进行补偿,改善带隙基准电压的温度特性,降低其温度系数。

图3 中通过晶体管M20、M21,三极管Q8和电容C2一起构成一个负反馈回路,对带隙基准输出进行动态实时调节,确保带隙基准输出的稳定。其具体工作原理如下: 当带隙输出电压Vref升高时,Q6的基极电压也相应升高,流入Q6基极的电流也随之增大,相对应的Q6集电极电流也应该变大,但由于Q6集电极电流由电流源M17所决定,因此Q6的集电极电压下降,即M19的栅端电压降低,又由于M19所流过的电流由M17和M18两个电流源所确定,所以导致M19的漏端电压增加,进一步M21的栅端电压增大,Q8的基极电压减小,Vref减小。

3 仿真结果与分析

本文的设计基于华虹0.35 μm BCD 工艺库,所有的电路仿真验证都采用Cadence Spectre 仿真工具。本电路的正常工作电压为1.7~5.5 V,温度范围为-55~125 ℃。

常温下,对电源电压从0~5.5 V 进行直流扫描仿真,仿真结果如图5 所示,带隙基准电路正常工作的最低输入电压为1.7 V,输出电压为1.203 V,同时在1.7~5.5 V 的供电电压下均可稳定输出。

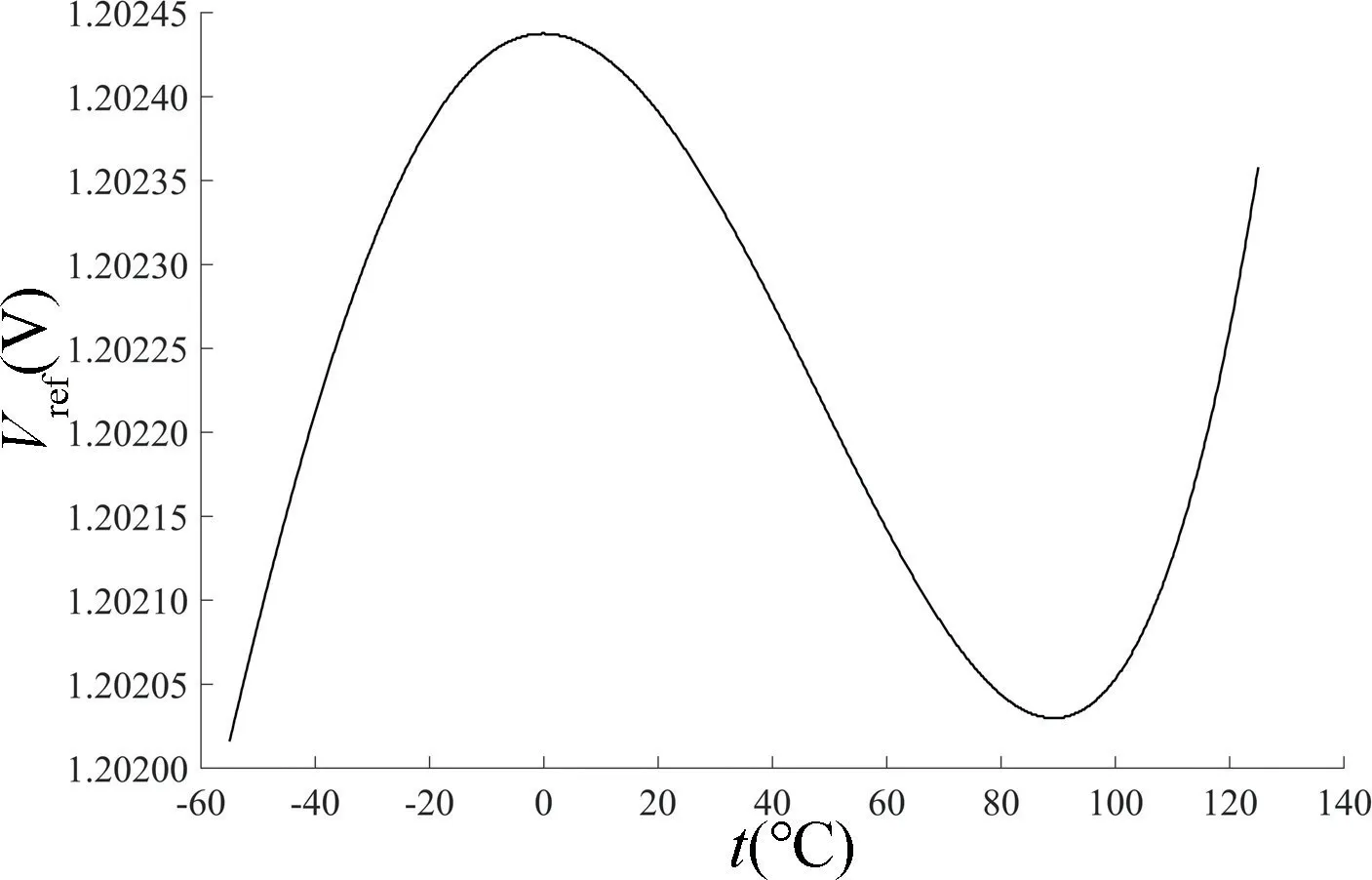

在5.5 V 的工作电压下,对带隙基准输出进行温度特性仿真,温度仿真的范围为-55~125 ℃,仿真结果如图6 所示,带隙基准经过温度补偿后,有两个近似于零温度系数温度点,带隙基准输出电压的波动约为422 μV,经过计算在-55~125 ℃的温度范围内,带隙基准的温度系数为1.949×10-6/℃。

图6 带隙基准温度特性曲线Fig.6 Temperature characteristic curve of the bandgap reference

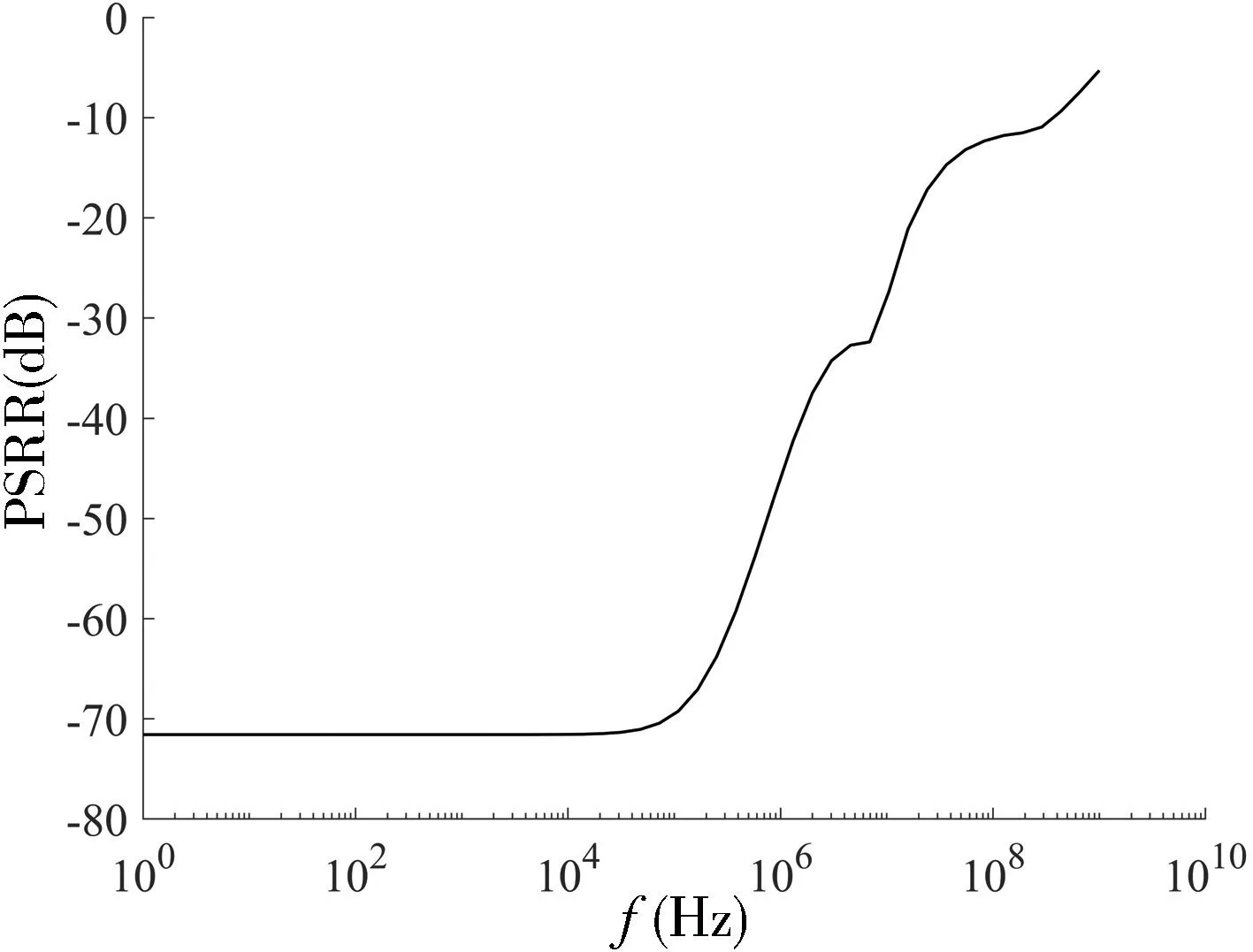

仿真设置5.5 V 的大信号,叠加1 V 的交流小信号,频率范围为1 Hz~10 GHz。仿真结果如图7 所示,低频10 kHz 时电路的PSRR 为71.5 dB,1 MHz 时电路的PSRR 仍有46.3 dB。

图7 带隙基准PSRR 特性曲线Fig.7 PSRR characteristic curve of the bandgap reference

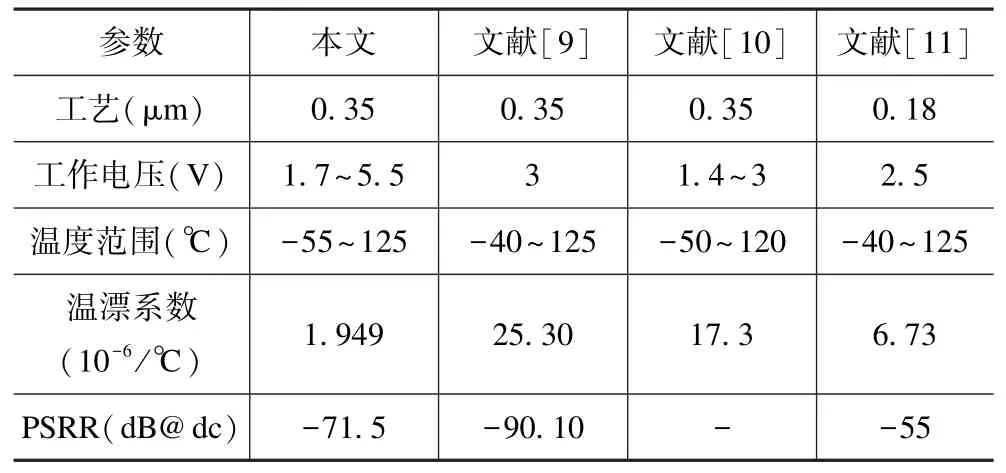

本文所设计的无运放带隙基准电源与近几年其他文献中的无运放带隙基准电压源的性能参数对比如表1 所示。从表1 中可以看出,在工艺制程差不多的情况下,本文所设计的带隙基准电路的工作电压比文献[9]、文献[10]以及文献[11]均要广;在-55~125 ℃范围内温漂系数也明显优于文献[9]、文献[10]与文献[11]。

表1 本文带隙基准源与其他文献的性能参数比较Tab.1 Comparison of performance parameters between the bandgap reference source in this paper and other literatures

4 结论

通过对传统带隙基准电路的研究,本文设计了一种低温漂的无运放带隙基准电路。本电路无需设计复杂的运放,降低了设计难度。同时利用不同电阻的温度特性对三极管VBE的高阶项进行曲率补偿,大大降低带隙基准的温漂系数。在华虹0.35 μm BCD 工艺下,仿真结果表明,其温度系数在-55~125 ℃内为1.949×10-6/℃。本文设计的带隙基准可应用于LDO等高精度要求的设计中。