基于FPGA的多信源可变速率通信系统

黄崇宇,罗义军,李 劲

(1.武汉大学电子信息学院,湖北武汉 430061;2.武汉纺织大学电子与电气工程学院,湖北武汉 430200)

0 引言

数字通信技术应用越来越广泛,信源、调制体制、传输速率是设计数字通信系统时需要考虑的重要因素。

不同应用场合下系统信源输出的信号类型各不相同。铁路应急通信、高速公路收费系统等采用图像信源[1];舰船航行异常监控等采用视频信源;农业饲养厂家禽养殖、音频信号检测评估等采用音频信源;煤矿救援机器人信息联络、轨道交通安全保障等采用数据文件信源。

不同场合对调制方式的要求不同,BPSK、QPSK是常用的调制方式,BPSK主要应用在卫星相干激光通信[2]、水下通信技术、油气田开发、电力通信系统载波智能恢复等场合,QPSK主要应用在数字卫星广播[3]、微波高速调制电路、高速大气激光通信等场合。

10 Kbit/s~20 Mbit/s满足了数据、图像、音频、视频等各个信源的码速率要求,可应用于无线局域网[4]、广播电视工程、无源物联网[5]、远程视频会议等领域。系统为支持多种信源,应采用可变速率的方式进行编码。目前大多数的数字通信系统在多信源、多调制体制和可变速率这几个方面无法做到同时兼容,通用性较低且不易于扩展[6-9]。

在此背景下,本文设计了一种兼容高低码速率、传输速率可变、信源多样化、调制体制可选的数字通信系统。系统核心为FPGA+ADC/DAC[10-12],支持BPSK和QPSK2种调制体制,传输速率在10 Kbit/s~20 Mbit/s内可变,支持数据文件、图像、音视频等多种信源,可适用于不同场景,灵活性高。本系统还可在信源端进行扩展,作为光学探测系统,将光信号转变为电信号后进行远距离传输。

1 系统总体设计

为支持多种信源,发送端需设置信源选择模块,根据信源种类采取不同传输方式。对于音视频信号的传输,发送端和接收端需要实现对音视频信号的采集处理和还原显示。FPGA 内部的逻辑规模扩大,时钟频率高,并且拥有并行处理能力、内部延时短、配置接口灵活等优点[13],配合ADC / DAC器件,能很好地满足中频传输的需求。考虑到某些场合发送端和接收端会间隔一定距离,音视频模块和中频传输模块之间需要使用交换机来传递信息。因此,整个系统由信源选择模块、信宿接收模块、中频传输模块、交换机、上位机组成,如图1所示。

图1 系统总体架构

工作流程为:传输音视频时,信号经音视频采集、编码压缩后,送到中频传输模块,进行RS编码和中频调制,经D/A转换和带通滤波,得到70 MHz中频信号,再经射频模块发出;接收端射频模块接收信号,70 MHz中频信号经带通滤波和A/D转换后,进行中频解调和RS译码,再经过解码解压缩后,即可送到显示器,从而实现视频显示和音频输出。RS编译码和中频调制解调均在FPGA上实现,音视频模块与交换机之间通过以太网口进行连接,中频传输模块的AD采集板和DA转换板上为USB接口,经过USB转以太网口后与交换机连接。传输文件和图像时则不启用发送端和接收端的音视频采集和播放设备。

本系统还可用作测试平台,工作流程同上。如将待测试的上变频器替换至系统的射频前端,再测试整个系统的文件、视频的传输情况,若误码率低且视频延时小,说明该上变频器性能良好。

本系统采用模块化设计,具有较强的扩展性。在信源选择模块添加光电转换器件,则本系统可作为光电探测系统应用于远距离通信场合,如在森林防火视频监控系统中,火灾的根源通常是难以发现的隐火,需要红外热成像仪透过烟雾发现着火点,监控人员通过数字通信系统在远处进行实时视频监控。

2 中频传输模块硬件设计

本系统的核心部分为中频传输模块,该模块包括ADC、DAC、FPGA芯片、时钟子板、USB接口和SDRAM缓存等部分。

SDRAM缓存模块用于缓存接收的解调数据,由芯片MT48LC32M16构成,将SDRAM应用成FIFO的形式,以利于形成大容量缓存。

在采集数据和回放数据期间,需要将数据发送给计算机作进一步的处理和显示。目前基于计算机的总线有许多,比如PCI-Express总线、ISA总线、VME总线、USB总线等,其中PCI-Express总线具有很高的数据传输速率,但是PCI-Express总线的控制十分复杂,而且必须采用插卡形式,本系统中高速数据的运算处理都是在FPGA中进行,得到的较低速率的结果才送至PC进行分析和显示,为了开发的方便性,采用USB2.0总线作为系统与PC机之间通信的接口。USB接口芯片选择CY7C68013,易使用且功耗低。

当视频数据流速率改变时,FPGA内部时钟也要做相应的调整,系统调制解调时需要根据不同码速率变换主时钟。ADF4351芯片的输出频率范围为2.2~4.4 GHz,有一个分频回路,能实现 1、2、4、8、16、32、64分频,产生低至35 MHz的RF输出频率,可以很好地满足系统设计需求。芯片主要由SPI控制时序,拥有三线串行接口CLK、ATA、LE。要写入数据到ADF4351的寄存器,要先将LE置低,然后在CLK的上升沿依次写入DATA的值,DATA的值就是配置ADF4351的值,写完一个寄存器(32位)后,LE要拉高,下次再配置寄存器时LE继续拉低配置,依次类推配置完6个寄存器。

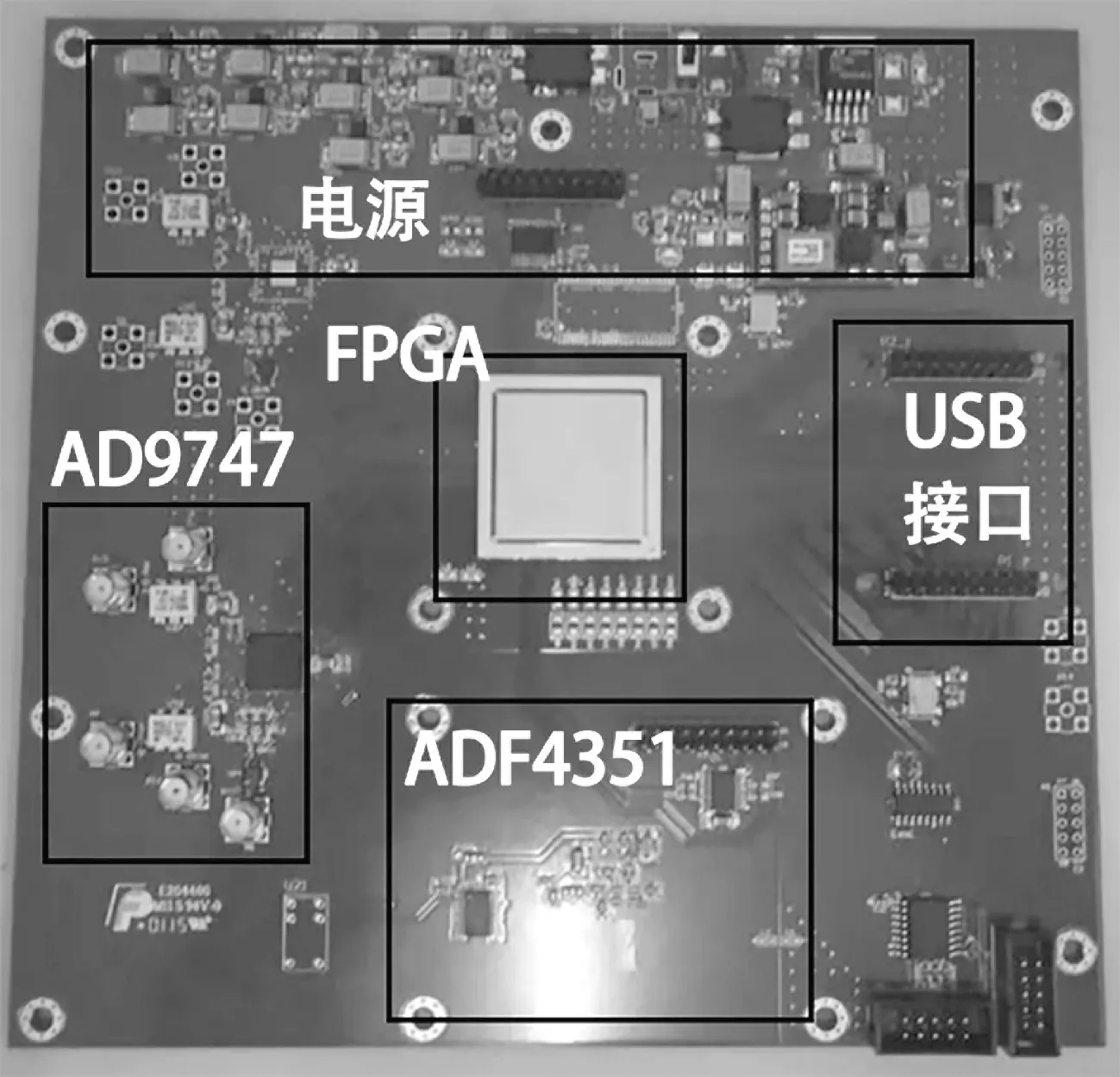

中频信号中心频率为70 MHz,为达到足够的杂波和谐波抑制,采样速率要在3倍以上。最大采样速率达到250 MSPS、不低于14位的DA转换器芯片有DAC5672A(14位)、AD9747、MAX5878,根据芯片手册中的SFDR(无杂散动态范围)和IMD(三阶交调)参数指标,本系统选用性能最好的AD9747。D/A转换板实物图如图2所示。

图2 D/A转换板实物图

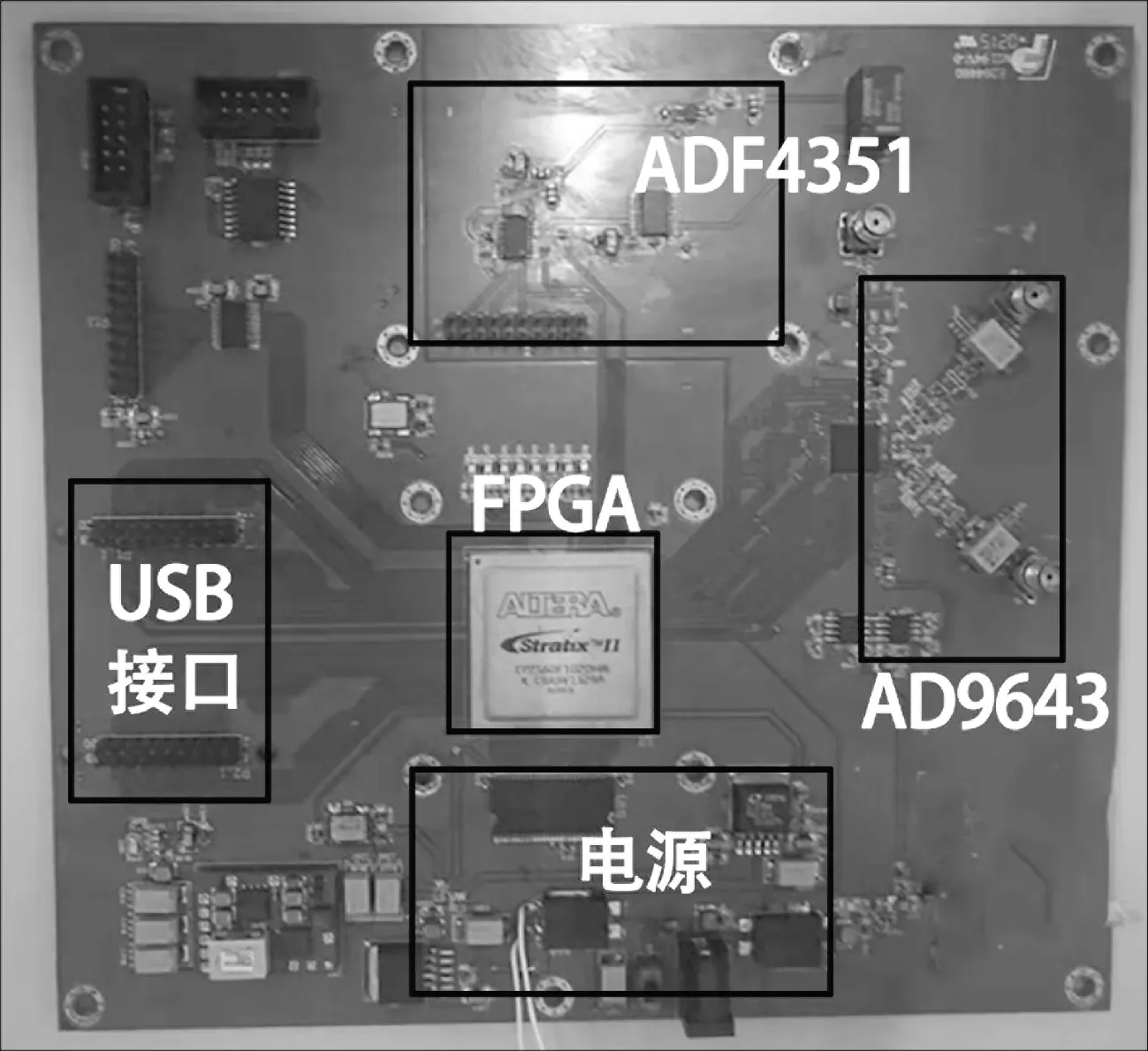

信源和采集板的中频A/D转换器需采用至少为工业级芯片,并满足采样速率和动态范围要求。超过100 MSPS的工业级A/D芯片有ADC14155QML-SP、AD9643、AD9253等,综合信噪比、动态范围和采样率指标,中频A/D转换采用AD9643芯片。AD9643是一款双通道、14位、采样速率最高达250 MSPS的模数转换器,采用多级、差分流水线架构,并集成了输出纠错逻辑。AD9643与AD9747电路一致,数据线和时钟线均为差分等长线。A/D采集板实物图如图3所示。

图3 A/D采集板实物图

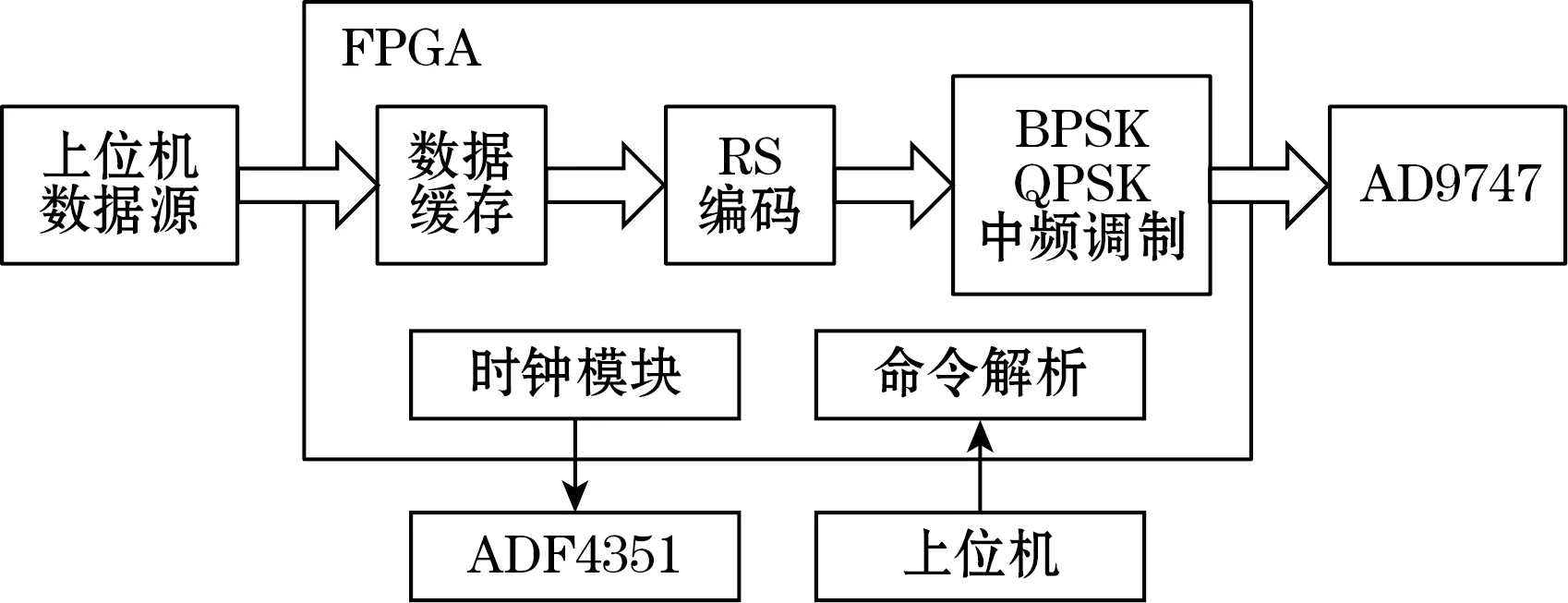

FPGA上所做的工作包括调制解调、RS编码译码、交织解交织、加扰解扰和加噪等,调制段和解调的FPGA逻辑顶层设计结构示意图如图4和图5所示。系统采用块交织的方式,取自FIFO的数据串并转换后送入4路并行RS编码器进行交织,再做并串交换输出数据;解交织是交织的镜像逆过程。m序列是周期最长的线性反馈移位寄存器序列,本系统将m序列产生的随机码本存储到RAM中,每个时钟周期读出RAM中的一个数据,再与串并变换后的码元数据进行异或,即得到加扰后的数据;解扰是和相同的码本再异或一次,与加扰结构一样。调制信源由伪随机序列生成器产生,并且经过符号映射将数据由{0,1}映射到{1,-1},串并变换处理,然后分别对I、Q路匹配滤波,得到基带信号的I路、Q路分量;采用BPSK调制方式不需要进行串并变化,不存在正交分量,令Q路输入输出均为0即可。调制之前,需要对信号进行多级滤波来消除信号旁瓣。BPSK/QPSK的解调都采用Costas环路和Gardner环路的方法,本系统中信号的码速率在10 Kbit/s~20 Mbit/s,为保证解调的性能,解调端的结构统一使用采样速率与符号速率之比为1∶16的环路设计。

图4 调制端FPGA逻辑设计顶层结构示意图

图5 解调端FPGA逻辑设计顶层结构示意图

3 上位机功能与界面

本系统软件上位机分为发送端上位机和接收端上位机,主要实现参数设置、给FPGA发送命令、显示数据对比信息、视频播放等功能。

发送端上位机工作流程为:设置信号类型、调制方式、输出功率和符号速率后,选择传输数据类型,若传输文件或图像,则打开USB发送端程序,直接发送数据;若传输音视频,则打开SDK发送端程序,搜索并初始化摄像机设备,再传输数据。USB发送端和SDK发送端程序界面如图6和图7所示。

图6 USB发送端程序界面图

图7 SDK发送端程序界面图

接收端上位机工作流程为:设置调制方式、符号速率后,选择传输数据类型,若传输文件或图像,则接收文件,进行数据比对统计误码率,直至文件接收完成;若传输音视频,则打开SDK接收端程序,接收数据并重新组帧,再解码播放视频。USB接收端和SDK接收端程序界面如图8和图9所示。

图8 USB接收端程序界面图

图9 SDK接收端程序界面图

4 系统测试

4.1 测试环境搭建

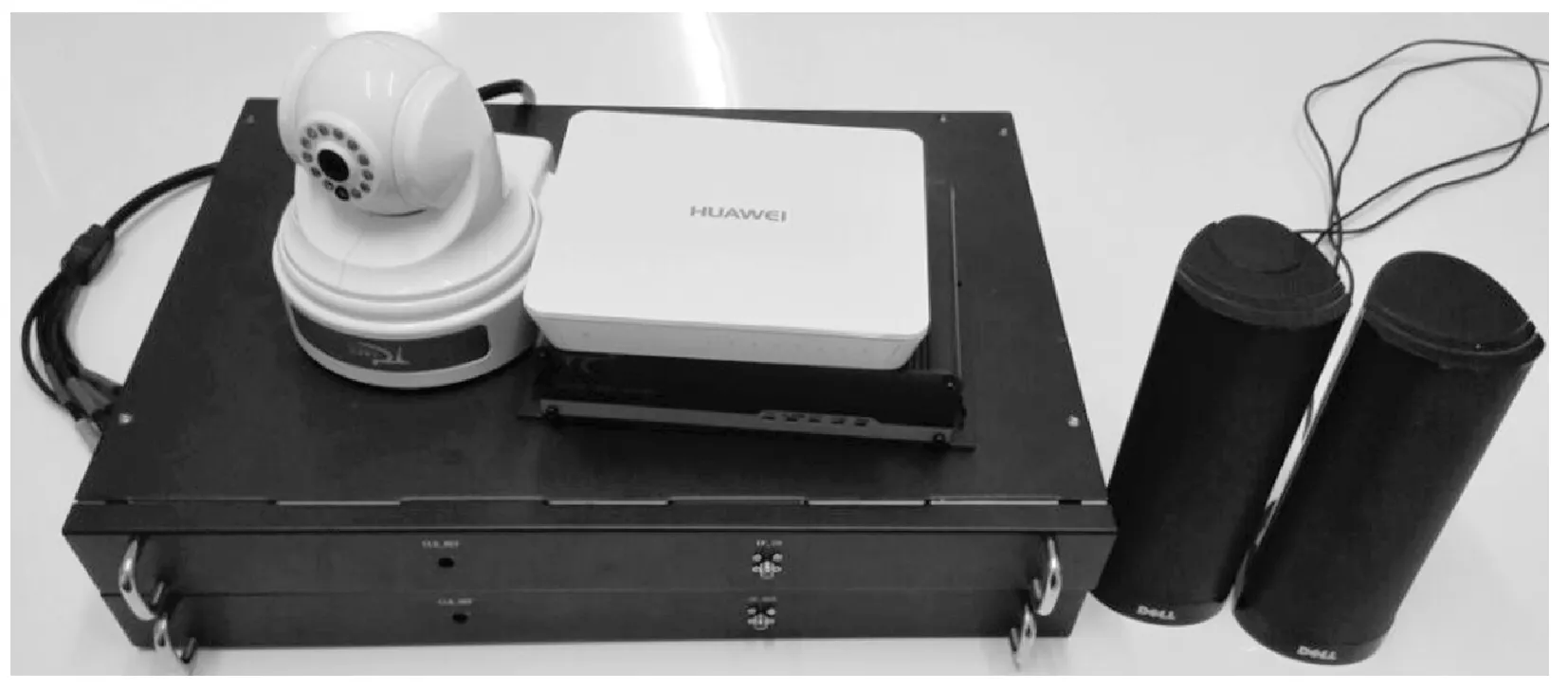

音视频采集和编码压缩采用一体化设备,如130万像素半球型网络摄像机;音视频解码(含解压缩)选用DS-7200HFH-ST系列网络硬盘录像机,该录像机可广泛应用于对高清和网传延时要求高的金融、交通等领域。

系统实物如图10,右侧为2个音箱,左侧上面为网络摄像机和网络硬盘录像机,左侧下面为中频发射机(信道编码和中频调制)和中频接收机(中频解调和信道译码)。

图10 测试环境实物图

4.2 测试结果及分析

4.2.1 资源消耗分析

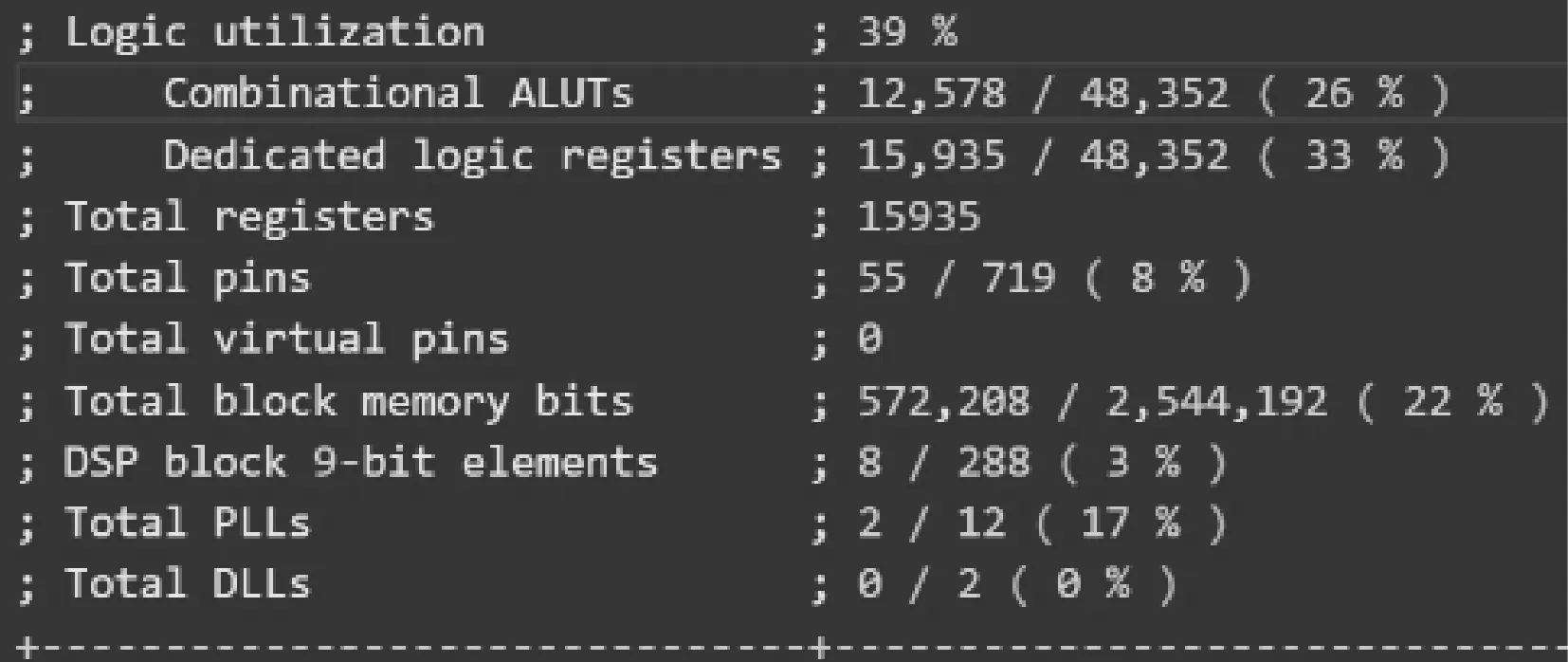

本系统在QuartusⅡ开发环境下完成硬件逻辑设计,QuartusⅡ会生成记录调制端和解调端FPGA资源消耗情况的报告文件,如图11和图12所示。可以看到,调制端和解调端FPGA上的重要资源,如逻辑资源块查找表(ALUT)、逻辑寄存器、锁相环(PLL)等使用率并不高,均有一半以上的空间供其他功能扩展。

图11 调制端FPGA资源消耗图

图12 解调端FPGA资源消耗图

4.2.2 音视频传输延时测试

选取码速率为3 Mbit/s的QPSK调制方式,用图13所示方法测试延时。照片中显示的是当前时刻的计时器的值和摄像头传输显示的计时器值,视频传输的延时就可以用这2个数据的差值表示,即12.30-11.84=0.46 s。

图13 延时测试图

实际的视频传输过程中,由于视频数据H.264的编码方式的限制,视频传输速率不低于2 Mbit/s。表1为不同调制方式不同码速率的视频延时测试表。

表1 视频延时测试表

4.2.3 加噪传输测试

选取码速率为3 Mbit/s的QPSK调制方式,将模拟加噪的信噪比加到7.5 dB,传输1 GB的文件来测试,上位机界面显示误码率为0.000 334 93,与理论误码率0.000 398 796接近,小于理论值的原因是系统加入了RS编译码和交织。加噪前后传输视频的效果对比如图14和图15,可以看出加噪后会出现不清晰的现象,但视频传输图像大体完整,在7.5 dB信噪比下视频传输较正常。

图14 加噪前视频传输效果图

图15 加噪后视频传输效果图

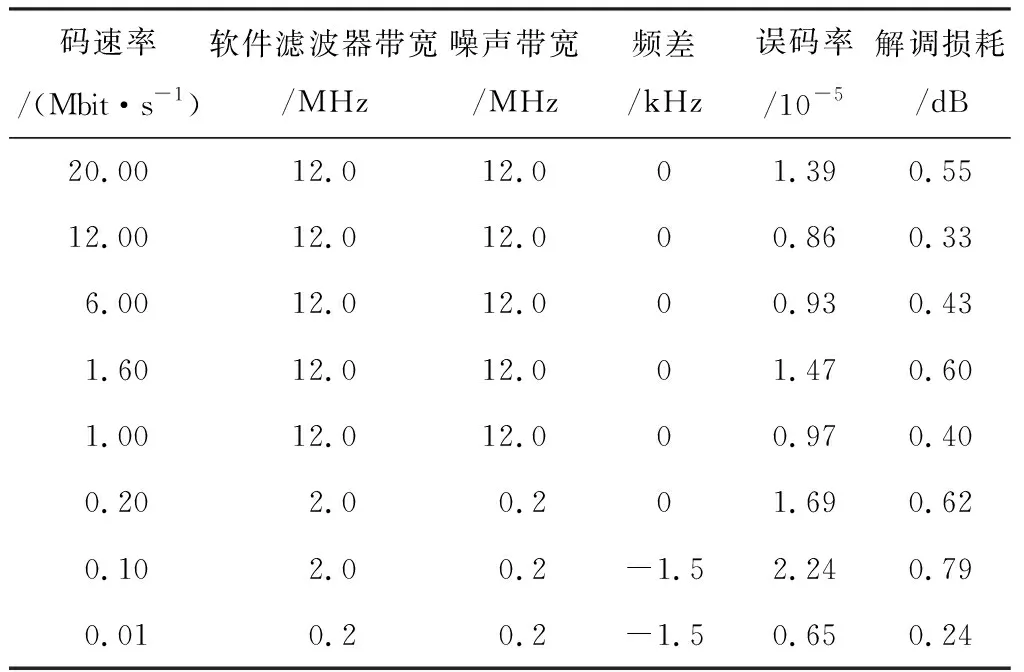

4.2.4 误码率及解调损耗测试

m序列具有良好的伪噪声特性,本系统在发送端和接收端都使用m序列源,接收端m序列源输出的本地序列与解调后的序列完全同步后,进行逐位比较即计算出误码率。发送端上位机设置比特信噪比Eb/N0为10 dBm,接收端根据误码率可计算出实际的Eb/N0,两者之差即为系统的解调损耗。在两种调制体制下,分别测试10 Kbit/s~20 Mbit/s范围内不同传输速率下系统的误码率及解调损耗,测试结果如表2和表3所示。

表2 BPSK误码率及解调损耗测试表

表3 QPSK误码率及解调损耗测试表

一般的调制解调器不能兼容低码速率和高码速率,即便兼容其解调效果也会因码速率变化而变化,尤其在低码速率时解调质量明显降低。为保证解调质量,滤波器带宽需根据码元速率来进行设置,低速率时应减小滤波器带宽,同时也应减小噪声带宽和频差。由测试结果可知,不同调制体制不同码速率下,误码率低,系统的解调损耗均小于0.8 dBm,说明本系统可靠性高,可满足高低码速率下不同信源场合下的传输要求。

5 结束语

本文基于FPGA设计了一种可变速率的数字通信系统,对系统的核心模块中频传输模块和上位机进行了设计和实现,经测试验证,系统能够实现在不同调制体制不同速率下的信号传输,且具有损耗低、稳定可靠的特点,可用于光学传输、视频会议、广播等领域。