一种基于高肖特基势垒的高性能隧穿场效应晶体管

李 鑫,刘 溪

(沈阳工业大学信息科学与工程学院,沈阳 110870)

1 引言

根据摩尔定律,器件数量的增多也将预示着器件尺寸的减小。随着器件尺寸的不断减小,降低功耗成为了集成电路设计的关键问题。现如今,CMOS工艺技术已经进入14 纳米时代[1],尺寸还在继续缩小,力争达到7 纳米。然而,随着器件尺寸的减小,一系列问题也随之而来,例如短沟道效应,即根据源漏区距离不断缩短,沟道内电场的分布发生变化。又例如热载流子注入效应对亚阈值摆幅特性产生影响等问题。在此提出一种具有两侧等号形主控制栅的晶体管结构,并在中间增加辅助栅来更好控制有效沟道长度[2]。传统肖特基势垒金属氧化物场效应晶体管是通过降低势垒的高度来产生大的电流,与此不同的是,本结构通过对禁带电子势垒的提高,降低由热电子激发产生的电流,并增大体硅与源漏电极接触界面作为正向导通的主要传导机制,形成带带隧穿,使器件具有高导通电流、低亚阈值摆幅和低静态功耗的特点,能够实现比传统隧穿晶体管更大的开启电流,而且由于结构的对称性更便于集成。

2 器件工作原理

在对器件的设计中,源、漏电极均采用金属材质,电极与半导体硅接触形成金属结。金属结在源漏区形成阻挡接触即肖特基势垒[3]。载流子发生带带隧穿形成导通电流。

在结构中,有一个两侧主控制栅极和一个中央辅助栅极。两侧的主控制栅极形为“等号”,主要利用带带隧穿作为正向导通电流的主导物理机制,即利用突变金属结在半导体处提供一个比P垣/N垣结更强烈的带带隧穿,同时还能阻挡热电子发射电流。两侧主控制栅极主要控制源、漏区。中央辅助控制栅极的导通机制与传统MOSFET 导通机制相同,为阻挡价带电流的产生,在此特别引入辅助栅结构以控制体硅区。

以N 型场效应晶体管为例,两侧主控制栅极和中央辅助栅极均为正向偏置,带带隧穿所产生的电子空穴对均由源极提供[4]。电子从源极流出,在两侧主控制栅极的控制下汇集在沟道两侧,随着电子不断地增加积累,电子从源极持续流向漏极形成漏电流,使器件导通。相反,保持两侧主控制栅极正向偏置不变,令中央辅助栅极反向偏置,电子同样从源极流出汇集在沟道两侧并流向漏极。但中央辅助栅极反向偏置会阻挡电子流向漏极,使器件处于关断状态。

P 型同N 型原理相同,两侧主控制栅极的中央辅助栅极均为反向偏置,带带隧穿所产生的电子空穴对由源极提供。空穴从源极流出,在两侧主控制栅极的控制下汇集在沟道两侧,随着空穴不断地增加积累,空穴从源极持续流向漏极形成漏电流,使器件导通。反之,保持两侧主控制栅极反向偏置,将中央辅助栅极改为正向偏置,空穴从源极流出汇集在沟道两侧并流向漏极[5]。但中央辅助栅极正向偏置会阻挡空穴向漏极流通,使器件处于关断状态。

3 仿真与分析

使用Silvaco TCAD 半导体仿真软件进行模型结构仿真[6]。结构所采用的模型有玻尔兹曼统计分布函数(Boltzman Distribution Model)、俄歇复合模型(Auger Recombination Model)、肖克基复合模型(Consrh Model)、能带变窄模型(Band Gap Narrowing Model)以及带-带隧穿标准模型(A Standard Band to Band Tunneling Mode Ibbt.std)。

3.1 器件结构及关键参数

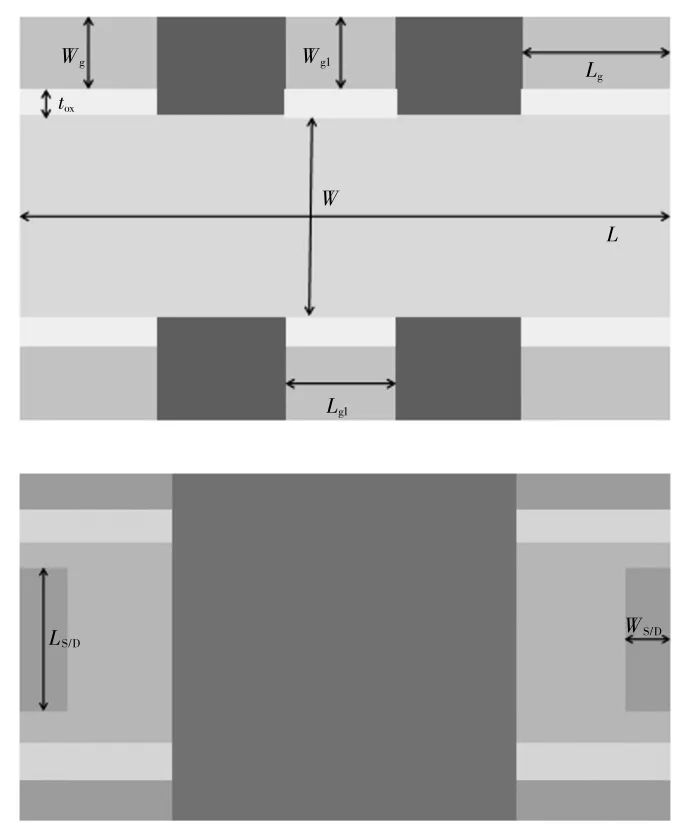

所设计的高肖特基势垒的高性能隧穿场效应晶体管的结构如图1 所示。这是一种具有等号形主控制栅的中央辅助栅场效应晶体管结构,它除了具备源极和漏极之外,还具有两侧等号形主控制栅极和中央辅助控制栅极。图中,W是沟道宽度;L是沟道长度;Wg是两侧主控制栅极宽度;Wg1是中央辅助栅极宽度;Lg是两侧主控制栅极长度;Lg1是中央辅助栅极长度;LS、LD是源、漏电极长度;WS、WD是源、漏电极宽度;tOX是栅氧化层厚度。各参数的具体数值如表1 所示。

图1 器件结构示意图及参数标注

表1 参数数值

3.2 仿真结果

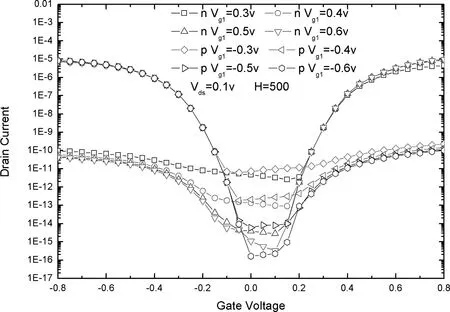

经过仿真,得到具有等号型主控制栅极的中央辅助栅场效应晶体管的以中央辅助栅极Vg1为参数的Vg1-IDS特性曲线,如图2 所示。实验中漏极为固定电压0.1V 且源极接地。通过仿真曲线可以看出,改变Vg1的电压正、反偏置可以相应地改变器件的类型(N-MOSFET 或P-MOSFET)。不论是对N-MOS FET 或P-MOSFET 操作,中央辅助栅极Vg1对该结构的晶体管都具有开关作用。

图2 Vg1-IDS 特性仿真曲线

由图可见,Vg1>0 时,该器件表现为N 型。中央辅助栅极电压的变化对正向导通电流及反向漏电流影响不大,对器件静态漏电流影响较为明显[7]。随着Vg1的正向增大,静态漏电流逐渐降低。由于静态工作区的栅级电压极小,此时主要电流是载流子的热激发运动所产生的。随着中央辅助栅极电压的增加,其控制区域的能带弯曲程度越来越大,对电子的阻挡更强烈,导致流过中央辅助控制栅极的电子数量减小,电流降低。

同理,Vg1<0 时,该器件表现为P 型。中央辅助栅极电压的变化对正向导通电流及反向漏电流影响不大,对器件静态漏电流影响较为明显。随着Vg1的反向增大,静态漏电流逐渐降低。同样由于静态工作区的栅压较小,其主要电流仍为载流子的热激发运动。随着中央辅助栅极电压的增加,其控制区域的能带弯曲程度越来越大,对空穴的阻挡更强烈,导致流过中央辅助控制栅极的空穴数量减小,电流降低。

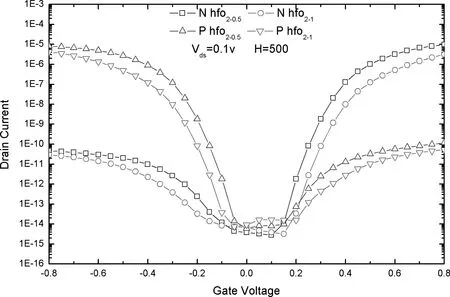

图3 所示为以绝缘氧化层厚度tOX作为可变参数,漏极外加0.1V 固定电压及源极接地、中央辅助控制栅极为固定电压0.5 V 条件下的转移特性曲线。由图可见,绝缘氧化层选取0.5nm 和11nm 两个厚度值。当氧化层厚度为1nm 时,正向导通电流及反向漏电流发生明显降低且正向导通电流降低数值大于反向泄漏电流,反而对静态工作电流没有太大影响。由于绝缘氧化层的厚度增加、栅极电压不变所产生的电场强度降低,导致载流子的带带隧穿能力会随之降低,导致电流减小。

图3 以绝缘氧化层厚度为参数的特性曲线

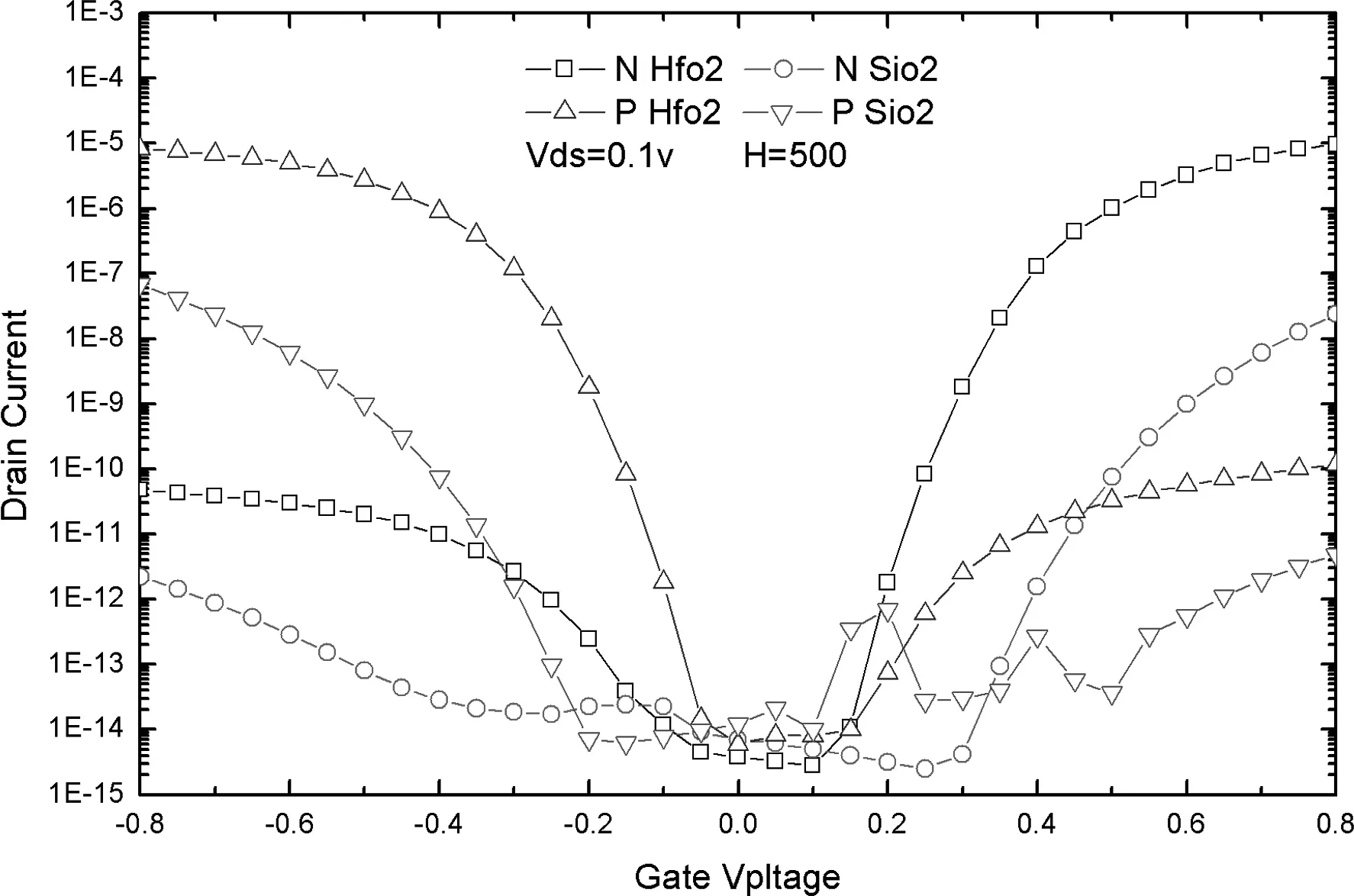

图4 所示为以绝缘氧化层材料厚度作为可变参数,漏极外加0.1V 固定电压及源极接地,中央辅助控制栅极为固定电压0.5V 条件下的转移特性曲线。由图中可见,材料选取二氧化硅和二氧化铪两种。与二氧化铪相比,二氧化硅作为绝缘氧化层材料使正向导通电流及反向漏电流均减小,氧化层材料对静态漏电流并没有太大影响,但二氧化铪的导电性能优于二氧化硅[8]。由于二氧化铪是高介电常数材料,禁带宽度较大,不仅可增强栅极对沟道中载流子的控制能力,还可降低载流子的热激发效应,造成正向导通电流和反向漏电流同时增大的结果。

图4 以绝缘氧化层材料为参数的特性曲线

4 结 束 语

提出的一种基于肖特基势垒的隧穿场效应晶体管,通过结合TFET 和MOSFET 的不同优点,对器件的各方面进行数值优化以达到最佳特性。等号形主控制栅的中央辅助控制栅场效应晶体管器件不仅结构对称还通过结构的U 型沟道克服了短沟道效应,还提高了导通电流,降低了亚阈值摆幅数值和静态功耗,具有很好的发展前景。