基于FPGA 的多端口网络协议解析加速卡硬件电路设计*

卞中昊,田 野,司 艺,朱 超

(1.公安部第三研究所,上海 200031;2.中国信息通信科技集团有限公司,湖北 武汉 430074;3.上海信管网络科技有限公司,上海 200032;4.上海飞宽通信技术有限公司,上海 200240)

0 引言

网络已经成为现代生活中,社会活动和经济发展的重要组成部分。从海量网络数据的接入、解析、处理到智能分析的大数据处理都是网络空间管理核心的基础工作。十九大报告中提出了“建设网络强国”的概念。然而,没有对网络数据的大数据处理,“网络主权”和“网络强国”就无从谈起。因此,构建高效的网络空间数据接入、数据解析、数据处理和智能应用系统,对于掌握网络空间态势、维护网络安全和网络主权、打击网络犯罪、维护线上线下安全都具有重要的意义[1-3]。

随着高速光通信系统、5G 技术、窄带物联网(Narrow Band Internet of Things,NB-IoT)、互 联网协议第6 版(Internet Protocol version 6,IPv6)等技术的同步发展和普及,网络传输带宽 成指数式增长。按照2017 年以太网路线图,未来几年的以太网速率将从10~40 Gb/s 扩展到100 Gb/s、400 Gb/s 甚至1 Tb/s,因此传统的网络空间监管手段面临巨大挑战[2-4]。

目前网络监控系统在数据接入上,多采用分级、分区域化管理和通用处理器方案,来实现网络数据的汇聚、分流、检测和还原工作;在数据解析上,采用内容解析,通过大量人力投入,针对每一个应用系统寻找破解方案,并保存能够识别的内容,抛弃不能识别的内容;在智能算法上,基于能够收集到的内容数据建立算法模型,所以具有“只见树木不见森林”的局限性。

现场可编程门阵列(Field Programmable Gate Array,FPGA)的可再编程技术可以满足不断变化的市场需求。网络加速卡可以通过FPGA 编程,实现不能的功能,应用到不同的领域:在传统加速领 域,可以预处理数据,提供高效的压缩、解压缩算法和视频编码、解码等[3];在网络安全领域,可以进行加密、解密;在其他领域也可以进行大数据分析、文本搜索和分析、机器学习、算法验证。为了加速网络数据处理,亚马逊和微软等公司已经把FPGA 的加速方案应用到他们的数据中心。据Semico Research 于2019 年5 月的预测,从2018 年到2023 年的5 年间,数据中心加速器市场规模预计将从28.4 亿美元增长211.9 亿美元,年均增长率为49.47&[1]。

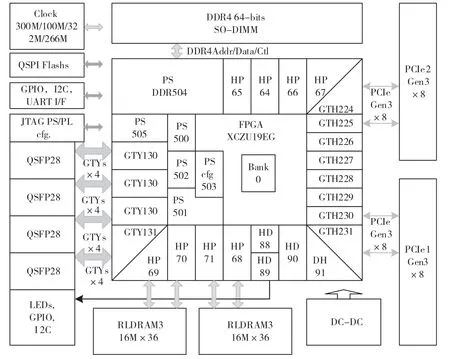

基于上述需求,本文设计一款基于FPGA 的多端口网络协议解析加速卡FBC-810x。4 个QSFP28接口的模块可提供4×40 G、4×100 G 的以太接口,其功能结构如图1 所示。该模块与主板的接口采用PCIe 3.0×16 或2 个PCIe 3.0×8,共计128 Gb/s 的线速接口速率。接口速率出入比不小于0.32。

图1 网络加速卡方案功能

此外,该板卡还包含了电源变换模块、时钟模块、DDR4 和低延迟DRAM 存储模块。板卡使用独立的参考时钟,能够发挥出芯片的最佳性能。电源方面,充分考虑旁路、去耦电容,以滤除各种干扰信号的影响,优化设计,保证系统稳定工作。设计过程中对于高速信号完整性、过孔扇出、过层所造成的阻抗突变、绕线造成的信号串扰、长走线造成的信号衰减等问题均需要进行合理的信号完整性设计。为了实现高速信号在动态随机存储器(Dynamic Random Access Memory,PCB)板上的传输,本研究在设计过程中对传输线损耗、阻抗、差分等长线等信号完整性问题进行了理论和仿真分析。

1 基于FPGA 的协议解析加速卡方案设计

本设计采用的器件是Xilinx 公司的Zynq UltraScale+MPSOC EG 系列器件。虽然部分Virtex UltraScale、Kintex UltraScale+和Virtex UltraScale+的高速串行收发器速率可达30.5 Gb/s,但上述器件存在片内Serdes 数量不够多,缺乏100 G 以太MAC 支持等缺点,且片内没有多核处理器。因此综合考虑功耗、功能、性能以及成本,本研究选用的FPGA 具体型号为XCZU19EG。

XCZU19EG 的内部分成可编程系统(Program-mable System,PS)和可编程逻辑(Programmable Logic,PL)两部分资源。PS 和PL 部分的资源可以通过12 组32 b、64 b 或128 b 的高级总线协议(Advanced eXtensible Interface,AXI)互联总线连接,可实现PS 的某些功能映射在PL 部分的外部管脚上。

PS 部分具有4 个主频1.5 GHz 的ARM Cortex-A53 处理器和2 个主频600 MHz 的ARM Cortex-R5 实时处理器,此外还有主频667 MHz 的Mali-400 图像处理器。上述3 种处理器分别配有L1 缓存32 kB,L2 缓存64 kB~1 MB 和128~256 kB的片上存储。PS 部分的外围接口包括x64 的DDR4 接口、2×Quard SPI NAND 存储器接口,高速互联接口可以是PCIe Gen2 ×4、4 个三模千兆以太控制器、2× USB3.0、SATA3.1、DisplayPort中的组合。通用互联接口可以是2× USB2.0、2× SD/SDIO、2× CAN2.0B、2× I2C、2× SPI、4× 32 位通用输入输出接口(General-Purpose Input/Output,GPIO)中的组合。此外,PS 部分还保护加密、电源管理和系统状态监视功能。

PL部分具有1 143 K的系统逻辑单元块、1 045 K 的触发器和523 K的查找表。在存储器方面具有9.8 MB 的分布式RAM、34.6 MB 的块RAM 和36.0 MB 的超级RAM。时钟管理单元的数量为11 个。另外,PL 部分内部集成了PCIe Gen3 ×16 或Gen4 ×8 IP核、带RS-FEC 编码的100 G 以太MAC/PCS IP 核。C1760 封装的ZU19EG 芯片在PL 部分的高速接口包含32 个16.3 Gb/s 的GTH 接口和16 个32.75 Gb/s 的GTY 接口,这些数量的高速SerDes 接口足以满足本系统的接口数量要求。

根据设计要求,本方案将XCZU19EG 芯片的4个GTY Bank 用于4 个100 G QSFP28 接口;将4 个GTH Bank 用于2 套PCIe 3.0×8 接口。XCZU19EG 芯片提供了高性能接口(High Performance,HP)、高密度接口(High Density,HD)等接口,可满足不同功能的需求。将HP 68-71 Bank 连接RLDRAM3的数据、地址和控制总线;将PS DDR504 Bank 连至DDR4 SODIMM 的地址线、数据线以及控制线;将HD 88-89 bank 作为GPIO口用于驱动LED 以及与光模块进行I2C 通信。PS 部分的PS 500 MIO用于2 片1 Gb QSPI 接口的NOR FLASH 互连;PS 501、502 和503 MIO 分别用于TF 卡、I2C、通用异 步收发传输器(Universal Asynchronous Receiver/Transmitter,UART)和以太千兆位媒质无关接口(Reduced Gigabit Media Independent Interface,RGMII)通信接口及芯片的配置、启动选择控制。FPGA 除了以上的外设外,还需要供电和时钟电路。

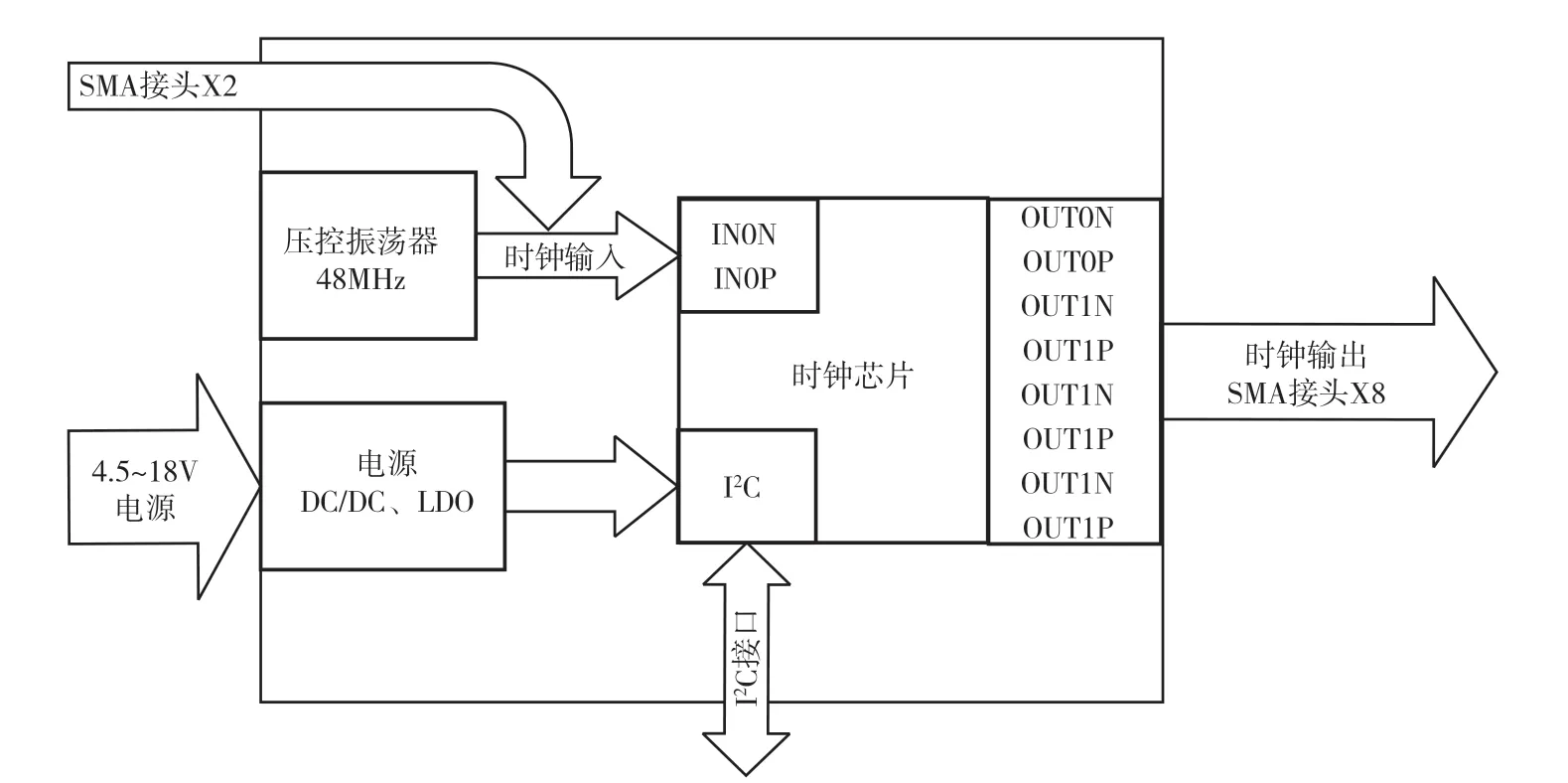

1.1 板卡时钟方案

为了灵活地为多个芯片提供时钟,设计中为时钟模块单独设计了单板。其硬件框图如图2 所示。

图2 时钟模块硬件

时钟模块由时钟芯片、压控振荡器和电源组成,外部接口主要有外部时钟接口、电源接口、I2C 接口和时钟输出接口。因此,模块主要分为四部分时钟信号:FPGA PS 时钟、FPGA PL 时钟、多千兆位收发机(Multi-Gigabit Transceiver,MGT)时钟和双倍速率(Double Data Rate,DDR)时钟。时钟发生器采用两片Silicon Labs 公司的Si5340 超低抖动任意频率多种输出驱动可配置的时钟芯片。每个芯片均采用独立的低抖动48 MHz 有源振荡器作为高频时钟信号的基准。4 个独立稳定的时钟输出频率及驱动配置可通过相关的配置软件快速灵活地设计出,通过I2C 总线可将配置参数输入芯片。

(1)FPGA PS 部分时钟:为整个FPGA 芯片的PS 部分提供一个主频时钟信号,用于芯片上电复位后的电源管理单元的工作、系统配置程序的加载、系统工作时钟的锁相环输入参考、ARM 系统看门狗定时器和CPU 调试等PS 中的功能单元。通常采用固定频率的有源振荡器。本设计采用了一款50 MHz 的均方抖动误差小于2 ps,频率稳定性在 ±10-5范围内,LVCMOS 输出驱动的有源振荡器。

(2)FPGA PL 部分时钟:为整个FPGA 芯片的PL 部分提供一个主频时钟信号,用于芯片运行逻辑程序、PL 部分的外部存储器、控制GPIO 信号、I2C等外围总线提供一个主频参考信号。通常采用固定频率的有源振荡器。该设计采用了一款300 MHz 的均方抖动误差小于1 ps、频率稳定性在±10-5范围内、LVDS 输出驱动的有源振荡器。

(3)MGT 时钟:专为FPGA 高速收发器提供的时钟参考信号。此处的时钟信号分别为QSFP28 以及PCIe 两部分功能提供参考时钟信号。对于ZYNQ UltraScale+FPGA而言,接口速率从16.375 Gb/s 到28.21 Gb/s 的SerDes Quad 单元可以从其上方或下方的一个Quad 单元获得参考时钟,此时可以灵活地分配共享参考时钟给这些Quad 中的SerDes 使用。该设计使用外部时钟发生器为每个GTY Bank提供了独立的参考时钟。

(4)DDR 时钟:通过时钟芯片Si5340 先提供给FPGA PS 部分DDR 控制器单元,再由FPGA 统一为DDR 芯片提供时钟,并进行数据、地址等信号的交互,从而可以更好地减少时序问题。

1.2 板卡电源方案

板卡有两个供电通道:其一使用外部12 V 电源适配器,通过4PIN 接口插入供电;其二,使用PCIe 接口中的12 V 电源进行供电。供电设计采用了一个双电源均流控制器,集成了金氧半场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)二极管,具有共享负载能力。此芯片不需要共享总线或电源上的微调引脚,即可实现外部12 V 电源或PCIe 接口中的12 V 电源的二选一供电,也可实现同时供电,这在PCIe 接口供电功率不足时是十分必要的。在启动和故障情况下,双电源均流控制器内的理想二极管会阻止反向电流和直通电流,可最大程度地减小反向电流瞬变对供电系统的损伤。在同时供电时,它会自动调整两个正向电压差以共享电源之间的负载电流。

电源芯片均采用的是MPS(Monolithic Power Systems)、ADI(Analog Devices Inc)、Micro Chip三家公司的电源芯片。整个电源设计为FPGA 各功能单元提供了足够的电源功率,并且根据FPGA 上电顺序要求,设计了合理的上电顺序。

参照Xilinx 关于UltraScale+在各种片内资源使用率情况下的电源功耗估计结果,选择了上述供电芯片或模块。在FPGA 应用实例中,一般内核电源VCCINT 所需功率最大,其次是高速光模块以及DDR 电源。万兆收发器SerDes 的电源供电对于恢复接收信号的时钟抖动至关重要,因此只要涉及万兆收发器,即使系统中已有相同电压值的电源,也必须分别独立供电。

根据Xilinx FPGA 用户手册建议,推荐的上电顺序为VCCINT、VMGTAVCC、VMGTAVTT 或VMGTAVCC、VCCINT、VMGTAVTT,没有建议对VMGTVCCAUX进行排序,所以VMGTAVCC 和VCCINT 均可同时加载。利用前一个电源的检测(Power Good,PG)信号作为下个电源的EN 使能信号,可方便地控制上电顺序。上电顺序在电源树中体现在电源芯片先后出现的次序上。

2 高速信号完整性仿真与测试

当高速信号沿着传输线传输时,由于传输线损耗,高频分量的幅度会减小而低频分量的幅度不变。由于这种频率选择性衰减,传输线的带宽降低,导致传输信号的带宽降低,信号上升沿变缓[5-7]。这种频率相关性损耗造成的信号上升沿退化会引起码间干扰(Inter Symbol Interference,ISI)、抖动等信号完整性问题。另外,传输过程中的信号反射也将造成传输信号能量的损失,信号上下沿出现过冲、振铃等问题[6-9]。

使用Ansys HFSS 3D 布线建模仿真软件对高速信号线进行仿真,通过仿真可以得到高速传输线的S参数和时域反射(Time Domain Reflectometry,TDR)参数,可在PCB 制板前判断其是否达到设计的预期效果。

由于光模块连接器的顶层空间有限,需要使用过孔换层。普通PCB 的过孔大致有通孔、盲孔、埋孔3 种类型,其中通孔的制作工艺相对简单,而且夹具板的高速走线密度不大,无需使用盲孔、埋孔技术。当使用通孔将表层信号换层到内层时,通孔的下半部分会留出一个残桩,残桩会导致信号在残桩末尾处发生反射使得传输线的插入损耗曲线出现谐振,残桩越长谐振频率点越低。谐振点的存在使相邻频段的插入损耗增加,从而加剧频率点处信号的衰减。对于谐振点问题,设计中可以使用背钻(Back-drilling)技术,即通过机械钻孔的方式将过孔未使用部分的镀层除去。这种设计会增加布线设计难度,且会增加成本,因此设计中将顶层传输线直接换层到底层,使得传输路径中不出现过孔残桩。

通孔产生的寄生电容大小为:

式中,εγ为相对介电常数,T为通孔的长度,D1是焊盘(pad)的直径,D2为反焊盘(antipad)直径。

由式(1)可知,降低通孔寄生电容的方法有改变介质的介电常数、PCB 厚度、通孔焊盘直径和通孔反焊盘直径。通常来说,在设计之初叠层结构和介质材料已经确定,只能通过焊盘直径和反焊盘直径调整寄生电容。

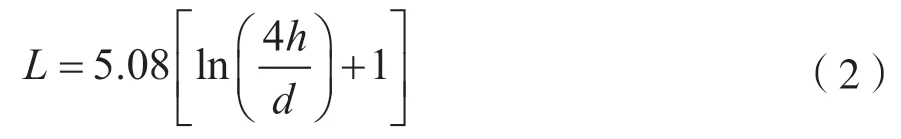

产生的寄生电感为:

式中,h是过孔的长度,d是过孔的直径。

由式(2)可知,过孔的寄生电感值与通孔长度和通孔直径有关,而通孔长度在PCB 厚度确认后无法改变,所以只能调整通孔直径。通常来说,过孔处的阻抗偏小,可以通过减小通孔直径增加寄生电感,将阻抗调整至特性阻抗。但由于工艺有限,通孔直径无法做到很小,且与板厚有关,PCB 越厚可制造性越小。因此,调节通孔阻抗的一般方法是直接调整通孔的寄生电容。

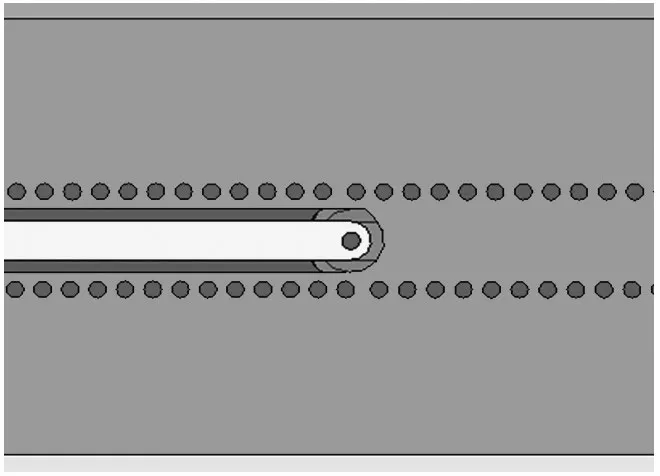

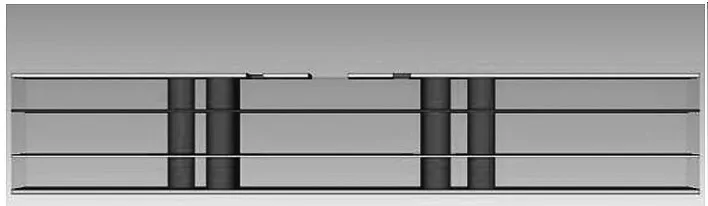

光模块夹具板的换层过孔不同于微带线双层板过孔,它是将顶层接地共面波导换层至底层的通孔,通孔穿过两层平面后到达底层。由于其结构与一般过孔不同,且无法估算具体阻抗值,所以使用CST对过孔阻抗做了仿真。仿真过程中将cadence 设计的换层设计转换成ODB++格式后导入CST 微波工作室,其三维结构的俯视图和切面图如图3 和图4所示。

图3 过孔俯视图

图4 过孔刨面

由图3 和图4 可以看出,设计中去除了穿过两层导体时过孔壁上无电气连接的非功能焊盘。非功能焊盘与平面反焊盘间的寄生电容使得容性负载变大,从而减小过孔部分的阻抗。

由于焊盘连接着传输线,焊盘直径无法调整。因此只能通过改变第二层和第三层导体的过孔反焊盘直径改变过孔阻抗。将离散端口1 设置在顶层接地共面波导处,离散端口2 设置在底层共面波导处,反焊盘半径可变。仿真过程中使用了参数扫描方法,将反焊盘半径从0.2 mm 扫描到0.5 mm,每组增加0.06 mm,共计6 组仿真数据。在仿真设置中打开TDR 分析,得出如图5 所示过孔阻抗参数扫描结果。

图5 过孔阻抗参数扫描结果

在图中放置了Marker,用于观察过孔换层时的阻抗情况。当过孔反焊盘半径为0.2 mm 时,过孔处阻抗下降至43.7 Ω。阻抗下降的原因是反焊盘较小使寄生电容增大,比约49.5 Ω 的传输线阻抗低了6 Ω,所以在此处信号将发生较大的负反射,将过孔反焊盘的半径增加会使其换层处阻抗变大。当反焊盘半径增加至0.5 mm 时,过孔处阻抗值变为51.5 Ω,超过了传输线特性阻抗,在过孔处信号发生正反射。所以选择反焊盘半径为0.38 mm 的过孔作为高速信号换层过孔,此时过孔处阻抗约为 49.6 Ω,传输线上的阻抗突变点基本消除,反射损耗最小。

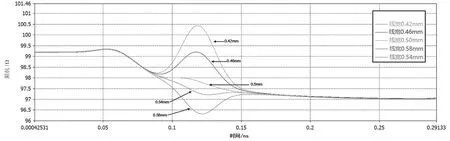

为了探究阻抗优化对传输线插入损耗的影响,使用CST 仿真出过孔换层传输线的插入损耗。仿真过程中扫描了反焊盘半径的几个参数,扫描结果如图6 所示。

图6 过孔插入损耗扫描结果

由上图扫描出的结果可知,在5 GHz 频段内,过孔阻抗对插入损耗几乎没有影响,但超过5 GHz时,频率升高则阻抗对插入损耗的恶化作用越明显。从27 GHz 处的Maker 可以看出,反焊盘半径为0.2 mm 的插入损耗比半径为0.38 mm 时大了0.37 dB,几乎是半径为0.38 mm 时损耗值的1 倍多。由仿真结果可知,当Layout 过程中出现高速信号过孔换层时,应对过孔进行阻抗优化,优化过后对传输线的插入损耗有很大的改善。

差分互连可以极大地改善信号传输质量,所以几乎所有的高速总线都会使用差分对。差分互连是指信号驱动端同时产生双路信号,它们沿着不同的传输线传输且极性相反,并在接收端进行差分检测提取发送的信息。差分线上的信号噪声在接收端的差分检测处相互抵消,只要收到的干扰噪声大小相同则不会对差分信号传输造成影响。差分信号按照工作模式可划分为共模与差模信号。共模信号所感知的阻抗为共模阻抗,差模信号感知的阻抗是差分阻抗。

通常来说,差分对设计要使两条传输线等长,从而保证接收端信号边沿处于同一时间点。当Layout 过程中差分对出现不等长现象时,可通过蛇形线的方式调整长度,在信号发生检测模块中就使用了这样的调控方式。但蛇形线会导致这一段的差分阻抗小于差分特性阻抗100 Ω,所以需要优化蛇形线处的阻抗。

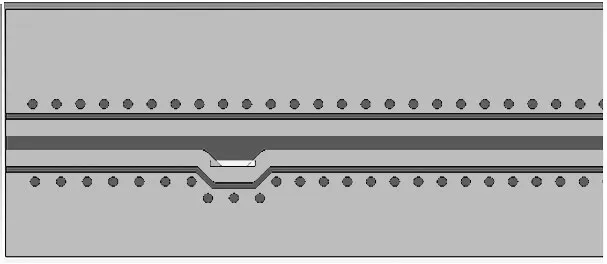

与上述仿真流程相同,将信号发生检测模块导入CST,裁剪出需要仿真的蛇形线。蛇形线三维结构的侧视图和俯视图如图7 和图8 所示。

图7 蛇形线的侧视图

图8 蛇形线的俯视图

由俯视图可以看出,蛇形线会导致两条传输线耦合变弱,从而使得差分阻抗增大。仿真过程中使用改变蛇形线宽度的方式调控差分阻抗。与过孔阻抗优化方式相似,对蛇形线线宽进行了参数扫描后得出TDR 分析曲线。蛇形线阻抗参数扫描结果 如图9 所示。

图9 蛇形线阻抗参数扫描结果

可见,蛇形线的初始宽度与传输线相同,为 0.42 mm,此时蛇形线处差分阻抗比传输线原本的差分阻抗大3 Ω。将蛇形线宽度逐次递增至0.58 mm,每次增加0.04 mm,共有5 组扫描结果。

由扫描结果可以看出,在蛇形线宽为0.54 mm时,其差分阻抗与传输线基本相同,而宽度增大至0.58 mm 时会使其阻抗小于传输线。参数优化过程中,模型会沿用其他参数的网格划分方式,所以结果比对会相对准确,从而为传输线阻抗设计提供准确参考。通过仿真结果可以看出,本文设计可以满足SFF-8432 协议规范的传输损耗要求。

3 结语

本文设计了一款基于FPGA 的PCIe Gen3 接口硬件板卡FBC-810x,用于服务器以及数据中心的网络协议解析加速。提供了完整的加速卡时钟硬件设计方案以及加速卡电源设计方案。该设计采用了背钻技术,同时对传输线进行了仿真,优化调整了由BGA 扇出的传输路径、过孔参数以及背钻参数,验证了本文设计的高频板性能达标。