TFT-LCD过孔接触电阻研究

白金超,王玉堂,郭总杰,丁向前,袁剑峰,邵喜斌

(北京京东方显示技术有限公司,北京 100176)

1 引 言

薄膜晶体管液晶显示器已成为目前平板显示的主流产品,为了提高其品质,相关研究进行了很多[1-3]。其中纯铝材料是近年来研究的重点,以其低电阻率、低成本、易刻蚀等优势,逐渐成为薄膜晶体管配线的主要材料[4-5]。同时氧化铟锡具有良好的导电性和高的光学透过率,作为透明电极被广泛应用在薄膜晶体管液晶显示器上,成为不可或缺的一部分[6-8]。纯铝和氧化铟锡经常同时应用在薄膜晶体管制造中,二者通常需要通过过孔连接,而过孔的接触电阻大小严重影响产品的显示品质和长期可靠性[9]。因此,在产品设计开发中,如何降低过孔接触电阻是提高产品品质的重要课题。

本文运用开尔文四线检测法对不同大小、形状、数量的纯铝与氧化铟锡连接过孔的接触电阻进行测量,并对接触电阻变化规律进行全面的机理分析和讨论,为减小过孔接触电阻、优化过孔设计提供依据。

2 实验方法

本文实验基板是康宁公司Eagle-XG 10K玻璃,尺寸为2 500mm×2 200mm,厚度0.5mm。采用4mask工艺,在基板上依次形成栅极金属层、栅极绝缘层、源/漏层(Source/Drain,SD)、薄膜晶体管钝化层和像素电极。物理溅射形成钼/铝/钼(Mo/Al/Mo)15nm/300nm/80nm的栅极和源/漏层金属,以及40nm氧化铟锡的像素电极。等离子加强型化学气相沉积较低介电常数的氮化硅形成栅极绝缘层和薄膜晶体管钝化层,厚度均为400nm。金属层采用湿法刻蚀。通过一次干法刻蚀,在薄膜晶体管钝化层上形成过孔使氧化铟锡和源/漏层金属相连接,在栅极绝缘层和钝化层上形成过孔使氧化铟锡和栅极金属相连接。

使用 ADE-2500DC DRY ETCH 设备进行过孔干法刻蚀。干法刻蚀采用增强电容耦合等离子体模式 (Enhanced Capacitive Coupled Plasma,ECCP)。刻蚀组分由六氟化硫、氧气生成,六氟化硫的流量为0.12~0.24m3/h,氧气的流量为0.18~0.24m3/h,源极射频功率为3 000~8 000 W,偏置射频功率为4 000~9 000W,气压为6.65~13.3Pa,设备下部电极、反应腔壁和顶部温度为30℃。过孔干法刻蚀时进行20%~40%的过刻,以免过孔中氮化硅残留,保证氧化铟锡和栅极、源/漏层金属完全连接。

本文采用半导体参数测试设备对基板上具有开尔文结构的过孔接触电阻测试样品进行测试,找出过孔接触电阻变化规律。然后通过扫描电子显微镜、能量色散X射线光谱仪和聚焦离子束显微镜等方法对过孔内部形貌进行表征,以对过孔接触电阻变化规律进行机理分析。过孔的测试条件如表1。其中过孔关键尺寸(Final inspection critical dimension,FICD)为刻蚀后过孔尺寸。

表1 过孔测试条件Tab.1 Via hole test split

3 结果与讨论

3.1 过孔大小对接触电阻的影响

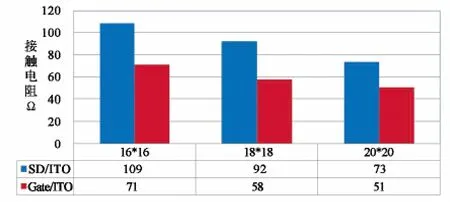

由图1可知,相同大小的过孔,源/漏层金属和氧化铟锡的过孔接触电阻大于栅极金属和氧化铟锡的过孔接触电阻。不同大小的过孔,随着过孔尺寸的增大,源/漏层金属和氧化铟锡的过孔接触电阻以及栅极金属和氧化铟锡的过孔接触电阻逐渐减小。

图1 不同大小过孔的接触电阻测试结果Fig.1 Contact resistance of different size via hole

3.2 过孔形状对接触电阻的影响

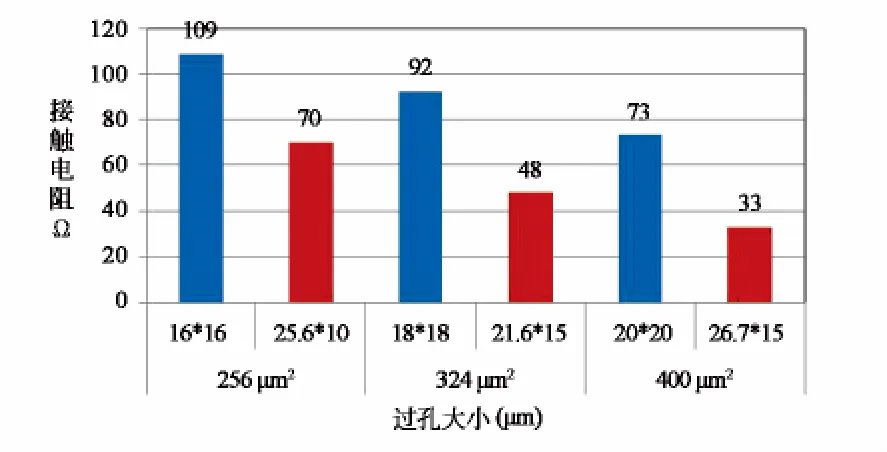

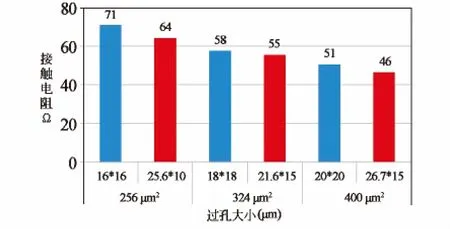

由图2、3可知,相同的过孔面积下,长方形过孔的源/漏层金属和氧化铟锡接触电阻、栅极金属和氧化铟锡接触电阻都小于正方形过孔的接触电阻。

图2 不同形状过孔的源/漏层金属和氧化铟锡接触电阻测试结果Fig.2 Contact resistance of SD and ITO with different shape via hole

图3 不同形状过孔的栅极金属和氧化铟锡接触电阻测试结果Fig.3 Contact resistance of Gate and ITO with different shape via hole

3.3 过孔数量对接触电阻的影响

图4 不同数量过孔的源/漏层金属和氧化铟锡接触电阻测试结果Fig.4 Contact resistance of SD and ITO with different number via hole

图5 不同数量过孔的栅极金属和氧化铟锡接触电阻测试结果Fig.5 Contact resistance of Gate and ITO with different number via hole

由图4、5可知,一个16μm×16μm正方形过孔的接触电阻要大于4个8μm×8μm过孔的接触电阻,18μm×18μm和20μm×20μm的过孔也存在这样的趋势。所以在相同的过孔面积下,单正方形过孔的源/漏层金属和氧化铟锡接触电阻、栅极金属和氧化铟锡的接触电阻要大于多小正方形过孔的接触电阻。

3.4 过孔形貌测试

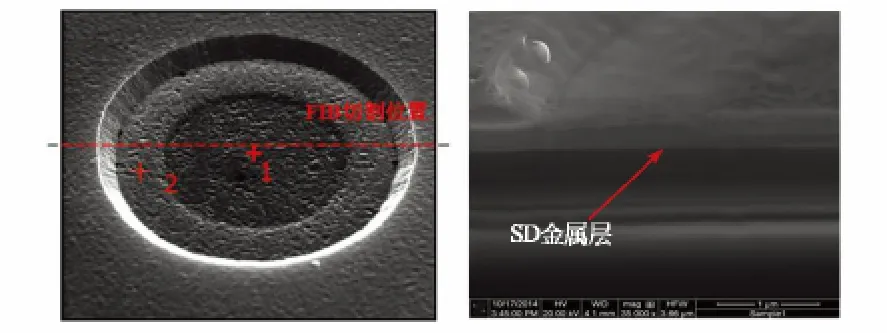

图6为源/漏层金属和氧化铟锡相连接过孔的扫描电子显微镜俯视图和聚焦离子束显微镜截面图。结果显示,在过孔内部源/漏层金属厚度由孔边缘到孔中心逐渐减薄,由于孔边缘和孔中心的厚度差,在过孔周围形成具有一定宽度的圆环。对过孔中心位置1和过孔周边的圆环位置2进行能量色散X射线光谱仪成分分析,如图7。过孔中心位置的钼和铝的重量百分比的比值为0.25,远小于过孔周边圆环处的钼和铝的重量百分比的比值1.55。根据以上结果可以推断,钼/铝/钼15 nm/300nm/80nm结构的源/漏层金属在过孔内部周边位置的顶层钼厚度远远大于过孔中心位置的顶层钼,过孔刻蚀导致过孔中心位置顶层钼绝大部分被刻蚀掉,甚至裸漏出下层的铝。

图6 源/漏层金属和氧化铟锡连接过孔的扫描电子显微镜图(左)和聚焦离子束显微镜图(右)Fig.6 SEM picture of SD and ITO connection via hole(left)and FIB picture(right)

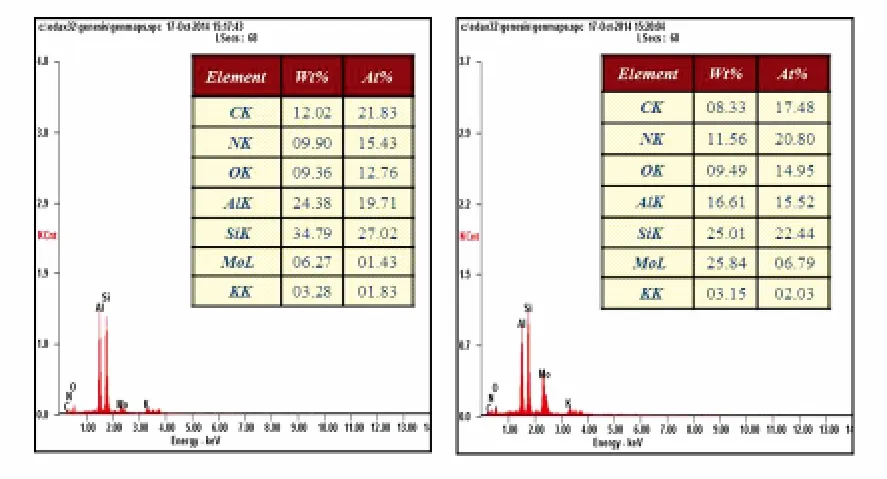

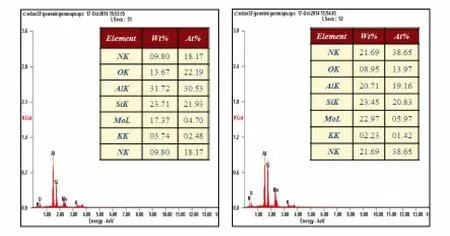

图7 源/漏层金属和氧化铟锡连接过孔的孔中心位置(左)和孔边缘位置(右)EDS测试结果Fig.7 EDS result of SD and ITO connection via hole center(left)and edge(right)

图8为栅极金属和氧化铟锡连接过孔的扫描电子显微镜俯视图和聚焦离子束显微镜截面图。结果显示,在过孔内部栅极金属厚度由孔边缘到孔中心没有显著变化。对过孔中心位置3和过孔周边位置4进行能量色散X射线光谱仪成分分析,如图9所示,过孔中心位置的钼和铝的重量百分比的比值为0.55,小于过孔周边位置的钼和铝的重量百分比的比值1.11。由此可以推断,钼/铝/钼15nm/300nm/80nm结构的栅极金属在过孔的中心和周边都存在顶层钼,但是过孔周边位置的顶层钼厚度大于过孔中心位置的顶层钼。

图8 栅极金属与氧化铟锡连接过孔的扫描电子显微镜图(左)和聚焦离子束显微镜图(右)Fig.8 SEM picture of Gate and ITO connection via hole(left)and FIB picture(right)

3.5 机理分析

过孔刻蚀时会进行20%~40%过刻,以保证过孔内无氮化硅残留,过刻会导致过孔内顶层钼被刻蚀。同时,由于源/漏层金属和氧化铟锡之间的绝缘层为400nm的氮化硅钝化层,栅极金属和氧化铟锡之间的栅极绝缘层和氮化硅钝化层总厚度为800nm,在相同的刻蚀时间,源/漏层金属和氧化铟锡相连接的过孔内顶层钼暴露在干刻等离子体的时间更长,被等离子体刻蚀的更多,所以源/漏层金属和氧化铟锡相连接的过孔内的顶层钼损失比栅极金属和氧化铟锡相连接的过孔内顶层钼损失更严重,过孔内残留顶层钼厚度更薄,面积更小。

图9 栅极金属与氧化铟锡连接过孔的孔中心位置(左)和孔边缘位置(右)EDS测试结果Fig.9 EDS result of Gate and ITO connection via hole center(left)and edge(right)

同时,由于铝和氧化铟锡的电学接触性能不好,接触电阻较大,而钼和氧化铟锡有较好的电学接触性能,接触电阻远小于铝和氧化铟锡的接触电阻。因此顶层钼的厚度越厚,面积越大,过孔的接触电阻越小。故过孔面积相等时,源/漏层金属和氧化铟锡的过孔接触电阻要大于栅极金属和氧化铟锡的过孔接触电阻。

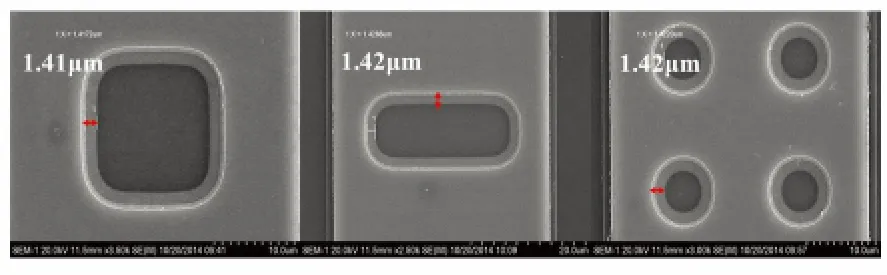

图10 各种源/漏层金属和氧化铟锡连接过孔的扫描电子显微镜结果Fig.10 SEM picture of SD and ITO connection via hole

由过孔形貌测试结果可知,源/漏层金属和氧化铟锡相连接的过孔中心位置顶层钼绝大部分被刻蚀掉,甚至裸漏出铝,在过孔内部周边位置残留的顶层钼形成一定宽度的圆环。图10为源/漏层金属和氧化铟锡相连接的各种过孔扫描电子显微镜俯视图,结果显示,正方形单大孔、长方形单大孔和正方形多小孔内残留的顶层钼形成的圆环宽度基本一样,约1.4μm,所以过孔周边残留的顶层钼圆环周长越大,钼的面积就越大,接触电阻就越小。栅极金属和氧化铟锡相连接的过孔中心和周边都存在顶层钼,但是过孔中心的顶层钼比周边顶层钼的更薄。由于周边顶层钼较厚,所以周边顶层钼的周长越长,钼的面积就越大,接触电阻越小。

因此,对于同一形状的过孔,过孔面积越大,孔周长就越大,过孔接触电阻越小;在过孔面积相等时,过孔数量越多,过孔周长就越大,过孔接触电阻就越小,即多小孔接触电阻小于单大过孔。同时,在过孔面积相等时,长方形过孔周长大于正方形过孔,所以长方形过孔接触电阻小于正方形过孔。

4 结 论

(1)对于钼/铝/钼结构的金属与氧化铟锡连接过孔,过孔面积越大,过孔接触电阻越小;在过孔面积相同下,长方形过孔接触电阻小于正方形过孔,多小孔接触电阻小于单大过孔,栅极金属与氧化铟锡的过孔接触电阻小于源/漏层金属与氧化铟锡的过孔接触电阻。

(2)在产品设计时,为了降低钼/铝/钼与氧化铟锡连接过孔的接触电阻,过孔面积尽可能最大化,采用长方形过孔优于正方形过孔,多小过孔优于单大孔设计。

(3)在产品制备时,为了降低钼/铝/钼与氧化铟锡连接过孔的接触电阻,需要不断优化过孔刻蚀工艺,提高刻蚀选择比,减少顶层钼的刻蚀损失。

[1] 闫方亮,沈世妃,侯智,等.a-Si厚度对 TFT开关特性的影响[J].现代显示,2011,12(7):23-25.Yan F L,Shen S F,Hou Z,et al.Effect of a-Silicon thickness on TFT characteristic[J].Advanced Display,2011,12(7):23-25.(in Chinese)

[2] Muhammad M H,Nairn M,Zhan Z B.Metal wet etch issues and effects in dual metal gate stack integration[J].Journal of the Electrochemical Society,2006,153(5):43-46.

[3] 张定涛,李文彬,姚立红,等.大尺寸 TFT-LCD ECCP刻蚀工艺低耗整合[J].液晶与显示,2014,29(1):6-13.Zhang D T,Li W B,Yao L H,et al.Low consumption combination of large-sized TFT-LCD ECCP etch process[J].Chinese Journal of Liquid Crystals and Displays,2014,29(1):7-14.(in Chinese)

[4] Kwang-ho J,Soo-jung H,Young-chang J.Effect of capping layer on hillock formation in thin Al films[J].Metals and Materials International,2008,14(2):147-150.

[5] 刘翔,陈旭,谢振宇,等.使用低电阻金属铝制造薄膜晶体管阵列信号电极[J].液晶与显示,2009,24(4):533-536.Liu X,Chen X,Xie Z Y,et al.Low resistant metal for thin film transistors[J].Chinese Journal of Liquid Crystals and Displays,2009,24(4):533 536.(in Chinese)

[6] Gruner G.Carbon nanotube films for transparent and plastic electronics[J].J Mater Chem,2006,16:3533-3539.

[7] 刘翔,薛建设,周伟峰,等.改善沉积氮化硅薄膜对FFS-TFT透明电极ITO影响的研究[J].真空科学与技术学报,2012,32(1):36-38.Liu X,Xue J S,Zhou W F,et al.Study on the effect of improving the deposition of silicon nitride films on ITO[J].Vacuum Science and Technology,2012,32(1):36-38.(in Chinese)

[8] Lewis B G,Paine D C.Applications and processing of transparent conducting oxides[J].Mrs Bulletin,2000,25(8):22-27.

[9] Seo H S,Choi J B,Yun D C,et al.Simple process of Hillock-free Al-gate metallization without ITO/Al contact problems for large-area TFT-LCDs[J].SID,1998,29:375-378.