倾斜排列差分过孔间串扰抑制方案

张慧超,王亚飞,李学华

(北京信息科技大学 信息与通信工程学院,北京 100101)

0 引言

近年来,随着信息时代的迅速发展,人们对能够支持高速数字信号准确传输[1-3]的印刷电路板(printed circuit board,PCB)的需求越来越高。在面对高频传输的要求时,确保信号能够准确地从一个电子模块的激励端传输到特定的接收端,已成为集成电路设计的关键问题[4]。

差分信号因其抗干扰性强且稳定性高,被广泛应用于多层板的信号传输[5]。然而,在研究多层板的信号完整性时,发现信号在层间传输时所遇到的串扰问题大多是由差分过孔引起的,这是因为过孔具有较大的尺寸,会导致阻抗不连续等问题,从而影响信号完整性[6-7]。在高速串行链路中,随着频率的增加,过孔的寄生参数对信号完整性的影响愈发严重。为减小信号间的串扰,需要调整过孔的物理参数,如过孔的直径和长短、反焊盘的直径和形状等,因其直接影响过孔的寄生参数。同时,过孔的短截线也会影响信号的传输性能,是否设置短截线及其长度都会影响信号的衰减[8-10]。对于差分信号,其回流路径的设计同样至关重要,需确保差分信号的驱动路径和返回路径上无电气间断[11]。尽管优化过孔的物理参数对于减小信号之间的串扰有很好的效果,但随着频率要求的提高,仅从这方面进行优化已经不能完全满足传输性能的要求。因此,需要从其他角度出发来改变相邻过孔间的耦合。

本文提出了2种倾斜的差分过孔排列方案,减小多层板上垂直通孔对间的串扰。所提方案对传统的差分过孔排列结构进行了优化,改变了过孔的排列方式。采用基于有限元法的全波仿真软件HFSS对方案进行建模,研究了改变位置参数对于差分过孔间串扰的影响,通过等效电路和磁场耦合方向,定性分析了差分过孔间的串扰,最后仿真了0.1~30 GHz范围内所提方案的串扰抑制效果。

1 差分过孔间的串扰

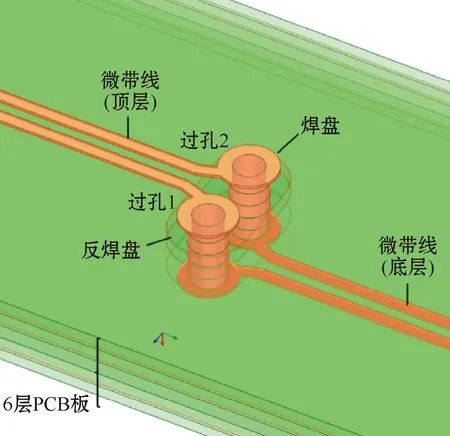

1.1 差分过孔的等效电路模型

在高速电路中,当不同信号层进行通信时,需要利用过孔进行信号传输,如图1所示,过孔1和过孔2为6层PCB板的单对差分过孔。该差分过孔被用于连接不同板层之间的信号,并通过微带线建立信号传输通道,其中焊盘用于连接传输线和过孔,反焊盘则用于隔离过孔和相邻金属层,防止短路。

图1 单对差分过孔排列Fig.1 Single-pair differential via arrangement

为分析差分过孔信号通道间的串扰,采用一阶等效电路模型来建模。单对差分过孔对应的一阶等效电路模型如图2所示。C1、C3为最顶层微带线所连接焊盘与参考地的寄生电容,C2、C4为第6层微带线所连接的焊盘与参考地的寄生电容。由于2个过孔的对称性,所以2个上焊盘电容C1=C3,2个下焊盘电容C2=C4。Cm1为过孔对内部顶端焊盘间的互电容,Cm2为过孔对内部底端焊盘间的互电容,2个互电容也相等,即Cm1=Cm2。2个过孔间的互电容为Cvia,过孔间的互感为Lvia。Lvia1和Lvia2为过孔的寄生电感。

图2 单对差分过孔的等效电路Fig.2 Equivalent circuit of single-pair differential via

2个差分过孔的互电容和互感的计算式[12]如式(1)和式(2)所示。

(1)

(2)

式中:r为过孔的半径;l为过孔的长度;s为2个过孔间的中心距;εr为PCB板的相对介电常数。

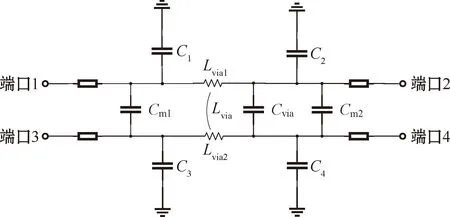

1.2 差分过孔对间的串扰分析

在高速传输中,当存在干扰信号时,过孔间的互电容会导致受害线上产生流向两边的电流。过孔间的互电容Cvia越大,产生的感应电流也越大。同时,信号在传输过程中产生变化的磁场,会在受害线上感应出与之相反的电压。过孔间的互感Lvia越大,感应电压也越大。在差分过孔对间,磁耦合比电耦合的影响更为显著,因为差分过孔对通常由反焊盘进行隔离,并由环绕的接地平面进行屏蔽。相邻的差分过孔对间由于电磁场耦合仍会产生干扰,因此,差分过孔对间的互感Lm成为研究串扰的关键。互感Lm的大小取决于两差分过孔对之间的物理布局和位置关系,两差分过孔对之间最坏情况的互感近似为

(3)

式中:H为PCB板的厚度;R为2个相邻过孔对中心之间的距离。

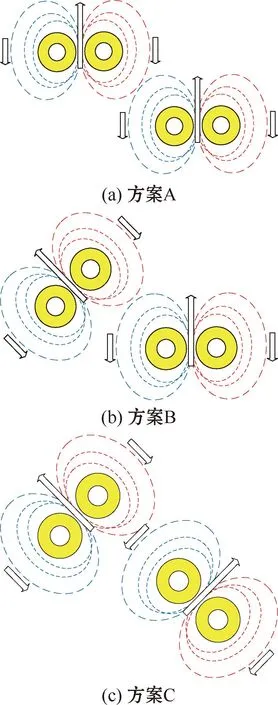

根据式(3)可知,两差分过孔对的互感与过孔对间距R的平方成反比。图3给出了传输差分信号时,过孔周围的磁场分布情况,磁力线的疏密反映了磁场强度,有助于评估串扰程度。图3中,差分过孔对a、b、c、d的排列方式不同,分别与中间的差分过孔对构成不同的布局方式。差分过孔对受到的串扰程度取决于穿过过孔对内的磁力线数量。可以看出,即使过孔对的中心点位于相同的位置,过孔对所受到的差分串扰也会因过孔排列方向的改变而发生变化。对于差分过孔对a,不同的磁力线从2个过孔间穿过,越靠近干扰源,差分过孔对a受到的干扰就越多,导致串扰越严重。而差分过孔对b处的磁场较弱,因为其周围磁力线的数量较少,所以该差分过孔对受到的串扰相对较小。对于差分过孔对c,尽管差分过孔的中心距离与b相比保持不变,但由于排列方向的不同,从c差分对的2个过孔间穿过的磁力线数量较少,这种布局设计减少了穿过差分过孔对c的磁力线的数量,从而降低了串扰。对于差分过孔对d,其轴线与磁力线平行,意味着在其2个过孔间没有不同的磁力线穿透。这样的排列方式使得差分过孔对d之间的串扰效应较小。综上分析,优化差分过孔对的布局和间距是设计高性能电路和系统的关键。

图3 两对差分过孔排列方式俯视图Fig.3 Top view of two pairs of differential via arrangement

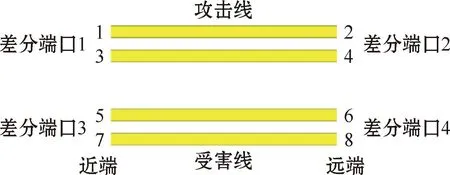

研究两对差分信号的传输特性时,模态分析是至关重要的,混合模式S参数用于研究差分结构的2种支持模式(差模模式和共模模式)以及它们之间的模式转换。如图4所示,将单端信号的8端口网络等效成差分4端口网络,8端口网络的单端端口1和3是差分端口1,单端端口2和4是差分端口2,单端端口5和7是差分端口3,单端端口6和8是差分端口4。

图4 两对差分信号线的端口图Fig.4 Port diagram of two pairs of differential signal lines

在该系统下,定义差分端口1为激励端口时,差分端口4的输出增益Sdd41表示差分远端串扰,差分端口3的输出增益Sdd31表示差分近端串扰。混合模型散射参数矩阵SM由单端散射参数矩阵S计算得出,如式(4)所示。

SM=M·S·M-1

(4)

式中:M为模式转换矩阵,如式(5)所示。

(5)

通过式(4)得到差分远端串扰Sdd41和差分近端串扰Sdd31:

(6)

Sdd31=0.5[S51-S53-(S71-S73)]

(7)

由上述公式可知,当对应的单端口间的耦合水平相近时,计算出的串扰结果就小,理论上存在串扰为零的差分过孔排列方案,即2对差分过孔呈完全正交且对称地排列,此时磁力线与受害差分过孔对的轴线平行。然而在实际应用中,由于2对平行的差分传输线的走线限制,所以,需要提出其他合适的布局方案来减小2个过孔对间的串扰。

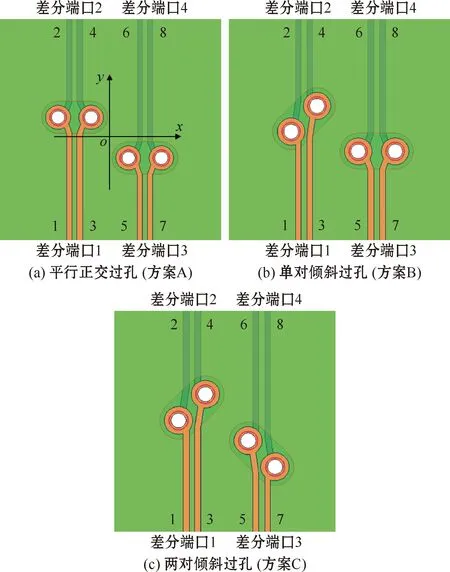

2 倾斜排列的差分过孔方案

根据以上分析,本节提出了通过优化差分过孔对间的几何布局来减小串扰的方案。在高速互连中通常使用平行正交的差分过孔对的布局方式,如图5(a)所示,以方案A代指这种布局方式。但是随着频率增加,该种差分信号对之间的串扰水平显著增加。本文提出的2种倾斜排列的差分过孔结构如图5(b)、(c)所示,分别为单对倾斜过孔方案(方案B)和两对倾斜过孔方案(方案C)。方案B是在方案A的基础上,不改变差分对内通孔间距和2个差分通道的间距,其最左端的差分通孔从x轴负方向到y轴负方向作了45°角的偏移。方案C则是将2对平行的差分过孔都做了与方案B同样的倾斜处理。

图5 三种差分过孔排列方案Fig.5 Three differential via arrangement schemes

通过磁场分布来研究以上3种方案中相邻差分过孔对间的耦合程度。根据右手螺旋定则,当相邻的2组垂直过孔上的电流流经时,产生的磁场方向是一致的,会导致严重的互干扰,感应电压UN如式(8)所示。

(8)

式中:M为互感系数,其大小取决于干扰源和受害电路的环路面积、方向、距离以及两者之间有无电磁屏蔽;is是干扰源回路中的电流。

因此,为了减小串扰,可以通过改变过孔的排列布局来减小互感系数,从而降低差分过孔对之间的磁场耦合。图6为上述3种差分过孔排列方案周围磁场的大致分布,图中方案A由于两对过孔的磁场方向一致,导致了更强的磁场耦合和串扰。图中方案B展示了单对倾斜过孔排列的情况,2个过孔对的磁场方向以45°相交,能够减小磁场的耦合效应和串扰,当信号通过第一对过孔时,它所产生的磁场与第二对过孔的磁场耦合较小。图中方案C的2对过孔倾斜排列的布局进一步改变了过孔的磁场方向,每对过孔的磁场方向相互正交,可以有效地减小磁场的交叉耦合。通过磁场分析,可以定性地评估不同布局方案对串扰的影响。

图6 三种差分过孔排列方案的磁场分布Fig.6 Magnetic field distribution of three differential via arrangement schemes

3 仿真结果与分析

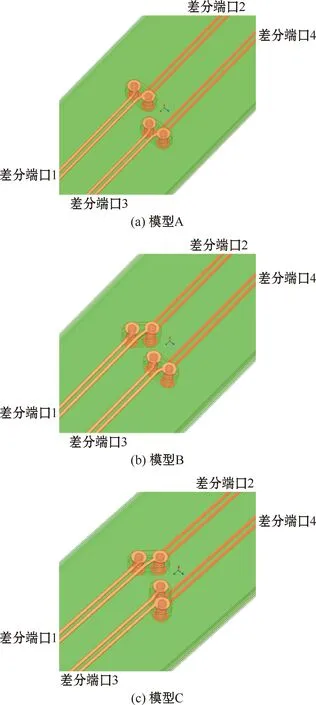

利用HFSS软件对所提出的差分过孔排列方案的传输性能进行仿真,通过0.1~30 GHz的扫频求解方式计算出两差分对对应的四端口网络的S参数。同时使用集成电路设计软件ADS联合HFSS计算四端口网络的插损串扰比(insertion crosstalk ratio,ICR)和集成串扰噪声(integrated crosstalk noise,ICN),以验证所提方案的有效性和可靠性。

如图7所示,通过HFSS建立了平行正交过孔模型和2种倾斜过孔模型,其中模型A、模型B、模型C分别与方案A、方案B、方案C相对应。模型采用0.8 mm厚的6层板,其中1、3、6为信号层和电源层,其他层为参考层或电源层。板材为FR4,其相对介电常数为4.4。差分过孔直径为0.6 mm,反焊盘直径为0.8 mm。差分对内两过孔的中心间距为0.8 mm,相邻差分对中心点之间的水平间距为1.7 mm。顶层和底层的微带线宽度均为0.1 mm,设定差分端口1和差分端口3为激励端,差分端口2和差分端口4为接收端。

图7 三种模型的3D示意图Fig.7 3D schematic diagrams of three models

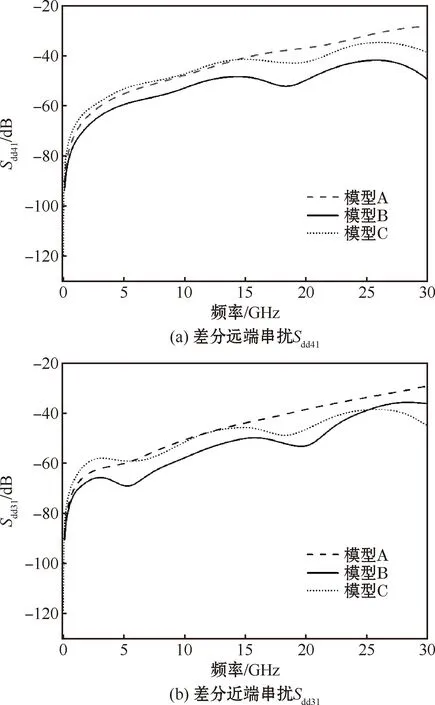

图8给出了3种模型的串扰仿真结果。图8(a)对比了3种模型的远端串扰。在低于15 GHz的频带内,模型B的差分远端串扰最小,模型A的差分远端串扰小于模型C。而在超过15 GHz的频带内,模型B和C的差分远端串扰都小于模型A。图8(b)给出了3种模型的差分近端串扰对比结果。在频率低于5 GHz的情况下,模型A的差分近端串扰小于模型C。而在频率高于5 GHz的情况下,模型B和C的差分近端串扰均小于模型A。在低于25 GHz的频带内,模型B的近端串扰小于模型C;而在25~30 GHz频带内则相反。在频率为30 GHz时,模型B的Sdd41为-49.5 dB,Sdd31为-36.1 dB,相比于模型A,差分远端串扰和差分近端串扰分别降低了21.3 dB和6.9 dB。同时,模型C的Sdd41为-38.7 dB,Sdd31为-44.6 dB,差分远端串扰和差分近端串扰比模型A分别降低了10.5 dB和15.5 dB。综上所述,在高频带内,2种倾斜排列的差分过孔方案都能够显著降低串扰。

图8 三种模型的串扰曲线对比Fig.8 Comparison of crosstalk curves of three models

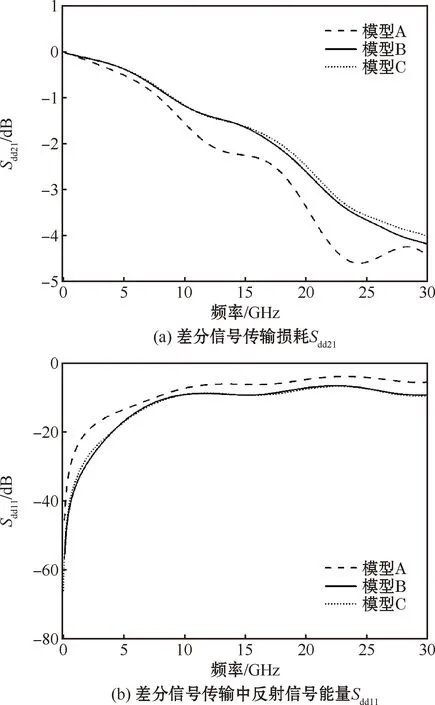

图9对比了Sdd21和Sdd11。Sdd21描述了差分信号在传输过程中的损耗,Sdd11反映了差分信号传输中产生的反射信号的能量大小。通过结果对比发现,相较于模型A,模型B在传输性能方面表现较好,同时信号反射水平较低;与此同时,2种倾斜过孔方案在传输性能曲线上表现出非常相似的趋势,表明其传输性能相近。

图9 三种模型的传输性能曲线对比Fig.9 Comparison of transmission performance curves of three models

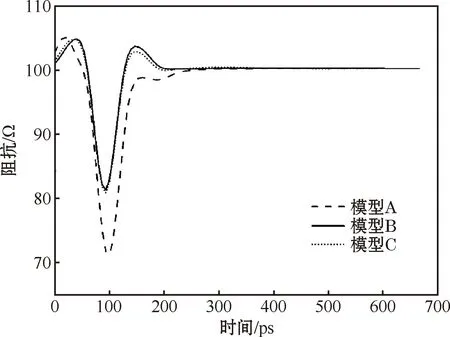

时域反射(time domain reflectometry,TDR)参数显示信号在传输线上的阻抗变化情况,当TDR曲线出现向下的尖峰时,表明此处是由于过孔的寄生电容导致的阻抗减小,是信号的主要反射点。图10给出了3种模型对应的TDR曲线。结果表明,倾斜排列过孔方案的阻抗变化幅度更小,意味着引起的信号反射较少。

图10 三种模型的时域TDR曲线对比Fig.10 Comparison of time-domain TDR curves of three models

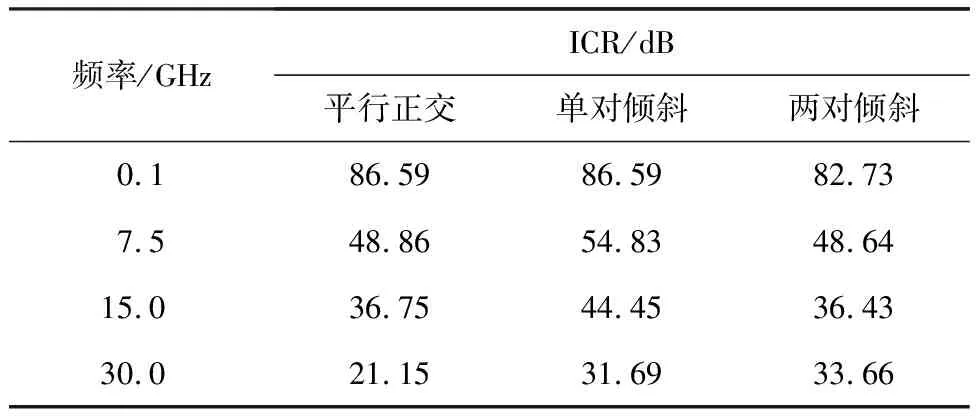

ICR是衡量信号传输中插入损耗与串扰之间关系的指标,较高的ICR值表示较小的信号损耗和干扰。使用ADS软件进行计算,以差分端口2为例计算各端口对该端口的干扰,得到结果如表1所示。通过对比发现,在0.1~30 GHz的范围内,单对倾斜排列过孔结构的ICR值更高,表明该种倾斜排列的差分过孔具有更高的可靠性。

表1 0.1~30 GHz频带内ICR值对比Table 1 Comparison of ICR values in 0.1~30 GHz band

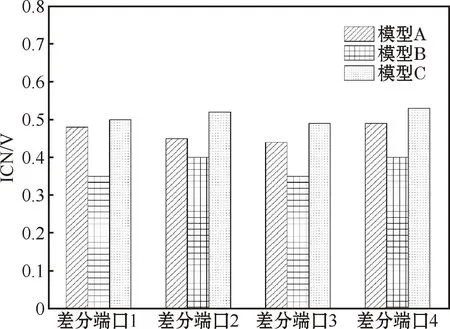

除此之外,为了量化串扰的时域电平,本节还引入了ICN指标,通过对信号波形进行积分计算,从而对串扰电平量化评估。ICN的值越大,表明串扰电平越高。图11给出了在符号速率为30 GBd时,3种不同方案的ICN情况。可以看到,与模型A和模型C相比,模型B的各个端口的串扰电平最低,ICN低了约10%~20%。

图11 三种模型各端口ICN对比Fig.11 Comparison of ICN at each port of three models

以上仿真结果表明,在0.1~30 GHz的频带内,模型B的综合性能优于其他2种模型。所提出的单对倾斜差分过孔的排列方案在0.1~30 GHz的频段内表现出了良好的串扰抑制能力,且没有牺牲其传输性能。与其他现有排列结构相比,本文提出的单对倾斜过孔方案在高速PCB设计中更具优势。

4 结束语

本文在保持过孔间距不变的情况下将差分过孔偏移放置,提出了2种倾斜排列的差分过孔方案以降低串扰。与传统平行正交的差分过孔排列方案相比,倾斜排列的差分过孔能够显著降低串扰,特别是在频率为30 GHz时,单对倾斜排列方案的差分远端串扰和差分近端串扰分别降低了21.3 dB和6.9 dB,两对倾斜排列方案的差分远端串扰和差分近端串扰分别降低了10.5 dB和15.5 dB。此外,2种倾斜排列的过孔在布局时占用更少的空间,有益于高密度的PCB设计。综上所述,所提的2种差分过孔排列方案在抑制串扰上具有一定的优势,可以为高速电路设计提供参考。