基于新型SAR ADC电容阵列的RFID温度传感器*

张 显,徐 勇,李 峤,李青龙

(陆军工程大学,江苏 南京 210001)

0 引言

无源超高频射频识别(Radio Frequency Identification,RFID)技术在当今社会中的应用越来越广泛,在传感器领域中,无源RFID 传感器具有较好的应用前景。相对于其他传感器来说,无源RFID 传感器体积小,仅仅需要一个芯片以及天线便可构成一个传感器,并且功耗低,此外,由于本身不带电池,它的成本也很低。无源RFID 传感器中,温度传感器仍然是市场占有量前三的传感器之一[1],因此无源RFID 温度传感器具备强大的市场竞争力,对无源RFID温度传感器相关的研究与设计是十分有前景的。

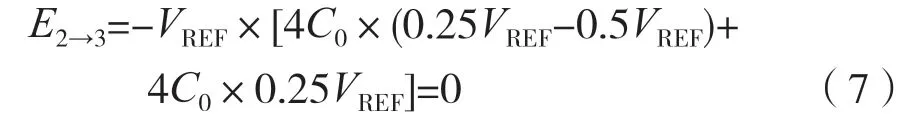

无源RFID 温度传感器通常由4 部分构成,分别为带隙基准电路、比较器电路、SAR ADC 电容阵列以及数字控制逻辑电路。带隙基准电路主要用于提供基准电压以及一个随温度线性变化的电压,方便模数转换器(Analog-to-Digital Converter,ADC)模块的测量。比较器承担着将模拟信号转变成数字信号的任务,它将输入的两路模拟信号进行对比,通过差分输出的方式,输出两路高低电平,在所设计的低功耗逐次逼近型(Successive Approximation Register,SAR)ADC 当中,对比较器的功耗要求较高,因此通常选用受时钟信号控制的动态比较器。传统的ADC 通常采用电阻阵列或者电容电阻结合的阵列,可以减少芯片面积,但在低功耗应用场景中,更多的是只采用电容阵列,通过电荷重分配的形式消除模块的静态功耗。缺点是随着位数的增加,单位电容的数量呈几何倍数增长,将会大大增加系统的动态功耗。数字控制逻辑主要用于ADC 电容阵列中相应的开关管控制。

目前,已有文献针对SAR ADC 的电容阵列进行了低功耗的研究[2-3]。文献[2]中提出了一种改良的Hybrid 电容阵列结构,前三步电平转换做到了无动态功耗,但是所用电容数量依旧会随着位数增加呈几何倍增长。文献[3]中通过分段电容的形式降低了电平,但是只有最高位比较时不消耗能量。因此,本文在分段电容以及Hybrid 电容阵列结构的理论基础上,阐述了一种高三位比较不消耗功耗的分段电容阵列。与传统的电容阵列相比,单位电容数量并没有随着位数的增加呈几何倍增长,同时前三位的比较不消耗能量,因此电容阵列的动态功耗也得到了有效的降低,采用台积电(TSMC)0.18 μm进行Cadence 仿真并流片。

1 带隙基准电路

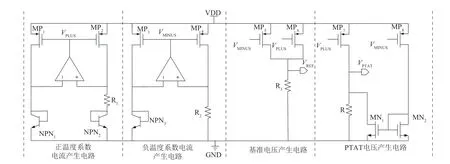

为降低温度传感器的功耗,这里只采用经过一阶补偿的基准电路,分别用两个运放,组成了一个正温度系数电流产生电路和一个负温度系数电流产生电路,如图1 所示。

图1 带隙基准电路原理

PMOS 管MP5与MP6的栅极分别与MP1和MP3的栅极相接,通过电流镜将正温度系数电流和负温度系数电流镜像给电阻R3,最后经过电阻R3产生一阶补偿的带隙基准电压VREF:

由式(1)、式(2)可以看出,这里需选用相同类型的电阻来抵消电阻因为温度和工艺所可能造成的非线性误差。

正温度系数电压VPTAT是整个感温模块用于衡量 温度的标准。VPTAT和VREF输入ADC 的模拟接口中,经过ADC 的模数转换成10 bit 的数字信息,之后再由上位机中的理想数模转换器(Digital-to-Analog Converter,DAC)程序进行还原,在这个过程中,无论VPTAT的斜率如何,最后经过DAC 还原的电压与VPTAT的偏差值是固定不变的,但是作为温度传感器来说,电压的偏差值需要转换成温度的偏差 值,如:

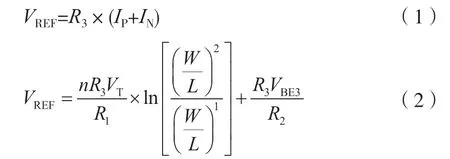

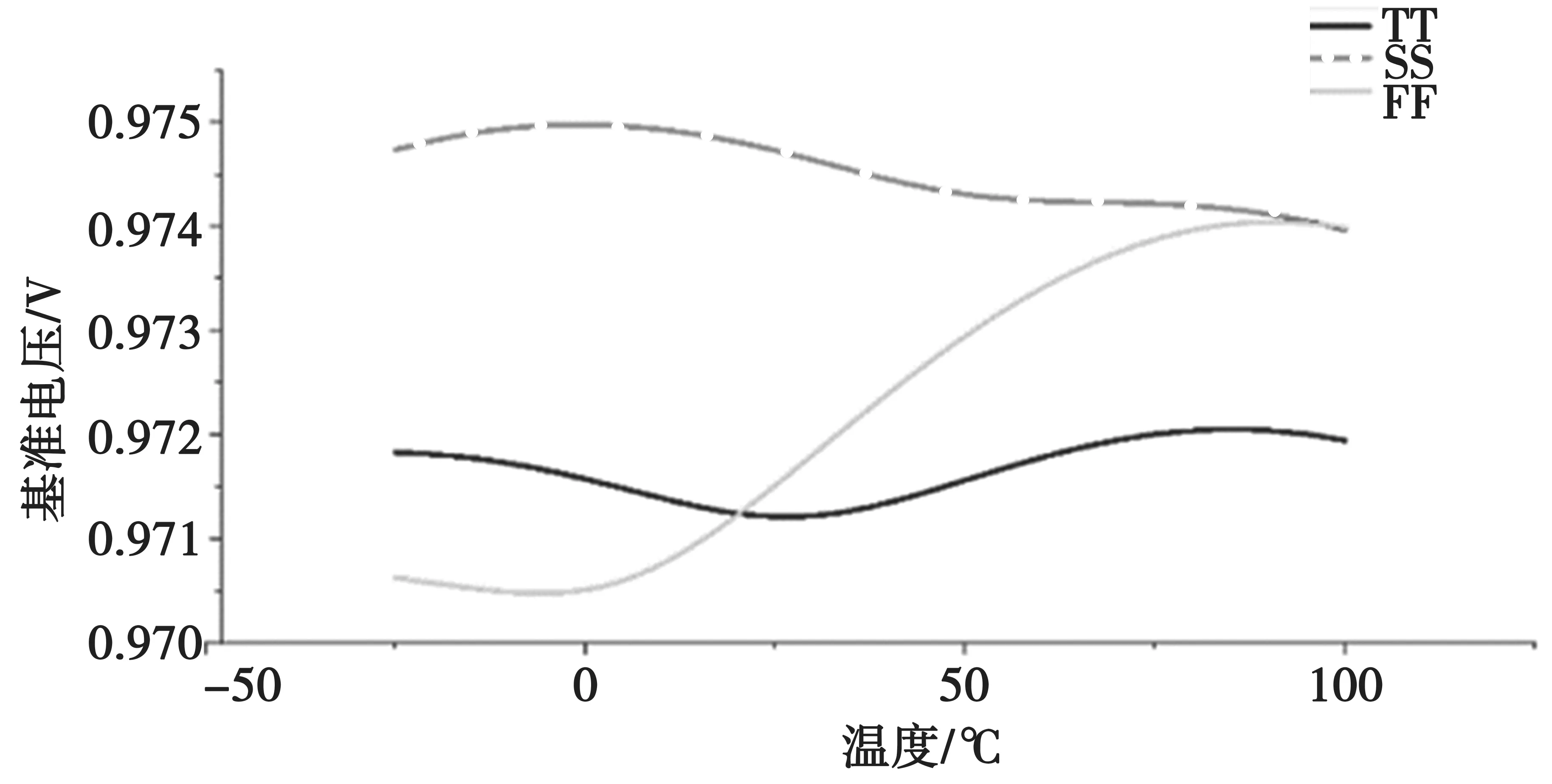

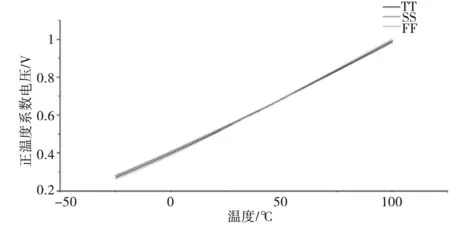

式(3)是由VPTAT电压的偏差量转换成温度的偏差。式中,ΔT是经过上位机的理想DAC 还原后温度的偏差量,kPTAT是VPTAT的斜率,ΔVPTAT是VPTAT的偏差量。由此可知,如果VPTAT的斜率增大,对于温度传感器来说是可以一定程度上减小测量温度的误差。而传统的VPTAT电压产生电路的电压斜率约为2 mV/℃,斜率相对小,所以这里采用正温度系数电流同负温度系数电流加权相减后,加在电阻R 上,得到一个斜率更高的正温度系数电流。图2 和图3 分别给出了带隙基准电压和正温度系数电压在不同corner 下的仿真结果。

图2 是带隙基准电压源在3 个工艺角下电压的温度特性曲线,在TT 模式时,带隙基准电压的温度系数为6.910×10-6/℃;在SS 模式时,带隙基准电压的温度系数为8.290×10-6/℃;在FF 模式时,带隙基准电压的温度系数为2.932×10-6/℃。

图2 带隙基准电压源的温度特性

图3 是分别在TT、SS 和FF 模式下的VPTAT电压随温度的特性曲线图。3 种工艺角下斜率大体相等,均为5.754 8 mV/℃。

图3 3 种工艺角下的正温度系数电压

2 动态比较器电路

在低功耗SAR ADC 的研究与设计中,比较器是一个至关重要的模块。它是整个SAR ADC 的模拟电路中,功耗较大的模块,因此,对比较器进行深入的研究,并且选择合适的低功耗比较器是十分必要的。

在SAR ADC 中,比较器承担着将模拟信号转变成数字信号的任务。它将输入的两路模拟信号进行对比,通过差分输出的方式,输出两路高低电平,高低电平的值与比较器两端电源电压一致。

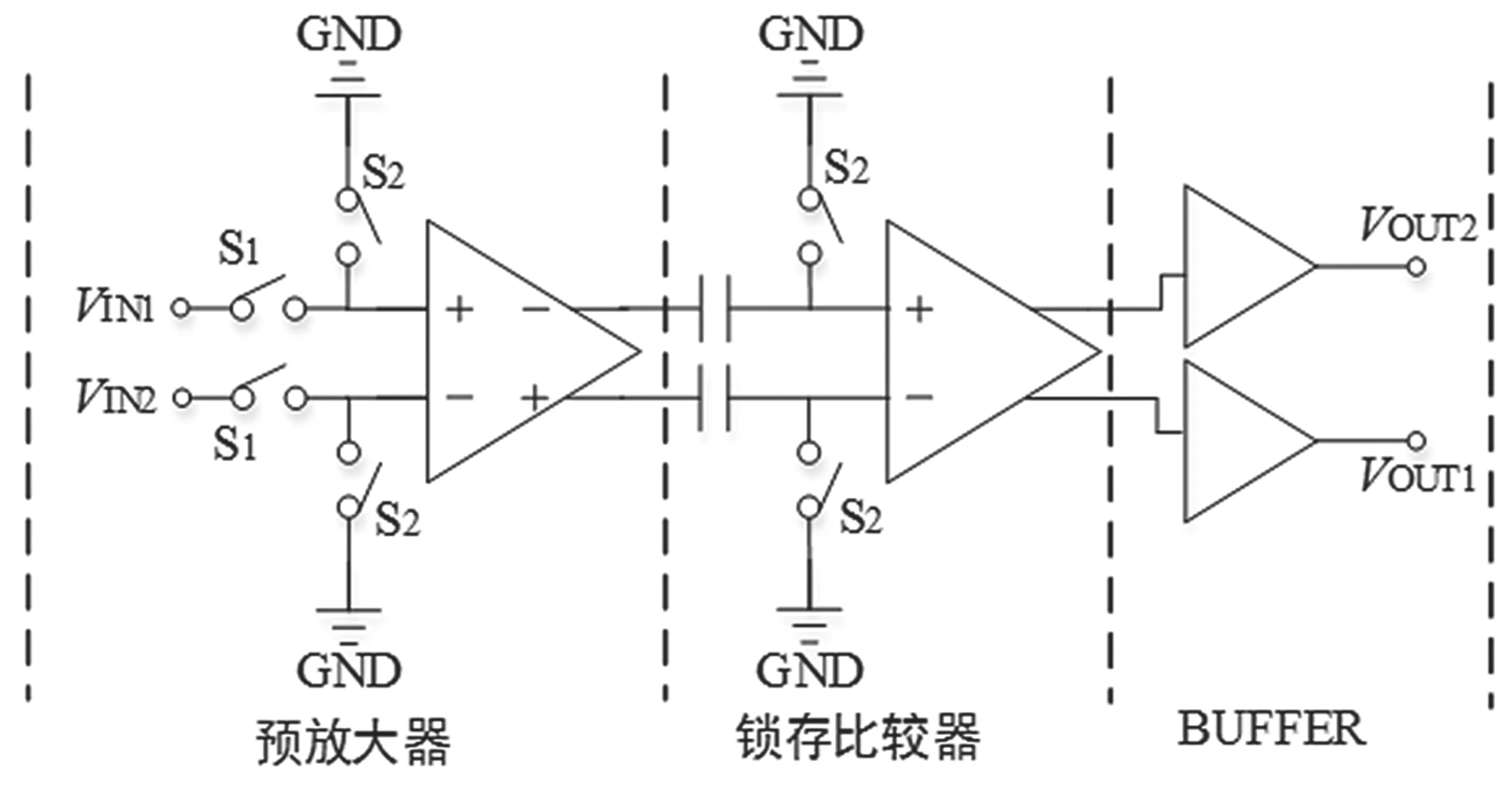

动态比较器结构如图4 所示可以分为3 部分。

图4 动态比较器结构

第1 部分是前置放大器,又称为预放大器。预放大器主要用于隔离锁存比较器对于采样电路的回馈噪声,并且一定程度上降低失调电压。因此这级放大器对于增益要求不高,但是其对带宽的要求较高。它的带宽直接决定了整个ADC 所能达到的最高采样速率,同时较大的带宽还可以降低时延,所以设计一个高带宽低增益的预放大器是十分有必要的。第2 部分为锁存器,主要功能是存储整个动态比较器的结果,便于后端数字电路使用。它能够将前端放大器的输出结果转化为其电源两端的高低电平。对于锁存器来说,最为重要的是电压摆率,即电压向高低电平翻转的变化率。压摆率越大,输出端的电平发生翻转的速度越快。第3 部分用两个驱动作为比较器的输出级,使用了输出失调存储技术对失调电压进行消除,由于比较器是作为 10 bit ADC 的比较单元,因此其要求的最小精度根据基准电压计算可得:

因此,比较器的精度应当小于1.9 mV。

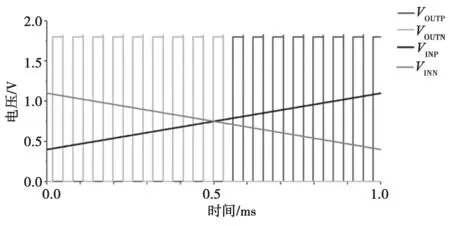

图5 是比较器的瞬态仿真结果,比较器在时钟clk高电平时才工作。输入端VINP和VINN是两个0.4~1.1 V 的斜坡信号。当VINP>VINN时,VOUTP在clk 的上升沿被置1,而VOUTN被置0,在clk 的低电平均为0;当VINP<VINN时,VOUTN在clk 的上升沿被置1,而VOUTP被置0,在clk 的低电平均为0。图中VINP与VINN的斜坡信号交界处,当VINN>VINP仅1.7 mV 时,可以观察到在时钟上升沿VOUTN被置1,因此精度可以达到要求。

图5 动态比较器的瞬态仿真

3 SAR ADC 电容阵列

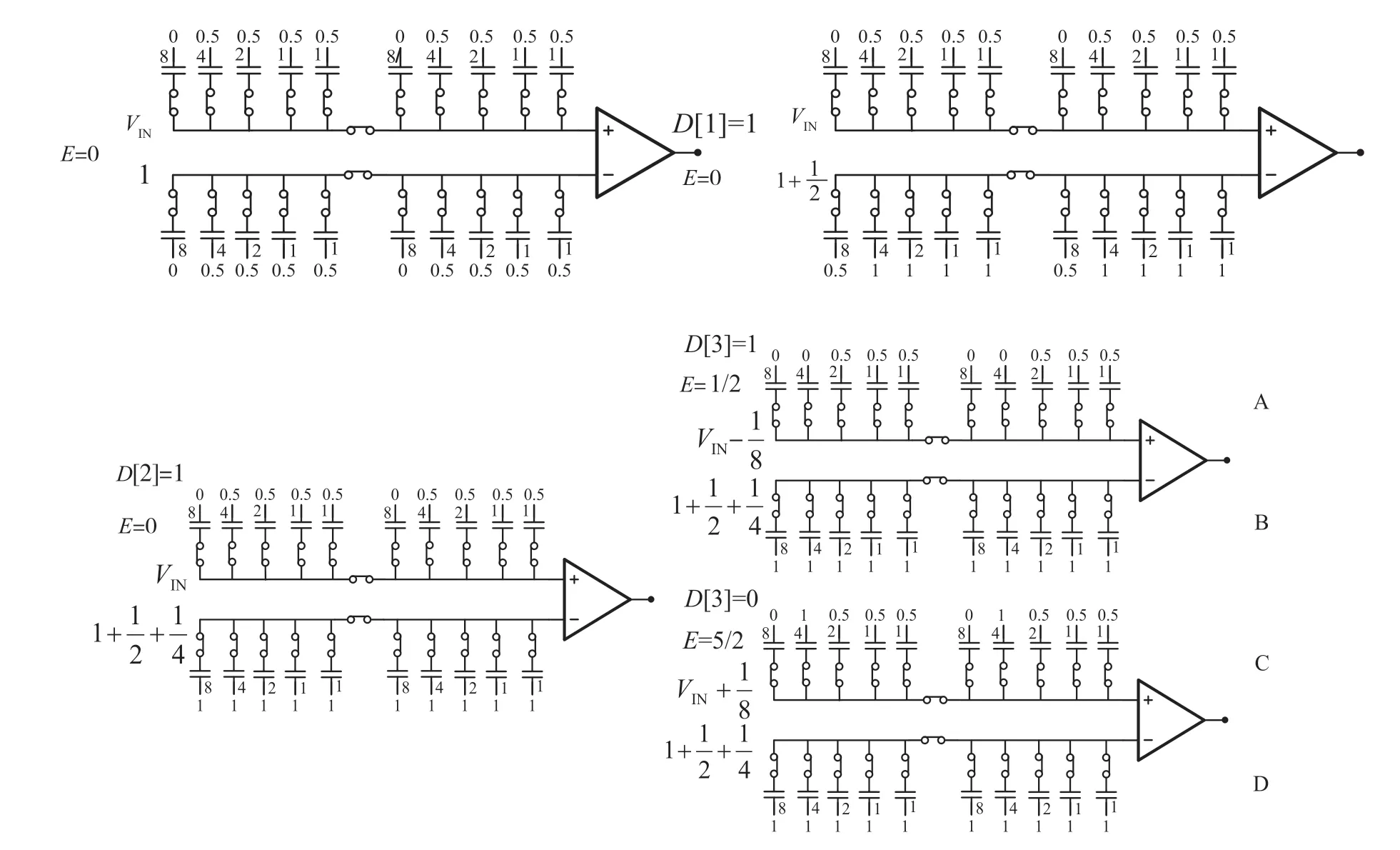

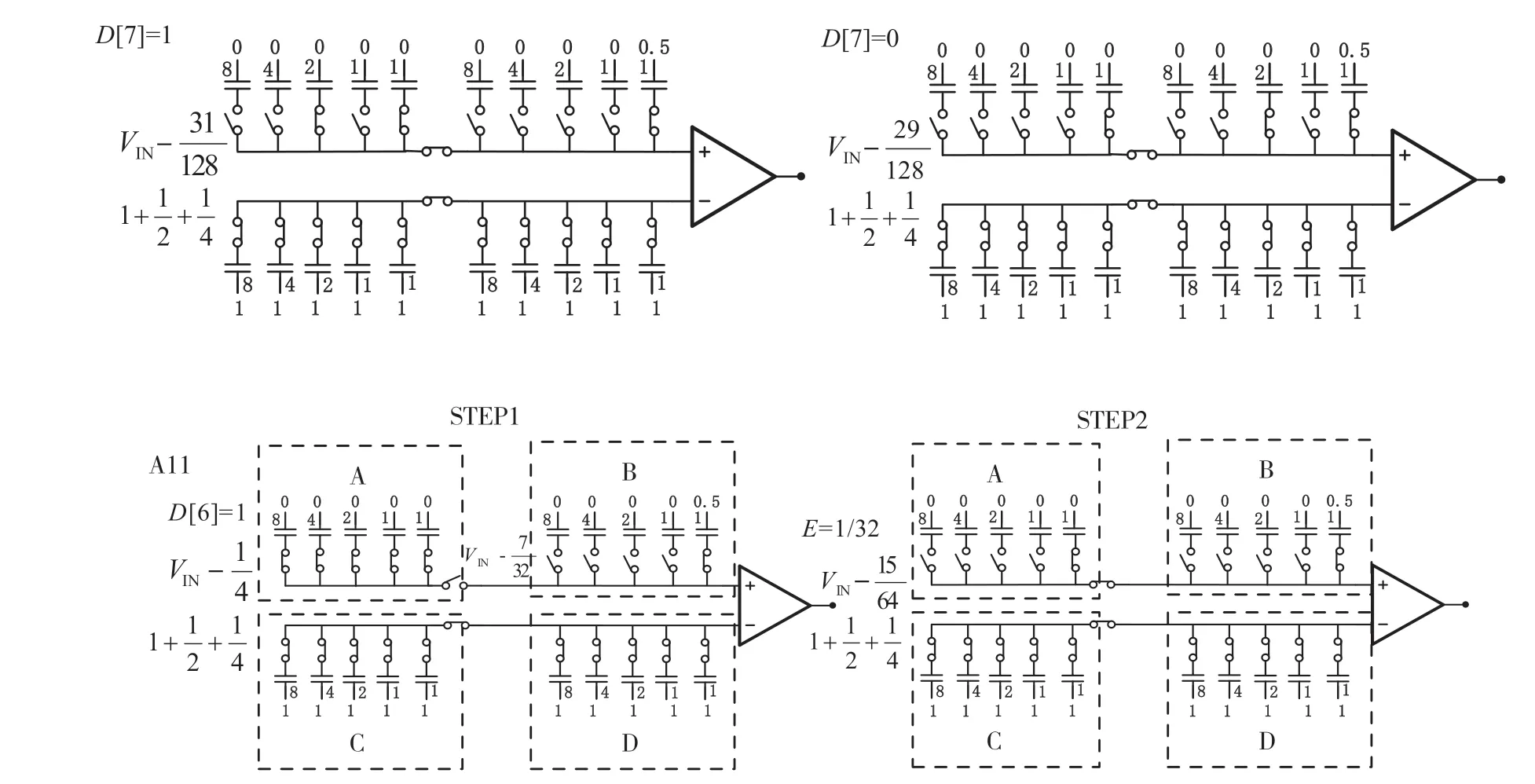

本文在tri-level 电容阵列的高两位不消耗能量的方案基础上,做出仅用64 个单位电容且前3 位不消耗能量的10 bit DAC 电容阵列[4],图6 是该电容阵列前4 位的比较方案。

由于对于对称的电容阵列来说,D[1]为0 和1的两种情况阵列方案对称,因此这里只给出了当D[1]为1 时的后续方案。图6 中,0.5 表示VCM共模电压,1 表示基准电压VREF,0 表示接地,E表示每一步消耗的能量,而D[i]表示比较器的输出结果。同tri-level 电容阵列方案一样,比较器的正输入端连接需要比较的电压Vin,负输入端接基准电压VREF,电容阵列中除最高位电容下极板接地外,其他电容下极板均接VCM。最高加权位(Most Significant Bit,MSB)可以直接进行比较,不改变下极板开关。

图6 SAR ADC 前4 bit 转换过程

当D[1]=1 时,正输入端电压Vin要大于负输入端的基准电压,对负输入端的电容阵列下极板电压进行抬升,整体抬升0.5VREF,则电容的上极板电压也同样抬升0.5VREF。根据前文可以得出这时不消耗能量。

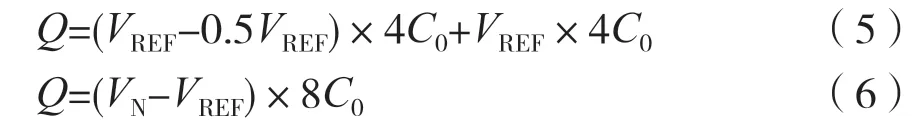

第2 位比较,若D[2]=1,则需要继续抬升负输入端的电容电压,将最高位电容的下极板电压抬升至VREF。根据电荷守恒定律[5]:

得到VN=1.75VREF。

计算第3 步的能量:

当D[2]=1 时,第3 步比较所需的电容阵列开关转换不消耗能量,现在计算当D[2]=0 时,第3 步比较所需的电容阵列开关转换消耗的能量,此时VN过大,因此除了最高位电容外,其余电容的下极板电压均下拉至VCM。根据能量守恒定律并化简可以得到VN=1.25VREF。

计算此时第3 步的能量消耗:

由此可见,无论是卫生管理部门还是医院都要从仁爱和技术能力两个不同维度出发对医生进行激励和管理,努力提升患者尤其是门诊患者对医生的信任水平。在仁爱维度上,医生要更加注重在门诊接诊过程中自身接诊态度的改善和医患沟通技巧的提升,充分考虑门诊患者的需求,把患者的利益放在第一位;在技术能力上,医技水平是医生的基础,医生在努力提升自身专业能力的同时,要充分利用自己所学到的医学知识给患者制定合理的治疗方案帮助患者恢复健康。尤其是对待问诊时间有限的门诊患者,准确利用自己的专业知识在短时间内了解更多的病情帮他们找到病因,治好急病,减少痛苦,增强门诊患者对医生的信任水平。

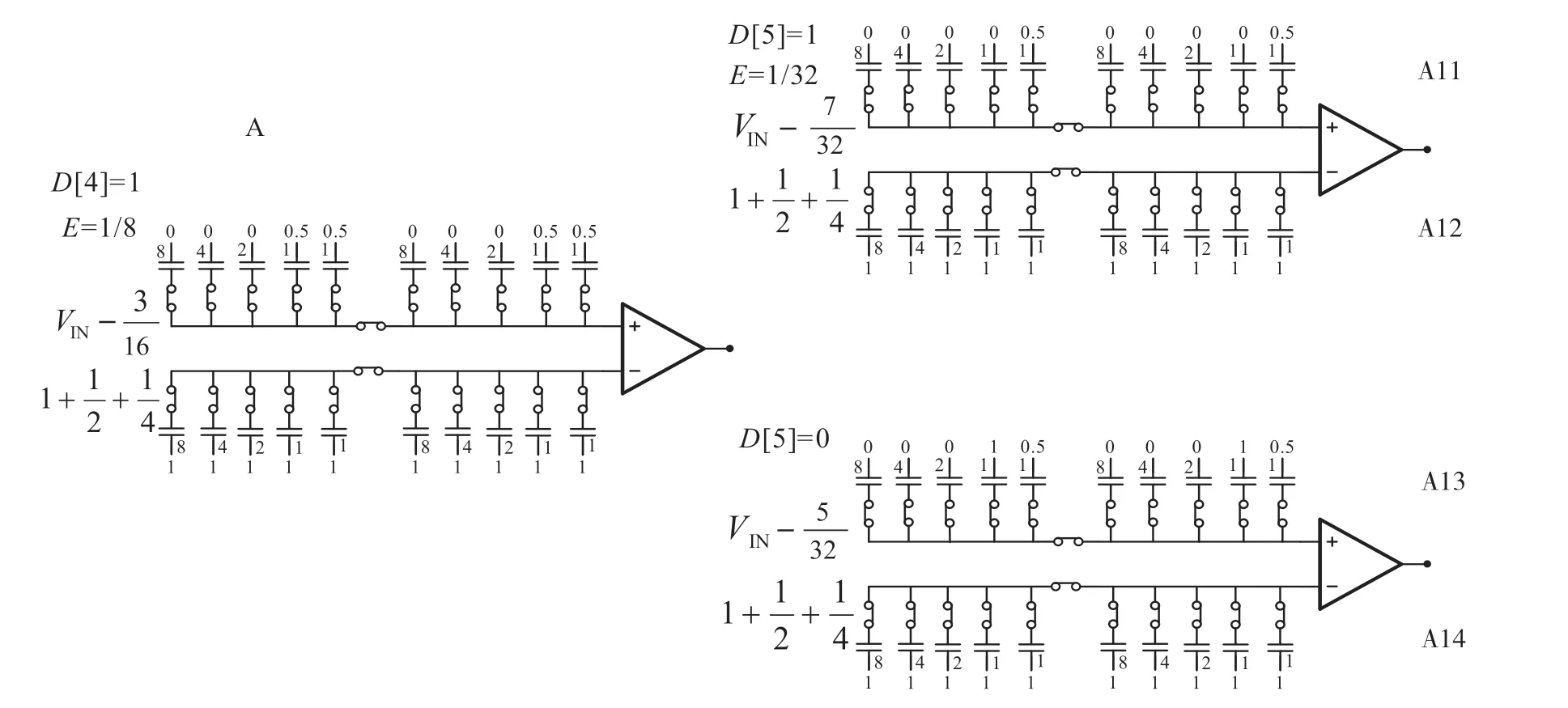

因此,这种方案前3 位的比较均不消耗能量。第3 步中,最高位电容改变电压所需要的电荷直接由其他电容中的电荷转移得到,不需要基准源额外提供电荷。第4 位至第6 位的比较方案,只需要依次对正输入端电容阵列,从4C0开始依次改变下极板电平即可。图7 给出了A 情况第5 位和第6 位的阵列方案。

图7 第5 位和第6 位比较过程

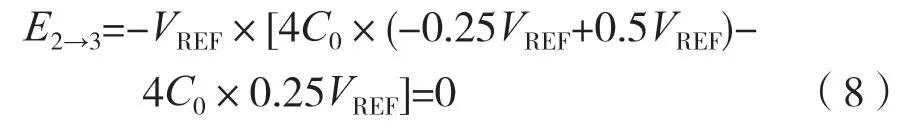

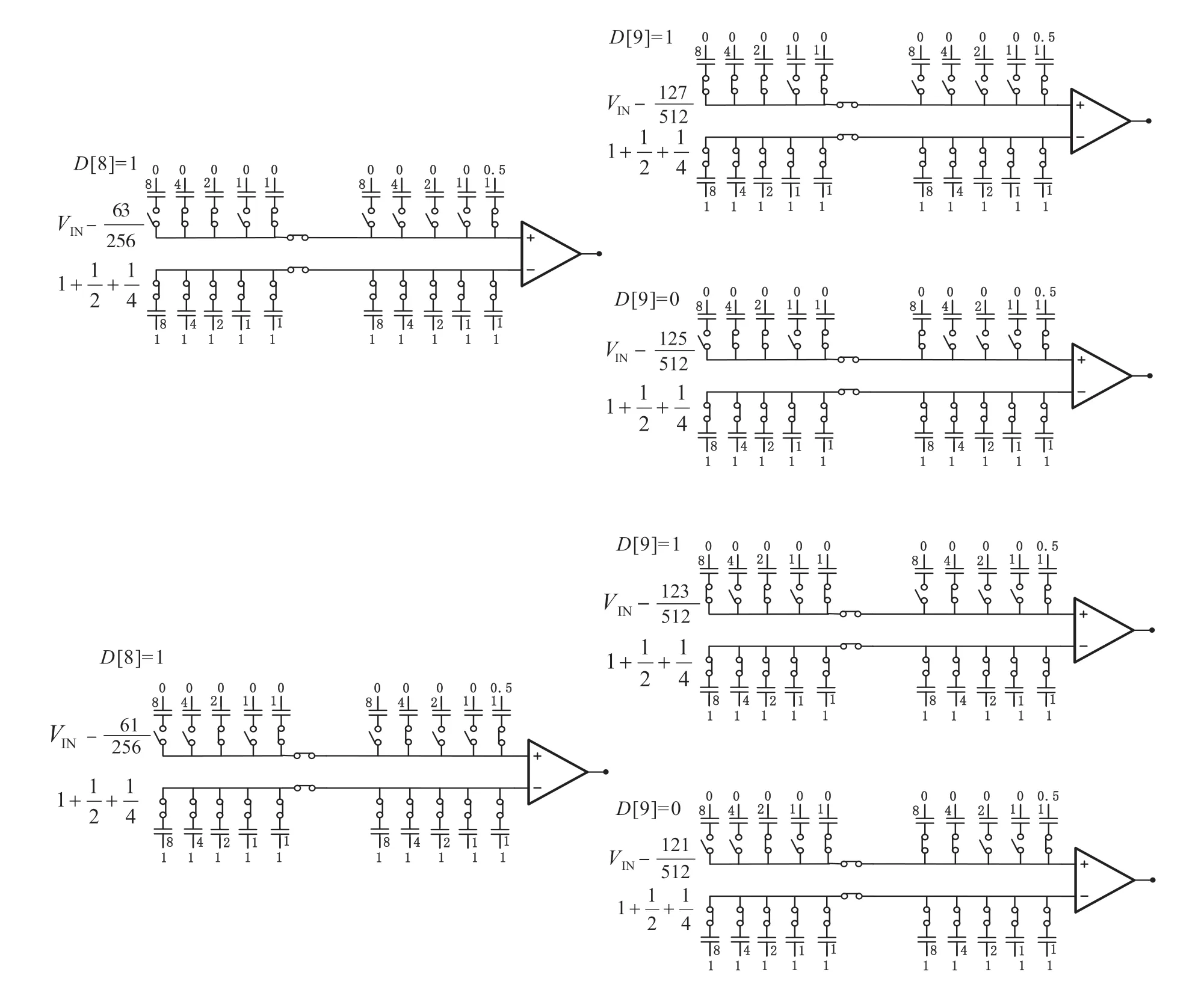

为了达到仅用64 个单位电容就可以实现电路功能的目的,这里第7 位开始的电容阵列方案对传统方案做出了改进。图8 给出了A11 情况下的第7位和第8 位的比较方案。

图8 第7 位和第8 位比较过程

这里仅对正输入端的电容阵列进行了开关的变更,将电容阵列A 的最小单位电容C0的下极板电平由VCM下拉至地,同时断开正输入端两个电容阵列之间的开关。电容阵列B 只有最小的单位电容C0仍接在正输入端上,其他均断开。此时根据电荷守恒定律可以计算出,比较器正输入端两个电容阵列上极板的电压,分别为VIN-0.25VREF和VIN-7/32VREF。然后将电容阵列A 的电容从正输入端上断开,仅留下一个最小的单位电容C0,并将两个电容阵列之间的连接开关闭合,此时继续根据能量守恒定律计算出正输入端电压值为VIN-15/64VREF,相较于第6 步结束时的电平VIN-1/4VREF,增大了1/64VREF,符合第7 步需要改变的电压大小,方案理论可行。

图9 给出了第9 位与第10 位的比较方案。从第8 位比较开始,若比较器的输出结果为1,那么需要将电容阵列A 中的电容从4C0至8C0每一步依次接入比较器的正输入端。若比较器的输出结果为0,那么需要将电容阵列B 中的电容同样也从4C0至8C0每一步依次接入比较器的正输入端。

图9 第9 位和第10 位比较过程

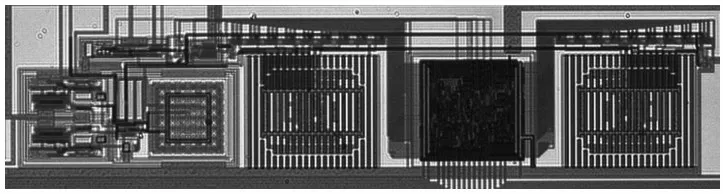

4 芯片版图与测试

图10 是芯片在显微镜下的照片,为了隔离衬底噪声,将模拟电路与数字电路分开放置。左侧为模拟电路,并且加上了双层的Seal Ring。由于开关采用的互补开关,因此控制逻辑输出的控制信号较多,所以将数字控制逻辑放置于两个电容阵列中间,可以减少连线的难度。考虑到衬底的噪声,这里所有模块均用了双层Seal Ring。并且模拟电路与数字电路分开供电。

图10 芯片版图照片

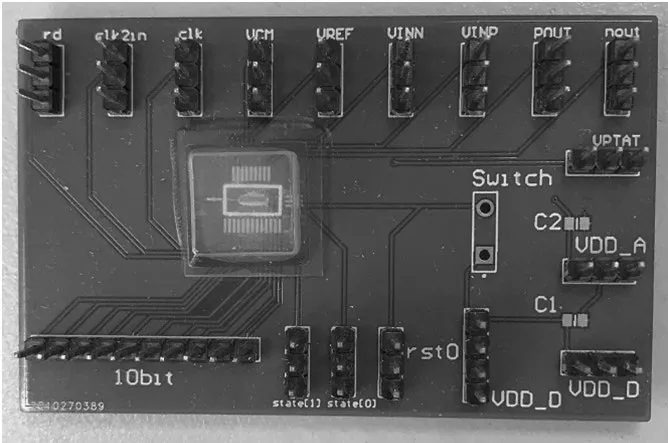

图11 是芯片测试板,PCB 板采用双层走线来实现芯片同外部接口的连接,PCB 板同芯片的接口采用沉金工艺,并通过金丝键合将芯片连接至PCB板,将芯片的模拟电路和数字电路分开供电,提供了10 位并行的排针让芯片的二进制温度数据能并行传输给现场可编程门阵列(Field Programmable Gate Array,FPGA)开发板的拓展IO 接口。

图11 芯片测试板

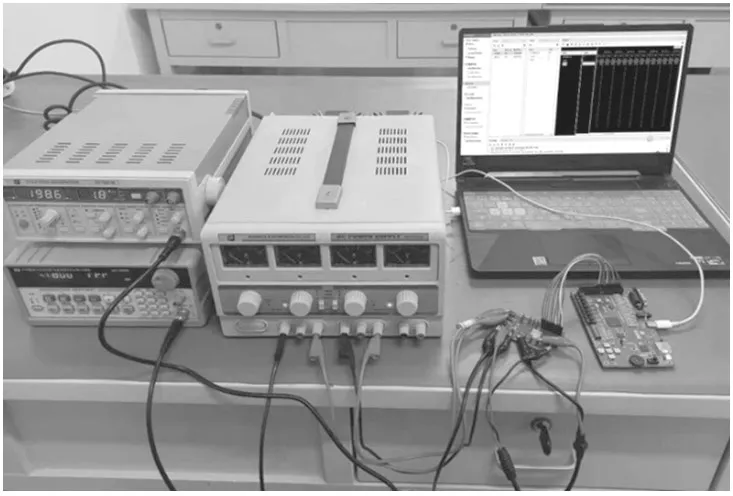

图12 是芯片测试场景的照片,芯片测试选用了3 台仪器,分别为2 台函数信号发生器和1 台直流电压源。

图12 芯片测试

F120 型函数信号发生器用于产生了一个频率为60 kHz 的时钟信号,由于ADC 完成一次10 bit转换需要15 个时钟周期,因此采样频率为4 kHz。DF1641B 型函数信号发生器则用于产生200 Hz 的正弦波信号作为SAR ADC 输入端的全摆幅输入信号,其输入振幅为550 mV,并且叠加了750 mV 的DC Offset 以形成一个0.2~1.3 V 的正弦波信号,大小同比较器仿真时的输入范围所对应。另用一台3个输出端的直流电压源分别给芯片的模拟电路和数字电路供电,进行一个电源的隔离。用Artix-7 系列的FPGA 开发板作为ADC 芯片输出信号的存储模块,其型号为xc7a35tcsg324。运用Vivado 进行仿真并完成相关程序的烧录,最后用扩展IO 口对ADC 的信号进行读取,在电脑中使用Vivado 的内嵌工具lia 进行波形的读取,并通过UART 协议读取存储器中的大量测试数据。

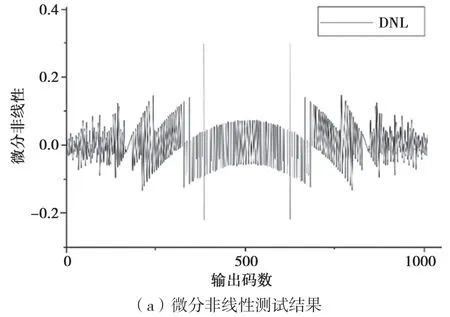

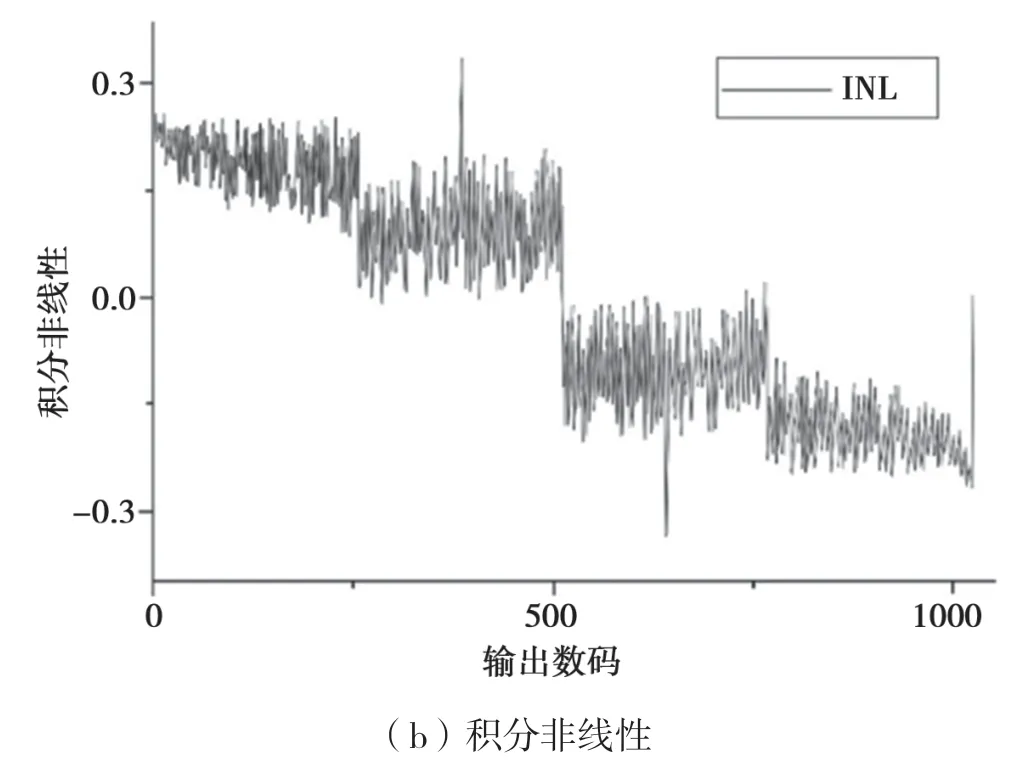

图13 芯片静态性能测试结果

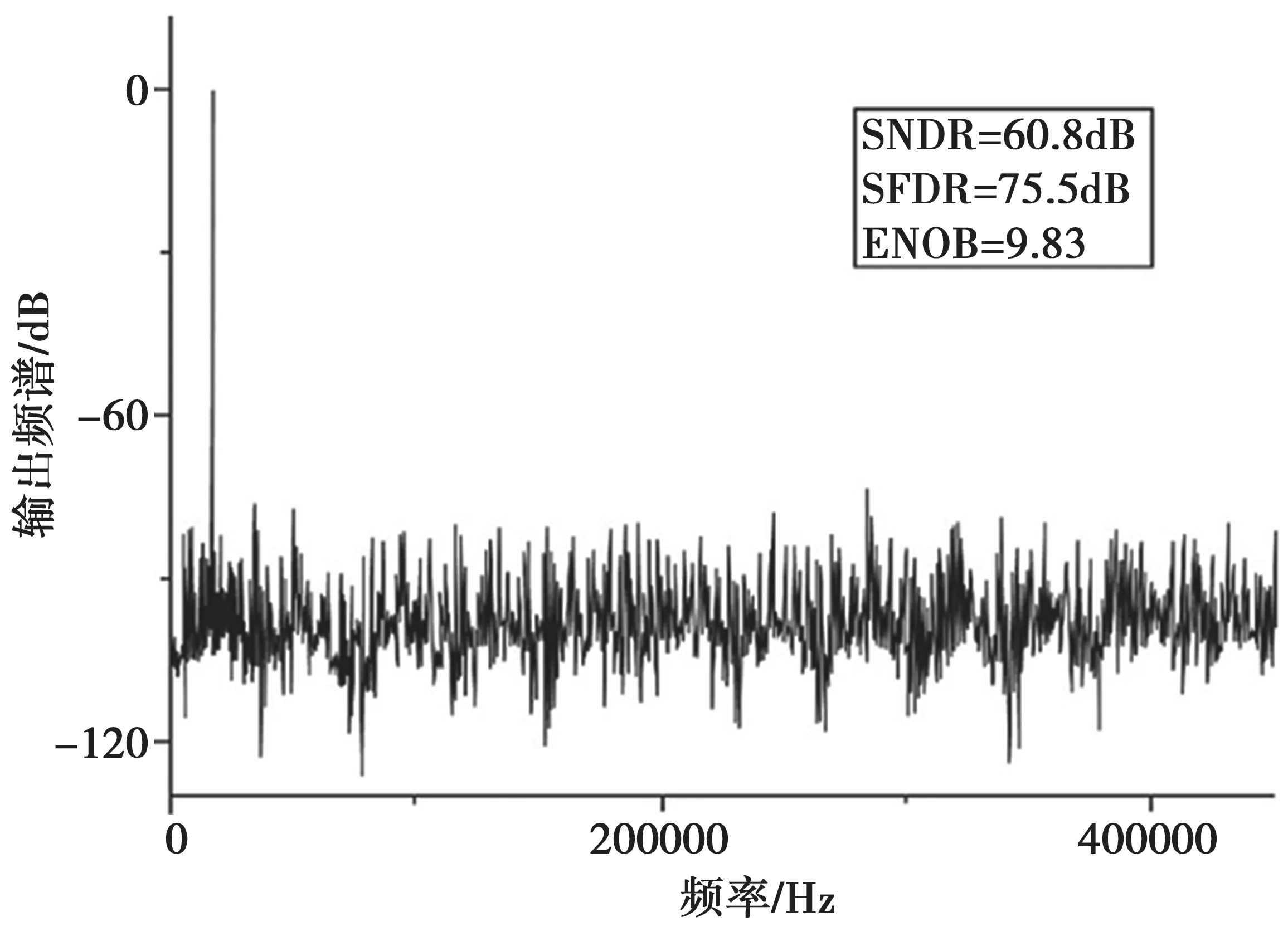

图14 是芯片的动态测试结果,该结果同样需要UART 协议对FPGA 存储器进行数字信息的读取,并将得到的数据通过MATLAB 软件中的算法程序处理才可以得出。该芯片无杂散动态范围(Spurious-Free Dynamic Range,SFDR)为59 dB,SNDR 为45.1 dB,芯片有效位数7.2 bits。

图14 芯片动态性能测试结果

导致以上测试所得结果恶化的主要原因有,流片工艺和版图匹配的偏差,由于该设计为了节省ADC 的动态功耗降低了单位电容的数量,从而导致电容阵列的匹配程度并不理想。数字模块位于两个电容阵列的中间,虽然降低了版图连线的难度,但在双极型互补金属氧化物半导体(Bipolar Complementary Metal Oxide Semiconductor,BiCMOS)的工艺中却给衬底带来了噪声的干扰,导致芯片测试结果的恶化。

5 结语

本文采用TSMC BiCMOS 0.18 μm 1P4M 工艺,完成了应用于RFID 温度传感系统中感温芯片部分模块的研究与设计,并完成了流片和相应SAR ADC性能的测试验证。

在现有的SAR ADC 电容阵列原理的基础上,进行了电容阵列方案的进一步创新,提出了一种高3 位比较不消耗能量,且仅用64 个单位电容就能完成10 bit 比较的电容阵列方案。

测试结果表明芯片中ADC 的精度同仿真相比有一定程度的恶化,芯片版图的失配影响占比重较大,需要对芯片进行一定程度的优化,例如增加和优化上位机的校准,或者在设计芯片的过程中增加数字校准电路可以从外部对芯片内部偏置电路的连接方式进行修正。

后期将进一步对无源RFID 感温芯片与读写器之间的收发通道进行研究。包括感温芯片中数字基带电路和调制电路的设计,调制电路与读写器之间传输信息的方式,相关空中接口协议的研究,以及标签天线的设计。