数字电路中“逻辑非”的用法辨析

方开洪,张函博,梁海兵,张 硕,王 强

(兰州大学 核科学与技术学院,甘肃 兰州 730000)

《模拟电路与数字电路》是高等教育院校电气、自控、机电、电子类专业的专业基础课,在整个专业课程体系中占有重要地位[1-2]。在高校“新工科”的历史背景下,对创新型工程人才的培养提出了更高的要求[3-6]。在教学实践中发现,数字电路部分中,“逻辑非”符号的应用与标注不尽一致,给数字电路教学中数字逻辑电路的分析和设计带来一定困扰。如何对“逻辑非”符号在不同电路以及电路中不同位置中表现的含义进行详尽阐明,是亟待解决的问题[7]。

1 国家标准GB/T4728对“逻辑非”的规定

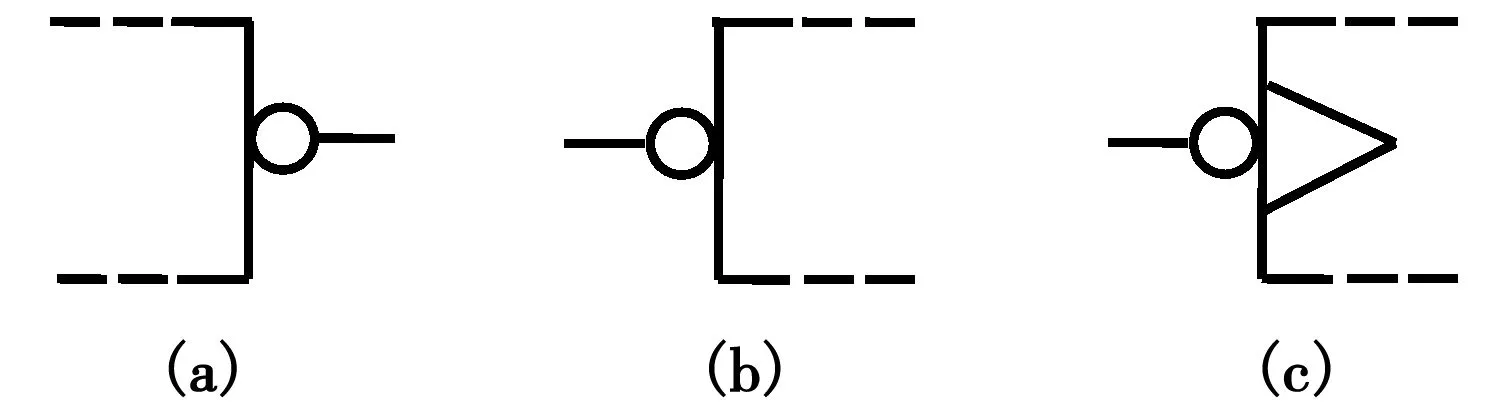

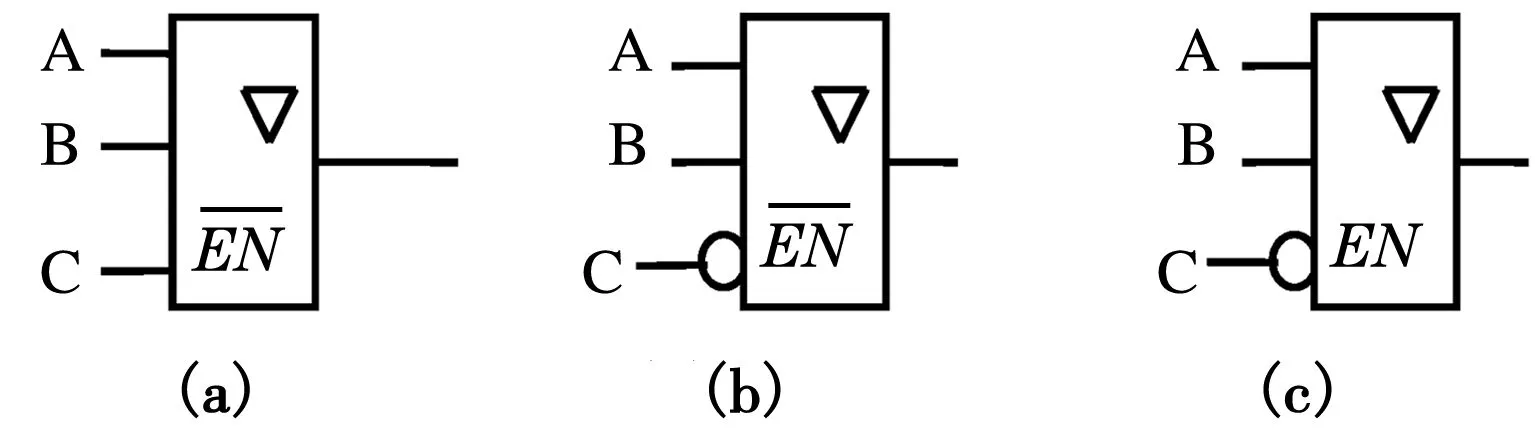

逻辑符号是逻辑电路的基础语言,包括文字符号、图形符号和绘图符号。数字逻辑电路是由各种逻辑器件符号组成的电路系统,它将理论和实际电路联系起来,通过逻辑电路的分析设计,指导实际电路的设计、搭建和监测。为了便于交流,国家制定和修订了《电气简图用图形符号》系列国家标准GB/T4728,其中,第12部分:二进制逻辑元件(GB/T4728.12)中针对常见的二值逻辑符号进行了规定[8-10]。与“逻辑非”符号的相关的图形符号如图1所示。

图1(a)为逻辑非(输出端),其编号为S01467,形状为圆圈,该符号用于输出端,表示内部1状态与输出端外部0状态对应;图1(b)为逻辑非(输入端),其编号为S01466,形状为圆圈,该符号用于输入端,表示输入端外部0状态与内部1状态对应;图1(c)为逻辑非动态输入,其编号为S01473,形状由圆圈和等边三角形组成,该符号用于输入端,表示内部1状态(暂态)与外部1状态到外部0状态的转换过程相对应,其他所有时间,内部逻辑状态为0。从图1(a)、(b)可以看出,非符号既可以放在逻辑电路的输入端,也可以放在逻辑电路的输出端。图1(c)表示的意思,说得通俗一点:当这个输入端口的电平由高电平1变换为低电平0时,这个输入端将起作用,其他情况如高电平1、低电平0以及由低电平变0换为高电平1时都不起作用。

在二进制逻辑电路中,以高、低电平表示两个不同的逻辑状态,高电平(H)、低电平(L)和逻辑状态1、0之间的关系,可以采用正逻辑或负逻辑约定,即若将高电平定义为逻辑1状态,将低电平定义为逻辑0状态,称为正逻辑约定;反之,将高电平定义为逻辑0状态,将低电平定义为逻辑1状态,称为负逻辑约定。输入端的“○”符号,强调“低电平有效”,在电路设计上采用“负逻辑”思路,并不是在输入端多接了一个非门电路;而输出端的“○”符号则表示取反,例如在TTL逻辑电路中,逻辑非由晶体管工作在饱和与截止两种状态来实现,同时,这种非门电路还有提升驱动能力的作用。

图1 逻辑非符号的几种图形

2 “逻辑非”的基本写法

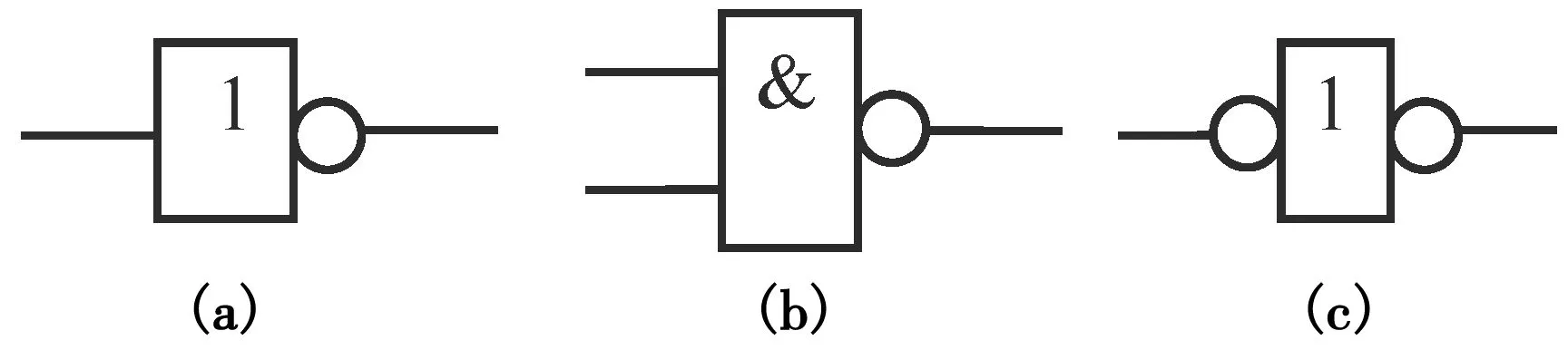

在逻辑图中,“逻辑非”用“○”表示。图2中(a)为非门电路,(b)为与非门电路,符号“○”都表示取反。图2(c)的输入端口和输出端口均标有“○”,均表示取反,即取反两次,相当于传输门电路,其输入端口的“○”除了取反之外,还表示低电平有效,即这一输入端口输入为0时,该输入端口将起作用。

图2 基本逻辑电路

3 “-”或“○”的其他含义

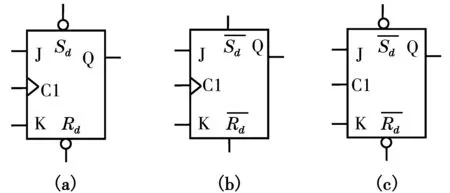

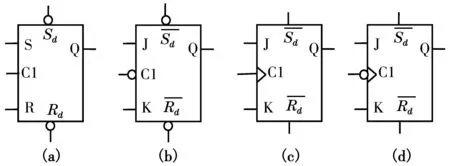

3.1 低电平有效,或低电平使能

在逻辑电路中,习惯上采用正逻辑。在三态门、数字集成电路的使能端(Enable)以及触发器的超前置位复位输入端,用“-”和“○”表示低电平有效或低电平使能;若没有标“-”或“○”,则表示高电平有效或高电平使能,图3所示为JK触发器,图3(a)中所示的超前置位复位端口Sd和Rd,用“○”表示该端口为低电平有效,即这两个端口平时输入高电平1信号,此时该输入对整个电路不起作用,当输入低电平0信号时将起作用,对输出端Q实现超前置0或超前置1;图3(b)所示的超前置位复位端口,在标号Sd和Rd上标了“-”表示低电平有效;图3(c)所示的超前置位复位端口,除了标有“○”符号外,Sd和Rd上也标了“-”符号,同样表示该端口为低电平有效。

图3 J-K触发器的超前置位复位端口

图4所示的三态门逻辑电路中,端口EN为使能端口,或者叫控制端口,即这个端口的输入电平正确则该电路可以正常工作,否则为高阻状态,不能工作。图中“-”和“○”均是等价的,表示低电平有效或低电平使能。

图4 三态门逻辑电路

低电平有效或低电平使能,实际与GB/T4728.12对逻辑非输入端的规定是一致的,都表示输入端外部的0状态与电路内部的1状态对应。即与图1(b)表示的含义相同。

3.2 低电平触发,或下跳边沿触发

同步触发器为触发信号高低电平触发,主从触发器属于触发信号边沿触发。如果触发端口没有标“○”,则表示高电平触发,或上升边沿触发;如果触发端口标有“○”,则表示低电平触发,或下降边沿触发。如图5所示的各触发器,图5(a)中触发器的触发端口C1无“○”也没有三角形符号,表示时钟脉冲高电平触发;图5(b)中触发器的触发端口C1有“○”但是无三角形符号,表示时钟脉冲低电平触发;图5(c)中触发器的触发端口C1无“○”但是有三角形符号,表示时钟脉冲上升边沿触发;图5(d)中触发器的触发端口C1有“○”并且也有三角形符号,表示时钟脉冲下降边沿触发。

图5 J-K触发器的触发端口

触发器触发方式的表示方法,正是依据《电气简图用图形符号》第12部分,二进制逻辑元件(GB/T4728.12)的规定而设计的。由图1可以看出,对于输入端口,“○”与三角形结合表示这个输入端口由高电平1转换为低电平0时,这个端口的信号将起作用,触发器将被触发,而其他情况,不管是高电平还是低电平,也不管电平从0变换到1,触发器均保持状态不变。

3.3 反相输出

图6 触发器的输出情况

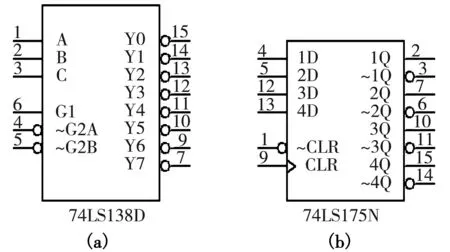

3.4 用“~”符号表示“逻辑非”

数字电子技术的仿真软件如Multisim、PSpice、Proteus等使用的是美国电气符号标识,与常见教材上的符号有所不同,容易出现误解。Multisim仿真软件中,端口带有“○”、名称前面带有“~”的都表示低电平有效或输出为低电平。图6(a)为三八译码器(74LS138),引脚4、5、6为使能端,其中端口标有“~G2A”和“~G2B”,同时也标有“○”,在输入端,表示低电平有效;译码器的引脚7~15为输出端口Yi(i=1~7),标有“○”,表示当译码器正常工作时,对应于地址输入端(ABC)的输出端Yi为低电平,这样设计的目的是为了匹配后续电路的低电平输入的要求。图6(b)为四路D触发器(74LS175),引脚1和9为触发输入端口,其中引脚1带有“○”且名称前带有“~”,表示低电平触发,引脚3、6、11和14标有“○”和“~”,表示引脚2、7、10和15对应的反相输出端。也就是说,引脚1上输入低电平时,输出端被清零,即,引脚2、7、10、15输出低电平,相应地,引脚3、6、11、14输出高电平。

4 结 论

随着电子信息技术的发展,各种新型器件、各种仿真软件层出不穷,逻辑器件的符号也略有差异。需要对不同标准的符号、来自不同软件的各类逻辑符号,从其功能出发,从实际应用出发,理解各逻辑符号的作用。

一般情况下,逻辑变量的取反,在国标中常用“-”符号,美国电气符号标识中常用“-”符号;而逻辑图形中,用“○”符号表示输入输出端的逻辑取反。其中“~”和“-”出现在文本和逻辑表达式中,“-”符号标注于变量或表达式的上面,“~”符号标注在变量的左边,“○”符号标注在图形的输入或输出端。“○”在输入端表示“低电平有效”,“○”在输出端表示取反。

结合通过上面的分析,对“非逻辑”符号的识别与应用方法总结如下:

(1)在逻辑运算以及逻辑电路图中,“○”和“-”均表示“取非”或“取反”的意思。

(2)在各种数字电路的使能端口,表示低电平使能。

(3)在触发器的输出端,表示反相输出。

(4)在触发器的触发端,若带有三角形符号则表示下跳边沿触发;若没有三角形符号则表示电平触发。

(5)在仿真软件中,用“~”表示“逻辑非”。

在上述几种情况中,不管标有“○”,还是标有“-”,或者两个符号同时标注,都表示的是同一个意思。在触发器的反相输出端口,标有“○”,或者标有“-”,或者两个符号同时标注,或者两者均不标注,此位置还是反相输出端口。